Documentos de Académico

Documentos de Profesional

Documentos de Cultura

5to-6to Jfet Mosfet PDF

Cargado por

krisTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

5to-6to Jfet Mosfet PDF

Cargado por

krisCopyright:

Formatos disponibles

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRONICA

ESCUELA DE INGENIERIA ELECTRONICA

LABORATORIO DE DISPOSITIVOS ELECTRONICOS

TEMA:

LABORATORIO DE DISPOSITIVOS ELECTRONICOS

TRANSISTOR JFET-MOSFET

I.

Objetivos:

a. Disear, comprobar, simular y calcular el funcionamiento de los siguientes circuitos de

polarizacin con el transistor JFET y MOSFET.

b. Experimentar circuitos de polarizacin del JFET

c. Experimentar circuitos de polarizacin del MOSFET

d. Observar sus diferencias en la implementacin de un circuito.

II.

Fundamento terico

En los transistores bipolares, una pequea corriente de entrada (corriente de base) controla la

corriente de salida (corriente de colector); en los casos de los FET, es un pequeo voltaje de entrada

que controla la corriente de salida.

La corriente que circula en la entrada es generalmente despreciable (menos de un pico amperio).

Esto es una gran ventaja, cuando la seal proviene de un dispositivo tal como un micrfono de

condensador o un transductor piezo elctrico, los cuales proporcionan corrientes insignificantes.

Los FETs, bsicamente son de dos tipos:

El transistor de efecto de campo de Juntura o JFET.

El transistor de efecto de campo con compuerta aislada o IGFET, tambin conocido como

semiconductor de xido de metal, MOS, o simplemente MOSFET.

EL JFET

El JFET est constituido por una barra de silicio tipo N o canal N, introducido en una barra o anillo de

silicio tipo P tal como se muestra en la Fig. A

Los terminales del canal N son denominados SURTIDOR (SOURCE) y DRENADOR (DRAIN). El

anillo forma el tercer terminal del JFET llamado COMPUERTA (GATE).

Inicialmente circula una corriente por la compuerta, pero posteriormente la corriente circula

nicamente desde el surtidor al Drenador sin cruzar la juntura PN.

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRONICA

ESCUELA DE INGENIERIA ELECTRONICA

El control de esta corriente se efecta por medio de la aplicacin de un voltaje de polarizacin

inverso, aplicado entre la compuerta y el surtidor (VGS), formando un campo elctrico el cual limita

el paso de la corriente a travs del canal N (Fig.B). Al aumentar el voltaje inverso, aplicado a la

compuerta, aumenta el campo elctrico, y la corriente de Surtidor a Drenador disminuye.

Tambin se construyen JFETs con barra de silicio tipo P y anillos de silicio tipo N, denominndose

JFET canal P.

El voltaje aplicado entre el Drenador y el Surtidor (VDS), no debe sobrepasar el voltaje de ruptura

(tpicamente 50V) porque destruira el dispositivo.

Si se aplica polarizacin directa a la compuerta, circular una alta corriente por la compuerta que

puede destruir el JFET si no est limitada por una resistencia en serie con la compuerta.

Para comprar un JFET se debe indicar su cdigo.

PRUEBA DEL JFET

Se comprueba con un ohmmetro en la escala de Rx1 Rx10.

Entre compuerta y surtidor o compuerta y Drenador debe marcar como si fuera un diodo de silicio;

es decir alta resistencia en un sentido y baja en el inverso.

Entre Drenador y surtidor, el valor hmico exclusivamente del material del canal. Su valor vara entre

2K y 10K, siendo el mismo en ambos sentidos.

III.

Materiales

Fuente de voltaje ajustables de 0 a 15 V.

Un multitester digital o analgico

Un JFET K373

Resistores W: de 1M , 6.8M, 2.2K, 470, 3.3K, 10M.

Capacitores varios 10uF, 100uF y 10Nf

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRONICA

ESCUELA DE INGENIERIA ELECTRONICA

IV.

Circuito e implementacin:

a. Determine Id y Vgs para el JFET con polarizacin mediante divisor de voltaje

dado que para este JFET particular los valores de parmetro son tales que Vd

= 7V

b. Cul es el voltaje de salida total para el amplificador sin carga de la figura?

Idss es de 4.3mA; Vgs(corte) es de -2.7V

Determine Vgs y Vds para el circuito E-MOSFET en la figura. Considere que

este MOSFET particular tiene valores mnimos de Id(encendido)= 200mA con

Vgs = 4V y Vgs(umbral) = 2V

UNIVERSIDAD NACIONAL DEL CALLAO

FACULTAD DE INGENIERIA ELECTRICA Y ELECTRONICA

ESCUELA DE INGENIERIA ELECTRONICA

Determine el voltaje de drenaje a fuente en el circuito de la figura. La hoja de

datos de MOSFET da Vgs(apagado)= -8V e Idss = 12mA

V.

Resultados:

TABLAS:

Experimental

Terico

Id

Vgs

VI.

Conclusiones

También podría gustarte

- Animales MarinosDocumento6 páginasAnimales MarinosGera Treyry100% (1)

- José Morón - Señales y SistemasDocumento428 páginasJosé Morón - Señales y Sistemasreyes100% (8)

- Ebook Comer Sano Sin ExcusasDocumento23 páginasEbook Comer Sano Sin ExcusasAma PauAún no hay calificaciones

- Relatos Eroticos Tomo 9Documento157 páginasRelatos Eroticos Tomo 9Alejandro MujicaAún no hay calificaciones

- Lecturas de Comprensión 1.6 PDFDocumento17 páginasLecturas de Comprensión 1.6 PDFNancy Perez ParraAún no hay calificaciones

- Proyecto Plan de NegociosDocumento24 páginasProyecto Plan de NegocioskrisAún no hay calificaciones

- OsciloscopioDocumento108 páginasOsciloscopioxxxdanielsss100% (6)

- El Club de Los 27Documento25 páginasEl Club de Los 27Melissa MendezAún no hay calificaciones

- 2 Localización EspacialDocumento44 páginas2 Localización EspacialkrisAún no hay calificaciones

- Tensiometro Adc PDFDocumento9 páginasTensiometro Adc PDFkrisAún no hay calificaciones

- Um102 Es PDFDocumento22 páginasUm102 Es PDFkrisAún no hay calificaciones

- Trabajo Final de Etica Pativilca-1Documento9 páginasTrabajo Final de Etica Pativilca-1krisAún no hay calificaciones

- S02.s1 Material 1Documento34 páginasS02.s1 Material 1Estefany OrtegaAún no hay calificaciones

- Um102 Es PDFDocumento22 páginasUm102 Es PDFkrisAún no hay calificaciones

- Capítulo 6 - Cont - Adap - Modelo - ReferenciaDocumento17 páginasCapítulo 6 - Cont - Adap - Modelo - ReferenciaFreddy Galileo Vega AcostupaAún no hay calificaciones

- Cap5 Linealiza RealimentaDocumento21 páginasCap5 Linealiza RealimentaJeshu I. MendozaAún no hay calificaciones

- PDFDocumento57 páginasPDFkrisAún no hay calificaciones

- TIME SCHDocumento1 páginaTIME SCHkrisAún no hay calificaciones

- Unidad 01Documento14 páginasUnidad 01krisAún no hay calificaciones

- Unidad 02Documento14 páginasUnidad 02krisAún no hay calificaciones

- 1 Introduccion Robotica PDFDocumento50 páginas1 Introduccion Robotica PDFkrisAún no hay calificaciones

- Previo 1Documento3 páginasPrevio 1krisAún no hay calificaciones

- Tutorial Serie de Fourier Con MatlabDocumento8 páginasTutorial Serie de Fourier Con MatlabPilar BernalAún no hay calificaciones

- Guia 4Documento12 páginasGuia 4daixdergoAún no hay calificaciones

- DecibeliosDocumento9 páginasDecibelioskleberfranco1Aún no hay calificaciones

- Lab1 Cont AvanzadoDocumento3 páginasLab1 Cont Avanzadocorreovideos10Aún no hay calificaciones

- Previo 2Documento7 páginasPrevio 2krisAún no hay calificaciones

- Cuadra DaDocumento49 páginasCuadra Da7ZETA7Aún no hay calificaciones

- Iniciacion VVDDocumento46 páginasIniciacion VVDsuarezgiovanny050406Aún no hay calificaciones

- Generadores de Ondas SenoidalesDocumento21 páginasGeneradores de Ondas SenoidalesCarls Guiovani Guirrardelli VegaAún no hay calificaciones

- Control de Un Motor Paso A Paso PIC PDFDocumento125 páginasControl de Un Motor Paso A Paso PIC PDFjulio gamboaAún no hay calificaciones

- TransformadoresDocumento68 páginasTransformadoresRolando DalenzAún no hay calificaciones

- Generadores D OmdaDocumento10 páginasGeneradores D OmdaMisuka MeiAún no hay calificaciones

- Cuestionario 33800Documento2 páginasCuestionario 33800Geancarlo AndreAún no hay calificaciones

- Oracle IntroduccionDocumento62 páginasOracle IntroduccionAdrian Samaniego AlejoAún no hay calificaciones

- Fuerzas Magnéticas para Tercer Grado de SecundariaDocumento5 páginasFuerzas Magnéticas para Tercer Grado de SecundariaOscar Edgar NinaAún no hay calificaciones

- 4 Consejos para Educar y Adiestrar A Un Perro de Raza AkitaDocumento4 páginas4 Consejos para Educar y Adiestrar A Un Perro de Raza AkitaEstelaMarin100% (1)

- Lectura 1Documento3 páginasLectura 1NATY MORALESAún no hay calificaciones

- DiscursoDocumento1 páginaDiscursocristian7epnAún no hay calificaciones

- Monodia Cristiana Medieval - #1 Misa para El Día de NavidadDocumento8 páginasMonodia Cristiana Medieval - #1 Misa para El Día de NavidadPepeAún no hay calificaciones

- Rendimientos de Obra JornalDocumento7 páginasRendimientos de Obra JornalJUAN DIEGO CASALLAS BOBADILLAAún no hay calificaciones

- Teoria para Licencia de ConducirDocumento3 páginasTeoria para Licencia de ConducirMARIACIFERNANDEZAún no hay calificaciones

- Atole de Maiz FermentadoDocumento1 páginaAtole de Maiz FermentadoSofia Alejandra Garcia GonzalezAún no hay calificaciones

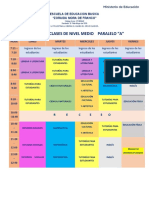

- Horarios 2022-2023Documento1 páginaHorarios 2022-2023Gabriel FarezAún no hay calificaciones

- Relacion 4Documento2 páginasRelacion 4danielAún no hay calificaciones

- Interelacion de FormasDocumento50 páginasInterelacion de FormasmartinAún no hay calificaciones

- Carpeta de Recuperacion - Arte y Cultura 1º de SecundariaDocumento8 páginasCarpeta de Recuperacion - Arte y Cultura 1º de SecundariaPamela Beatriz100% (1)

- El Verdugo. Carmen, Iris, Ruth y Hugo 2BachADocumento3 páginasEl Verdugo. Carmen, Iris, Ruth y Hugo 2BachACarmen NavarreteAún no hay calificaciones

- Guia de Ejercicios RectaDocumento3 páginasGuia de Ejercicios RectaDaniel EffioAún no hay calificaciones

- 5 Ejercicios de Visualización Creativa para Tu AutoestimaDocumento5 páginas5 Ejercicios de Visualización Creativa para Tu AutoestimaLeidy Johana Sanchez OlayaAún no hay calificaciones

- Analisis Hotizontal y VerticalDocumento22 páginasAnalisis Hotizontal y VerticalMichu VelezAún no hay calificaciones

- Cronica de ViajeDocumento1 páginaCronica de ViajeanghelaAún no hay calificaciones

- S17.s1-ENTREGA FINALDocumento18 páginasS17.s1-ENTREGA FINALLeo Loud QuispeAún no hay calificaciones

- Lista Con Los Instrumentos Musicales de La Antigua Grecia - ¡Resumen!Documento1 páginaLista Con Los Instrumentos Musicales de La Antigua Grecia - ¡Resumen!luis moronAún no hay calificaciones

- Fundamentos Tecnicos de El FutbolDocumento9 páginasFundamentos Tecnicos de El Futbolesther riveraAún no hay calificaciones

- Vida Saludable y Deporte - Evidencia Et 4Documento9 páginasVida Saludable y Deporte - Evidencia Et 4kate guadalupeAún no hay calificaciones

- AsdDocumento20 páginasAsdPaulAún no hay calificaciones

- Ordena Las Letras D P M R B-VDocumento56 páginasOrdena Las Letras D P M R B-Varcangelblanco2014Aún no hay calificaciones

- El Silencio de San JoséDocumento13 páginasEl Silencio de San JoséSor Maria Ysabel Gauret Novoa100% (3)

- Simbología de RedesDocumento4 páginasSimbología de Redeshjuarezv50% (2)