Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Lenguaje VHDL

Cargado por

Enrique GarcíaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Lenguaje VHDL

Cargado por

Enrique GarcíaCopyright:

Formatos disponibles

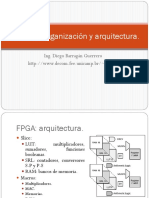

VHDL: SU ORGANIZACIN Y ARQUITECTURA

Tal como lo indican sus siglas, VHDL (Hardware Description Language) es un lenguaje

orientado a la descripcin o modelado de sistemas digitales; es decir, se trata de un

lenguaje mediante el cual se puede describir, analizar y evaluar el comportamiento de un

sistema electrnico digital. VHDL es un lenguaje poderoso que permite la integracin de

sistemas digitales sencillos, elaborados o ambos en un dispositivo lgico programable,

sea de baja capacidad de integracin como un GAL, o de mayor capacidad como los

CPLD y FPGA. La estructura general de un programa en VHDL est formada por mdulos

o unidades de diseo, cada uno de ellos compuesto por un conjunto de declaraciones e

instrucciones que definen, describen, estructuran, analizan y evalan el comportamiento

de un sistema digital.

Existen cinco tipos de unidades de diseo en VHDL: declaracin de entidad (entity

declaration), arquitectura (architecture), configuracin (configuration), declaracin del

paquete (package declaration) y cuerpo del paquete (package body). En el desarrollo de

programas en VHDL pueden utilizarse o no tres de los cinco mdulos, pero dos de ellos

(entidad y arquitectura) son indispensables en la estructuracin de un programa. Las

declaraciones de entidad, paquete y configuracin se consideran unidades de diseo

primarias, mientras que la arquitectura y el cuerpo del paquete son unidades de diseo

secundarias porque dependen de una entidad primaria que se debe analizar antes que

ellas.

1. La Entidad: (entity) es el bloque elemental de diseo en VHDL, las entidades son

todos los elementos electrnicos (sumadores, contadores, compuertas, flip-flops,

memorias, multiplexores, etc.) que forman de manera individual o en conjunto un sistema

digital. La entidad puede representarse de muy diversas maneras; por ejemplo, la figura

se muestra la arquitectura de un sumador completo a nivel de compuertas; ahora bien,

esta entidad se puede

representar a nivel de sistema indicando tan slo las entradas (Cin, A y B) y salidas

(SUMA y Cout) del circuito.

Declaracin de la entidad de un circuito sumador

entity sumador is

port (A, B, Cin: in bit;

SUMA, Cout: out bit);

end sumador;

2. Arquitectura: Una arquitectura (architecture) se define como la estructura que describe

el funcionamiento de una entidad, de tal forma que permita el desarrollo de los

procedimientos que se llevarn a cabo con el fin de que la entidad cumpla las condiciones

de funcionamiento deseadas. La gran ventaja que presenta VHDL para definir una

arquitectura radica en la manera en que pueden describirse los diseos; es decir,

mediante el algoritmo de programacin empleado se puede describir desde el nivel de

compuertas hasta sistemas complejos.

De manera general, los estilos de programacin utilizados en el diseo de arquitecturas

se clasifican como:

Estilo funcional

Estilo por flujo de datos

Estilo estructural

El nombre asignado a estos estilos no es importante, ya que es tarea del diseador

escribir el comportamiento de un circuito utilizando uno u otro estilo que a su juicio le sea

el ms acertado.

2.1 Descripcin funcional:

En la figura se describe funcionalmente el circuito comparador. Se trata de una

descripcin funcional porque expone la forma en que trabaja el sistema; es decir, las

descripciones consideran la relacin que hay entre las entradas y las salidas del circuito,

sin importar cmo est organizado en su interior.

Para este caso:

El cdigo que representa el circuito de la figura se muestra en el siguiente listado:

-- Ejemplo de una descripcin funcional

library ieee;

use ieee.std_logic_1164.all;

entity comp is

port (a,b: in bit_vector( 1 downto 0);

c: out bit);

end comp;

architecture funcional of comp is

begin

process (a,b)

begin

if a = b then

c <='1';

else

c<='0';

end if;

end process;

end funcional;

Ejercicio: Describa mediante declaraciones del tipo if-then-else el funcionamiento de la

compuerta OR.

2.2 Descripcin por Flujo de Datos:

La descripcin por flujo datos indica la forma en que los datos se pueden transferir de una

seal a otra sin necesidad de declaraciones secuenciales (if-then-else). Este tipo de

descripciones permite definir el flujo que tomarn los datos entre mdulos encargados de

realizar operaciones. En este tipo de descripcin se pueden utilizar dos formatos:

mediante instrucciones when else (cuando- si no) o por medio de ecuaciones

booleanas.

a) Descripcin por flujo de datos mediante when-else.

A continuacin se muestra el cdigo del comparador de igualdad de dos bits descrito

antes. Ntese que la diferencia entre el listado anterior y el actual radica en la eliminacin

del proceso y en la descripcin sin declaraciones secuenciales (if-then-else).

--Ejemplo de declaracin de la entidad de un comparador

library ieee;

use ieee.std_logic_1164.all ;

entity comp is

port (a,b: in bit_vector (1 downto 0);

c: out bit);

end comp;

architecture f_datos of comp is

begin

c <= '1' when (a = b) else '0'; (asigna a C el valor

de 1 cuando a=b si no vale 0).

end f_datos;

En VHDL se manejan dos tipos de declaraciones: secuenciales y concurrentes. Una

declaracin secuencial de la forma if-then-else se halla en el listado anterior dentro del

proceso, donde su ejecucin debe seguir un orden para evitar la prdida de la lgica

descrita. En cambio, en una declaracin concurrente esto no es necesario, ya que no

importa el orden en que se ejecutan.Tal es el caso del listado actual.

b) Descripcin por flujo de datos mediante ecuaciones booleanas:

Otra forma de describir el circuito comparador de dos bits es mediante la obtencin de sus

ecuaciones booleanas. En el siguiente listado se observa este desarrollo.

El interior del circuito comparador de la figura puede representarse por medio de

compuertas bsicas y este circuito puede describirse mediante la obtencin de sus

ecuaciones booleanas.

-- Ejemplo de declaracin de la entidad de un comparador

library ieee;

use ieee.std_logic_1164.all;

entity comp is

port ( a,b: in bit_vector (1 downto 0) ;

c: out bit) ;

end comp;

architecture booleana of comp is

begin

c <= (a(1) xnor b(l) and a(0) xnor b(0)) ;

end booleana;

La forma de flujo de datos en cualquiera de sus representaciones describe el camino que

los datos siguen al ser transferidos de las operaciones efectuadas entre las entradas a y b

a la seal de salida c.

También podría gustarte

- Uf0319 Sistema Operativo, Internet y Correo-E.Documento36 páginasUf0319 Sistema Operativo, Internet y Correo-E.Maripi Del CidAún no hay calificaciones

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Aún no hay calificaciones

- 101 Secretos Hardware Users PDFDocumento356 páginas101 Secretos Hardware Users PDFFredy Alexander Tellez ArizaAún no hay calificaciones

- Uso de Verilog HDLDocumento95 páginasUso de Verilog HDLFelix HeinzAún no hay calificaciones

- Introduccion HDL y VerilogDocumento81 páginasIntroduccion HDL y VerilogPedro Ruiz DiazAún no hay calificaciones

- Programacion de Sistemas Digitales Con VHDLDocumento35 páginasProgramacion de Sistemas Digitales Con VHDLNicolas CastilloAún no hay calificaciones

- VHDLDocumento34 páginasVHDLAnel VallarinoAún no hay calificaciones

- ELECTRODocumento9 páginasELECTROpathy cocreAún no hay calificaciones

- 06 Sistemas Digitales Mum 130605Documento13 páginas06 Sistemas Digitales Mum 130605Gabriel JDAún no hay calificaciones

- Curso VHDLDocumento8 páginasCurso VHDLHumberto Lloclle DelgadoAún no hay calificaciones

- VHDL Organización y ArquitecturaDocumento23 páginasVHDL Organización y ArquitecturaLuis SantiagoAún no hay calificaciones

- Cap. 2 VHDLDocumento19 páginasCap. 2 VHDLveronicaAún no hay calificaciones

- Estudio VHDLDocumento29 páginasEstudio VHDLTsubasa GarcíaAún no hay calificaciones

- U6 de DISEÑO DIGITAL 2021 ElectronicaDocumento17 páginasU6 de DISEÑO DIGITAL 2021 ElectronicaJuan alberto Martinez torresAún no hay calificaciones

- VHDL Programacion de Sistemas Digitales U!Documento31 páginasVHDL Programacion de Sistemas Digitales U!L Adolfo AlvarezAún no hay calificaciones

- Formas de Describir Un Circuito VHDLDocumento14 páginasFormas de Describir Un Circuito VHDLnorbeyjAún no hay calificaciones

- Lógica Programable - Parte - 2 - ArquitecturaDocumento17 páginasLógica Programable - Parte - 2 - ArquitecturaOliverth EnriqueAún no hay calificaciones

- Introduccion Al Lenguaje VHDLDocumento21 páginasIntroduccion Al Lenguaje VHDLLucho PortuanoAún no hay calificaciones

- VHDLDocumento53 páginasVHDLDaniel CadenaAún no hay calificaciones

- Introduccion VHDLDocumento16 páginasIntroduccion VHDLCarmen CarrionAún no hay calificaciones

- Aplicación de Los Estilos de Descripción en VHDLDocumento7 páginasAplicación de Los Estilos de Descripción en VHDLDiego Andres ParadaAún no hay calificaciones

- Arquitectura y Estructura de VHDLDocumento7 páginasArquitectura y Estructura de VHDLVictor ManuelAún no hay calificaciones

- Asm en VHDLDocumento6 páginasAsm en VHDLotoAún no hay calificaciones

- LIBRO Programacionconvhdl BuenoDocumento25 páginasLIBRO Programacionconvhdl BuenoTomas Sanchez TronoAún no hay calificaciones

- Contador 00 A 99 VHDLDocumento3 páginasContador 00 A 99 VHDLFabian UgarteAún no hay calificaciones

- 4.2.1 Por Captura Esquemática: 4.2.2 Por Tabla de VerdadDocumento5 páginas4.2.1 Por Captura Esquemática: 4.2.2 Por Tabla de VerdaddwdAún no hay calificaciones

- Programacion de Circuitos Combinacionales Con HDLDocumento19 páginasProgramacion de Circuitos Combinacionales Con HDLTaz Hernandez DeAún no hay calificaciones

- Estilos de Programación en VHDLDocumento5 páginasEstilos de Programación en VHDLCARLOS ENRIQUE URETA BELTRANAún no hay calificaciones

- Guia Laboratorio No 3 Introduccion A VHDLDocumento8 páginasGuia Laboratorio No 3 Introduccion A VHDLStellaAún no hay calificaciones

- VHDL Su Organizacion y ArquitecturaDocumento20 páginasVHDL Su Organizacion y ArquitecturaTonaspiuckAún no hay calificaciones

- Diseño VHDL (Organizacion Y Arquitectura)Documento57 páginasDiseño VHDL (Organizacion Y Arquitectura)ENIC-AITCG0% (1)

- ALUDocumento26 páginasALUChuck PorcalloAún no hay calificaciones

- Flujo de Diseño en VHDLDocumento26 páginasFlujo de Diseño en VHDLRodolfo AlcantaraAún no hay calificaciones

- P4 - Introducción A Programación VHDLDocumento43 páginasP4 - Introducción A Programación VHDLReséndiz Nieto Melanie GabrielaAún no hay calificaciones

- Programacion VHDL Con (PLD)Documento61 páginasProgramacion VHDL Con (PLD)Luis Fernando BravoAún no hay calificaciones

- VHDL BasicoDocumento64 páginasVHDL BasicoQuetzal Cortés50% (2)

- SD1 PR2 Introduccion VHDL 2023-1Documento27 páginasSD1 PR2 Introduccion VHDL 2023-1Antonio MuroAún no hay calificaciones

- Lenguaje Descripción de Hardware: VHDL: GeneralidadesDocumento23 páginasLenguaje Descripción de Hardware: VHDL: GeneralidadesErick Alejandro Galicia CastañedaAún no hay calificaciones

- VHDL SentenciasDocumento6 páginasVHDL SentenciasAlexis PeñalozaAún no hay calificaciones

- Programacion de Circuitos Combinacionales Con HDLDocumento11 páginasProgramacion de Circuitos Combinacionales Con HDLTaz Hernandez De0% (2)

- VHDLDocumento24 páginasVHDLJorge RamirezAún no hay calificaciones

- VHDLDocumento5 páginasVHDLJorge Alberto Salomon MedinaAún no hay calificaciones

- Verilog PracticasDocumento100 páginasVerilog Practicasivanvargas19100% (1)

- Lenguajes de Descripción de Hardware (HDL)Documento34 páginasLenguajes de Descripción de Hardware (HDL)Arturo72Aún no hay calificaciones

- Unidad 2Documento7 páginasUnidad 2Gustavo RodriguezAún no hay calificaciones

- Laboratorio#3 SumadorcompletoDocumento4 páginasLaboratorio#3 SumadorcompletoFernando GuiraudAún no hay calificaciones

- Reglas Básicas de Programación en VHDLDocumento4 páginasReglas Básicas de Programación en VHDLCesar David Arango OsorioAún no hay calificaciones

- Tutorial de VHDLDocumento27 páginasTutorial de VHDLPablo Mamani CruzAún no hay calificaciones

- Programacion VHDL Con PLD PDFDocumento61 páginasProgramacion VHDL Con PLD PDFMtzAún no hay calificaciones

- T300 Capítulo 06 - SirveDocumento15 páginasT300 Capítulo 06 - SirveFormat_CAún no hay calificaciones

- Cuestionario 1 y 2. El Arte de Programar en Sistemas DigitalesDocumento9 páginasCuestionario 1 y 2. El Arte de Programar en Sistemas DigitalesFabiana GutiérrezAún no hay calificaciones

- Compuertas y VHDLDocumento8 páginasCompuertas y VHDLLuis LoayzaAún no hay calificaciones

- Nuevo Documento de Microsoft WordDocumento11 páginasNuevo Documento de Microsoft WordIsrael Nicolas Linares ToroAún no hay calificaciones

- Lenguaje HDLDocumento4 páginasLenguaje HDLIsacar Vela100% (1)

- Estilo de Descripción Estructural en VHDLDocumento13 páginasEstilo de Descripción Estructural en VHDLJorge Beniez CAún no hay calificaciones

- Arquitectura EstructuralDocumento4 páginasArquitectura EstructuralJuan Manuel DávilaAún no hay calificaciones

- Taller de DigitalesDocumento8 páginasTaller de DigitalesDavid BlanchardAún no hay calificaciones

- Practica 6Documento12 páginasPractica 6hector blancoAún no hay calificaciones

- Sistemas DigitalesDocumento24 páginasSistemas DigitalesHugo ETAún no hay calificaciones

- FGL029 Guia No 2 Arquitecturas VHDLDocumento13 páginasFGL029 Guia No 2 Arquitecturas VHDLAlbeiroFernandezSanchezAún no hay calificaciones

- Despliegue y puesta en funcionamiento de componentes software. IFCT0609De EverandDespliegue y puesta en funcionamiento de componentes software. IFCT0609Aún no hay calificaciones

- Cal Culo Select RicosDocumento4 páginasCal Culo Select Ricosqwerty1280Aún no hay calificaciones

- Datasheet Panel Solar INTI 250w.Documento2 páginasDatasheet Panel Solar INTI 250w.Enrique García100% (1)

- EcoDocumento14 páginasEcoAlirio MejiasAún no hay calificaciones

- Elaboracion Del Plano EléctricoDocumento4 páginasElaboracion Del Plano EléctricoMariaMonicaAún no hay calificaciones

- Tutorial Descarga XilinxDocumento22 páginasTutorial Descarga XilinxYoee ChuquiihuancaAún no hay calificaciones

- Led de Alumbrado Publico de 30w A 80wDocumento16 páginasLed de Alumbrado Publico de 30w A 80wEnrique GarcíaAún no hay calificaciones

- Control de Angulo TiristoresDocumento10 páginasControl de Angulo TiristoresBoris Barzallo0% (1)

- Tema5 Inf2207 Modos de DireccionamientoDocumento14 páginasTema5 Inf2207 Modos de DireccionamientoMarcos HernandezAún no hay calificaciones

- AnTeNaSt3 PDFDocumento38 páginasAnTeNaSt3 PDF201208071993Aún no hay calificaciones

- Tema - 3 - Pds Transformada Z PDFDocumento18 páginasTema - 3 - Pds Transformada Z PDFAlberto DiazAún no hay calificaciones

- Ventajas de Tener La Conciencia DespiertaDocumento10 páginasVentajas de Tener La Conciencia DespiertaEnrique GarcíaAún no hay calificaciones

- Manual Fx-570ES SPDocumento78 páginasManual Fx-570ES SPEnrique GarcíaAún no hay calificaciones

- 3-2 Circuitos DisparoDocumento28 páginas3-2 Circuitos DisparoAdrian BedollaAún no hay calificaciones

- Lab3 Control Digital 2014 IIDocumento1 páginaLab3 Control Digital 2014 IIEnrique GarcíaAún no hay calificaciones

- Ejercicios de SuperposicionDocumento2 páginasEjercicios de SuperposicionEnrique GarcíaAún no hay calificaciones

- Control Motor CA PDFDocumento74 páginasControl Motor CA PDFEnrique GarcíaAún no hay calificaciones

- Funciones FourierDocumento12 páginasFunciones FourierNéstor BernalAún no hay calificaciones

- Casos Practicos Newsletter PDFDocumento506 páginasCasos Practicos Newsletter PDFEnrique GarcíaAún no hay calificaciones

- Crecimiento EpitaxialDocumento26 páginasCrecimiento EpitaxialEnrique GarcíaAún no hay calificaciones

- 03 SemiconductoresDocumento3 páginas03 SemiconductoresrusokAún no hay calificaciones

- DiodosDocumento21 páginasDiodosDiego LlalauAún no hay calificaciones

- Actividad 4Documento5 páginasActividad 4Samuel Eduardo Emperador ContrerasAún no hay calificaciones

- Administracion Del ProcesadorDocumento4 páginasAdministracion Del ProcesadorVictor Hugo Morales0% (1)

- Ud2 Practica DCHP WindowsDocumento2 páginasUd2 Practica DCHP WindowsJAVIER MARTÍNEZ SÁNCHEZAún no hay calificaciones

- Practica 06 - Programacion de HMI UNACDocumento10 páginasPractica 06 - Programacion de HMI UNACMarco SantiagoAún no hay calificaciones

- Componentes de Un DBMSDocumento36 páginasComponentes de Un DBMSAnatoli Quimper100% (1)

- Conceptos Básicos de ElectrónicaDocumento1 páginaConceptos Básicos de ElectrónicaJosé Alfredo Guzmán GonzálezAún no hay calificaciones

- Ejecicio Tipo Examen 3Documento3 páginasEjecicio Tipo Examen 3oriminnotAún no hay calificaciones

- Pic SustitutoDocumento34 páginasPic Sustitutomarquitos550bAún no hay calificaciones

- Modelo 1 A 1 - Elgueta Ramírez.Documento3 páginasModelo 1 A 1 - Elgueta Ramírez.Ananda Cronopio De Las MercedesAún no hay calificaciones

- Trucos para PPC (Muy InteresanteDocumento48 páginasTrucos para PPC (Muy Interesanteapi-3730532100% (1)

- Leer y Escribir en Particiones EXT4 en WindowsDocumento8 páginasLeer y Escribir en Particiones EXT4 en WindowsantornioAún no hay calificaciones

- Tipos de DatosDocumento4 páginasTipos de DatosDavid EstuardoAún no hay calificaciones

- Lab 4Documento11 páginasLab 4arancbasAún no hay calificaciones

- Unidad 3,4 EnsambladorDocumento13 páginasUnidad 3,4 EnsambladorPérez Oso100% (1)

- MMQDocumento24 páginasMMQRodrigo CastilloAún no hay calificaciones

- Vixtrun Tarea GraficaDocumento9 páginasVixtrun Tarea GraficaNicolas PovedaAún no hay calificaciones

- ELK StackDocumento392 páginasELK StackanchumagicAún no hay calificaciones

- Sistemas Gestores de Bases de DatosDocumento3 páginasSistemas Gestores de Bases de DatosAlejandra GarciaAún no hay calificaciones

- Drivers o ControladoresDocumento2 páginasDrivers o ControladoresLidia OrellanaAún no hay calificaciones

- Símbolos de Diagramas de FlujoDocumento6 páginasSímbolos de Diagramas de FlujoDerek DavidsonAún no hay calificaciones

- Material de Reforzamiento U9 TAREA RESUELTADocumento8 páginasMaterial de Reforzamiento U9 TAREA RESUELTAFrank DíazAún no hay calificaciones

- Actividad 5Documento6 páginasActividad 5AbrekAún no hay calificaciones

- Practica Ejercicios Ruteo EstaticoDocumento3 páginasPractica Ejercicios Ruteo EstaticoluisAún no hay calificaciones

- Squid CacheDocumento24 páginasSquid CacheAlexis Diaz del RiscoAún no hay calificaciones

- Actividad 2 - Instalacion - SoftwareDocumento21 páginasActividad 2 - Instalacion - SoftwareBryan BetancourthAún no hay calificaciones

- Resumen de Las Clases de ComputaciónDocumento12 páginasResumen de Las Clases de ComputaciónmarcelomorenodAún no hay calificaciones

- Interrupciones en Los MicrocontroladoresDocumento4 páginasInterrupciones en Los MicrocontroladoresNathalí MoreiraAún no hay calificaciones

- Vocabulario Básico en Inglés Que Debes ConocerDocumento7 páginasVocabulario Básico en Inglés Que Debes ConocerElvira VLAún no hay calificaciones