Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe Z80

Cargado por

Bry Ruiz Mendez0 calificaciones0% encontró este documento útil (0 votos)

84 vistas15 páginasTítulo original

INFORME Z80

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOC, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

84 vistas15 páginasInforme Z80

Cargado por

Bry Ruiz MendezCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 15

Microprocesador Z80

TEMA: MICROPROCESADOR Z80

OBJETIVO GENERAL

Disear un sistema bsico con un microprocesador de 8 bits utiliando el

microprocesador Z80!

OBJETIVOS ESPECFICOS

Analiar la estructura del microprocesador" las memorias # de los

puertos E$S en el datas%eet!

Estudiar cada elemento &ue compone el sistema!

Conectar es&uemticamente los elementos del sistema!

MARCO TERICO

Estudio del Microroces!dor: "P#$%

&ESCRIPCIN GENERAL

El Zilo' Z80 (Z80) es un microprocesador de 8 bits" mane*a instrucciones de

+, bits # puede direccionar %asta ,- .b de RAM! Su ar&uitectura se

encuentra a medio camino entre la or'aniaci/n de acumulador # de

re'istros de prop/sito 'eneral! Si consideramos al Z80 como procesador de

ar&uitectura de re'istros 'enerales" se sit0a dentro del tipo de re'istro1

memoria!

CARACTERSTICAS GENERALES

2us de datos de 8 bits

2us de direcciones de +, bits

En total +8 re'istros de 8 bits # - de +, bits

+3 re'istros de 8 bits &ue se pueden usar en pares para 4ormar , de

+, bits

Cloc5 de - M6

El set de instrucciones contiene +78 instrucciones!

El e8tenso set de instrucciones inclu#e operaciones con palabras" bit"

b#te # cadena de caracteres!

Set duplicado de re'istros de banderas # de prop/sito 'eneral!

Dos re'istros 9ndices de +, bits!

Contador de re4resco de memoria dinmica!

2a*o consumo de ener'9a

: -0mA ;ipo (7<" +0M6 en el modo R=>)

: 3mA ;ipo (7<" +0M6 en modo ID?E+)

: +0mA ;ipo (7<" +0M6 en modo ID?E3)

: 7uA ;ipo (7< en el modo S;OP)

: DC a +0M6 operaci/n (7< @ +0A)

=na 4uente de alimentaci/n de 7< (7< @ +0A)

;emperatura de 4uncionamiento (0BC a C0BC)

Potente 4unci/n de interrupci/n

+0 modos de direccionamiento

CICLOS &E MA'(INA ) CICLOS &E INSTR(CCION

+

Microprocesador Z80

Se denomina DM+D al ciclo de m&uina correspondiente a la b0s&ueda del

c/di'o de operaci/n" durante el cual" la pata M+ del microprocesador se

coloca a niEel ba*o! El ciclo de m&uina M+ ocupa - ciclos de relo*F un ciclo

de relo* dura apro8imadamente 0!3G microse'undos (millonHsimas de

se'undo)" por lo &ue el ciclo M+ dura +!+- microse'undos!

=n ciclo de memoria es una operaci/n de lectura o escritura en memoria"

emplea I ciclos de relo*" # dura 0!8, microse'undos!

REGISTROS

?os re'istros constitu#en una especie de pe&uea memoria interna al

microprocesador! El Z180 tiene re'istros de 8 # +, bits" si bien los de 8 bits

se pueden a'rupar de 3 en 3 para 4ormar uno de +, bits! ;odas las

operaciones &ue realia el Z180 se %acen entre n0meros contenidos en los

re'istros" o bien" entre un re'istro # una posici/n de memoriaF por eso se

dice &ue el Z180 es un microprocesador orientado %acia los re'istros! ?a

posibilidad de a'rupar dos re'istros de 8 bits para 4ormar uno de +,"

permite al Z180 realiar operaciones de +, bits a pesar de ser un

microprocesador de 8 bits! El Z180 tiene" en total" +8 re'istros de 8 bits # -

re'istros de +, bits! Al'unos son de uso 'eneral # otros tienen asi'nadas

4unciones espec9Jcas!

Re*istros eseci!les de +, -its

?os cuatro re'istros especiales de +, bits sonK

Contador de pro'rama (pro'ram counter DpcD)

Puntero de pila (stac5 pointer DspD)

Re'istro 9ndice (inde8 8 e inde8 # Li8M e Li#M)

Re*istros eseci!les de $ -its

<EC;OR DE I>;ERR=PCIO> (Interrupt DID)

Re'istro de re'eneraci/n (re4res% DrD)

Re*istros !lter.!ti/os

Acumulador (acumulator DaD)

Re'istro de estado (Na's D4D)

Re'istros de uso 'eneral (DbD" DcD" DdD" DeD" D%D" DlD)

Re'istro de instrucciones

PINES &EL #0$%

3

Microprocesador Z80

$ l1.e!s de d!tos 2de.o"i.!d!s: de &% ! &34

+, de direccio.es 2de.o"i.!d!s: de A% ! A+546

7RESET: Es un pin de entradaF cuando se actiEa se resetea el

microprocesador" lo cual produce" entre otras acciones" &ue se car'ue

0000% en el contador de pro'rama!

7M+: Es un pin de salida" se actiEa cuando el microprocesador est

buscando el c/di'o de operaci/n de una instrucci/n!

7MRE': Es un pin de salida" se actiEa cuando el microprocesador est

accediendo a la memoria" #a sea en un ciclo de lectura o de escritura

7IOR': Es un pin de salida" se actiEa cuando el microprocesador est

accediendo a un dispositiEo de entrada$salida" #a sea en un ciclo de

lectura o de escritura!

7R&: Es un pin de salida" se actiEa cuando el microprocesador est

e*ecutando un ciclo m&uina de lecturaF #a sea lectura de memoria o

lectura de un dispositiEo de entrada$salida!

78R: Es un pin de salida" se actiEa cuando el microprocesador est

e*ecutando un ciclo m&uina de escrituraF #a sea escritura en memoria o

escritura en un dispositiEo de entrada$salida!

79ALT: Detener la seal Indica &ue la CP= %a e*ecutado una instrucci/n

de detener

7RFS9: Es un pin de salidaF el microprocesador lo actiEa en los 0ltimos

ciclos de relo* de todos los ciclos m&uina M+" para realiar el re4resco de

la memoria dinmica!

78AIT: Es un pin de entradaF &ue indica al microprocesador &ue la

operaci/n de memoria o entrada$salida &ue estaba realiando a0n no se

%a terminado por lo &ue debe incluir una serie de estados de espera

mientras &ue esta seal permaneca actiEa!

7INT: Seal de petici/n de interrupci/n enmascarable Interrupci/n es

'enerada por ?SI peri4Hrico! Esta seal ser aceptado si la %abilitaci/n de

interrupci/n del Nip1Nop (OI2) se J*a en D+D! $I>; es normalmente cable1O

# re&uiere una tracci/n e8terna para estas aplicaciones!

Co.sider!cio.es de Oer!ci:. Reco"e.d!d!

I

P!r;"etr

o

&escrici:. M1.i"o T1ic

o

M;<i"o

<cc Alimentaci/n -!7 < 7!0 < 7!7 <

P>D ;ierra 0!0 < 0!0 < 0!0 <

<I? Entrada de Eolta*e

ba*a

10!I < 0!0 < 0!8 <

<I6 Entrada de Eolta*e

alta

3!3 < 1 7 <

Microprocesador Z80

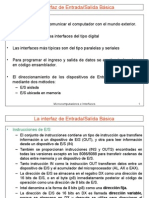

Puertos de co"u.ic!ci:.: #$%0PIO

A&APTA&OR &E P(ERTOS #$% PIO

&ESCRPCION GENERAL

El Z8O paralelo de I$O (PIO) es un circuito pro'ramable= el dispositiEo de

puerto dual &ue proporciona un inter4a ;;? compatible entre dispositiEos

peri4Hricos # la CP= Z80! >ote &ue los pa&uetes de QOP estn s/lo

disponibles en la Eersi/n CMOS! ?a CP= conJ'ura la Z8O1PIO para

interactuar con una amplia 'ama de dispositiEos peri4Hricos sin a*ena l/'ica

necesaria" t9picos dispositiEos peri4Hricos &ue son totalmente compatibles

con el Z801PIO inclu#en ma#or9a de los teclados" lectores de cinta de papel #

puetaos" las impresoras" los pro'ramadores de PROM" etc! Z8O1PIO se

empa&ueta en un DIP de -0 pines" o un P?CC de -- pines" o un POO de --

pines! >MOS # Eersiones CMOS estn tambiHn disponibles!

CARACTERISTICAS

Proporciona una inter4a directa entre el sistema de microcomputadora

Z80 # dispositiEos peri4Hricos!

Cuatro modos operatiEos pro'ramables salida" entrada" bidireccional

(solamente Port A)" # 2it de control!

Interrupciones pro'ramables sobre condiciones del estado de peri4Hricos

(+!7m< 1 +!7<)!

>MOS Eersi/n para soluciones de costo de 4uncionamiento sensible!

CMOS Eersi/n para los diseos &ue re&uieren alta Eelocidad # ba*o

consumo de ener'9a!

>MOS Z08-300-1-M6" Z08-300,1,!+CM%!

, M6 compatible con la Eersi/n ,!+-- M6 operaci/n del relo* de la CP=!

<olta*es en <cc con respecto a <ss (10!I< a RC!0<)

<olta*es en todas las entradas con respecto a <ss (10!I< a <ccR0!I<)

;emperatura de almacenamiento (1,7BC a R+70BC)

MO&OS &E TRABAJO

El Z80PIO traba*a en cuatro modos de traba*o!

MO&O %= + O >= 2e.tr!d!= s!lid! de l! se?!l= o -idireccio.!l4

-

T!-l!6 + <alores de

operaci/n Z80

Microprocesador Z80

Re&uiere &ue al menos uno" # %asta tres" palabras de control por puerto!

Estas palabras sonK

Modo de !l!-r! de co.trol6 Selecciona el modo de 4uncionamiento

del puerto! Esta palabra es necesaria # puede ser escrita en cual&uier

momento!

I.terruci:. de l! P!l!-r! de Vector6 El Z80 PIO est diseado para

utiliarse con la CP= Z80 en el modo de interrupci/n 3! Esta palabra

debe ser pro'ramada si las interrupciones se Ean a utiliar!

I.terruci:. de l! !l!-r! de co.trol o i.terru"ir &es@!-ilit!r

l! P!l!-r!: Controla el actiEar o desactiEar la 4unci/n de la PIO de

interrupci/n!

MO&O A 2co.trol de -its4!

Re&uiere al menos dos" # %asta cuatro de las palabras de control!

Modo de !l!-r! de co.trol! Selecciona el modo de 4uncionamiento

del puerto! Esta palabra es necesaria # puede ser escrita en cual&uier

momento!

I7O Re*istro !l!-r! de co.trol! Cuando se selecciona el modo I" el

Modo de Control de la Palabra debe ser se'uida por la E$S de control de

palabra! Esta palabra conJ'ura el I$O re'istro de control" &ue deJne si las

l9neas de puerto son entradas o salidas!

I.terru"ir l! !l!-r! de co.trol6 En el modo I" %ands%a5e no es

usada! ?as interrupciones son 'eneradas como una 4unci/n l/'ica de los

niEeles de seal de entrada!

&ESCRIPCION &E PINES

7

Oi'!+ Disposici/n de pines

del Z80

Fi*6> Disposici/n de pines

del Z80 PIO

Microprocesador Z80

&3 0 &O Z80-CPU bus de datos 2-idireccio.!l tri0est!t!l46

Este bus se utilia para trans4erir todos los datos # comandos entre la Z801

CP= # la Z801PIO! D0 es el bit menos si'niJcatiEo del bus!

PORTSEL B7A Sel puerto B o A Select 2i.su"os= !cti/os de

!lto46

Este pin deJne &uH puerto tendr acceso durante la trans4erencia de datos

entre la CP= # Z801la1PIO Z8O! =n niEel ba*o en este pin selecciona el puerto

A" mientras &ue un niEel alto selecciona Puerto 2! A menudo" el bit A0 de la

CP= se utilia para esta 4unci/n de selecci/n!

CONTSEL C7& Sel de control o datos de Select (insumos,

!cti/os de !lto46

Este pin deJne el tipo de trans4erencia de datos a ser realiado entre la CP=

# la PIO! =n niEel alto en este pin durante la escritura de la CP= a la PIO

%ace &ue el bus de datos Z80 debe interpretarse como un comando para el

puerto seleccionado por el 2$A" seleccione la l9nea!

=n niEel ba*o en este pin si'niJca &ue el bus de datos Z80 se utilia para

trans4erir datos entre la CP= # la PIO a menudo el bit Al de la CP= se

utiliar para esta 4unci/n!

CE Chip Enable 2i.su"os= !cti/os de -!B!46

,

Microprocesador Z80

=n niEel ba*o en el pin permite a la PIO aceptar el mando o entradas de

datos de la CP= durante un ciclo de escritura o para transmitir datos a la

CP= durante un ciclo de lectura!

?a seal es 'eneralmente una decodiJcaci/n de cuatro de I $ O los n0meros

de puerto &ue abarcan los puertos A # 2" los datos de control! S

C El reloj del sistema 2e.tr!d!46

El Z801PIO utilia el relo* Z80 sistema estndar para sincroniar

determinados seales internamente! Este es un relo* de una sola 4ase!

7M+ 2Ciclo de m!uina4

Es una seal de la CPU! Esta seal de la CP= se utilia como un pulso de

sincroniaci/n para controlar Earias operaciones internas de la PIO!

Cuando $ M+ est actiEa # el RD de seal es actiEa" el Z801CP= busca una

instrucci/n de la memoria! Por el contrario" cuando $ M+ se actiEa # $ IORQ

est actiEo" la CP= est reconociendo una interrupci/n! Adems" la seal de

Ml $ tiene otros dos 4unciones dentro de la Z801PIO!

7IOR' de entrada "salida Solicitud del Z80-CPU 2e.tr!d!=

!cti/o -!Bo46

?a seal $IORQ se utilia *unto con el 2$A" C$D Seleccione" el ICE" # $RD

seales para trans4erir los comandos # datos! Cuando $CE" $RD # $IORQ

estn actiEos" el puerto diri'ido por 2$A trans4erir datos a la CP= (una

operaci/n de lectura)! Por el contrario" cuando $CE # $IORQ estn actiEos

pero $RD no est actiEo" entonces el puerto diri'ido por 2$A se escribir en

la CP= #a sea con datos o in4ormaci/n de control se'0n lo especiJcado por

la C $ D Selecci/n de seal! Adems" si $IORQ # $M+ se actiEa al mismo

tiempo" la CP= est reconociendo una interrupci/n # el puerto de

interrumpir automticamente colocar su Eector de interrupci/n en el bus de

datos de la CP= si es la prioridad de dispositiEo de alto interHs en un

interruptor!

7 R& #eed Ciclo Condici$n %ur&dica ' Social de la Z80-CPU

2e.tr!d!= !cti/o -!Bo46

$RD es una lectura actiEa MEMORT o E$S de operaci/n de lectura en curso!

?a seal de RD $ se utilia con A $ 2 Seleccione" C$D" $CE # $IORQ seales

para trans4erir datos desde el Z801Z80 PIO a la CP=!

7IEL Entrada para (nterrumpir )abilitar 2e.tr!d!= !cti/os de

!lto46

Esta seal se utilia para 4ormar una prioridad de cone8i/n en cadena de

interrupci/n cuando ms de un dispositiEo impulsado por interrupci/n se

est utiliando! =n niEel alto en el pin indica &ue otro dispositiEo de ma#or

prioridad no est siendo atendido por un serEicio de rutina de interrupci/n

de la CP=!

7OEI S!lid! !r! I.terruci:. 9!-ilit!r 2s!lid!= !cti/os de

!lto46

?a seal de la OEI es la seal de otra 9ndole necesaria para 4ormar una

cadena de sistema de prioridades! Es alta s/lo si IE? es alta # la CP= no es

una interrupci/n de serEicio de este PIO! Por lo tanto" esto blo&uea la seal

de dispositiEos de menor prioridad de la interrupci/n" mientras &ue una

ma#or prioridad

7INT

C

Fi*6A Disposici/n de pines de la RAM

,++,

Microprocesador Z80

Petici/n de interrupci/n (producci/n" drena*e abierto" actiEo ba*o)! Cuando

$I>; est actiEo el Z80 PIO est solicitando una interrupci/n de la CP= Z80!

&isositi/os de !l"!ce.!"ie.to: Me"ori!s RAM ,++, D EEPROM

>$>,

RAM ,++,

El dispositiEo ,++, es una memoria de acceso aleatorio" Random Acces

Memor# (RAM)" cuenta con una capacidad de 30-8 palabras de 8 bits cada

una" es una memoria esttica de alta Eelocidad" est 4abricada con la

tecnolo'9a CMOS" opera con una 4uente de alimentaci/n de R7!0 <olts #

est dispuesta en una pastilla de 3- terminales! El bus de direcciones consta

de once terminales (3

++

U30-8)" el bit menos si'niJcatiEo es A0 # el ms

si'niJcatiEo es A+0! El bus de datos es de 8 bits # Ea desde I$O0 %asta I$OC!

;iene adems una terminal de %abilitaci/n (c%ip select)" # terminales &ue

indican modo lectura o escritura VE # OE

ES'(EMA

RES(MEN &E CARACTERSTICAS &E LA MEMORIA RAM ,++,

Or'aniaci/n de la memoriaK 30-8 W 8

2a*a potencia en estado inactiEoK +0 XV

2a*a potencia en estado actiEoK +,0 mV

RAM completamente estticaK >o re&uiere relo* para su 4uncionamiento

Ran'o de ;emperatura de operaci/n 177 a R+37 'rados cent9'rados de

acuerdo a estas temperaturas el traba*o de la memoria es distinto lo

&ue se muestra en la tabla si'uiente

8

Fi*6E Disposici/n de pines de la

EEPROM 38+,

Microprocesador Z80

055F G+>5F

;iempo de acceso m8imo +70 ns +87ns

Corriente Output Enable ,0 ns 80 ns

Corriente de operaci/n

m8ima

-7mA -7mA

Corriente de standb#

;;?

CMOS

+!CmA

70XA

3mA

700XA

Potencia de disipaci/nK + Vatts

;odas sus entradas # salidas son compatibles directamente con la

tecnolo'9a ;;?

Es directamente compatible con las memorias de +,. estndar" tipo RAM

,+I3

T!-l! de /erd!d !r! oer!cio.es de lectur! D escritur!

OPERACI

N

L 9 L ?ectura

L L H Escritura

EEPROM >$+,

El circuito inte'rado EEPROM 38+, es una memoria repro'ramable #

borrable &ue contiene 30-8 localidades de memoria con 8 bits cada una"

(3. W 8) # opera con una sola 4uente de alimentaci/n de R 7 <! Est

4abricada con la tecnolo'9a >MOS! Es una memoria no Eoltil" todas las

tensiones &ue usa son compatibles" con la tecnolo'9a ;;?!

ES'(EMA

G

T!-l!6 A <alores de operaci/n

RAM ,++,

T!-l!6, ;abla de Eerdad para actiEaci/n de modos en la

RAM ,++,

Microprocesador Z80

RES(MEN &E CARACTERSTICAS >$+,

Or'aniaci/n de la memoria 30-8 W8

;ipo de 4uncionamientoF c%ip esttico

;iempos de acceso a lecturaF 370 nse'!

Capacidad de correcci/n para un solo bit tiempo de escritura ma8" +0

mse'!

Ran'os de ;emperatura 1-0BC a R87BC!

Potencia de disipaci/n

a) Estado actiEoF ,+0 MY

b) Estado inactiEoK 3G7 mV

T!-l! de /erd!d !r! oer!cio.es de est! "e"ori!

OPERACI

N

L 9 L ?ectura

L 9 Escritura

ES'(EMA &E CONEHIN &EL #$% CON OTROS &ISPOSITIVOS )

MEMORIAS

+0

T!-l!63 ;abla de Eerdad para actiEaci/n de modos en la

EEPROM 38+,

Microprocesador Z80

AR'(ITECT(RA &EL SISTEMA

Este procesador est concebido precisamente para una ar&uitectura <on

>eumann" por lo cual se accede a las dos memorias (datos # pro'rama)

mediante un 0nico bus de direcciones!

Ali"e.t!ci:. de todo el siste"! 7<

Frecue.ci! de reloB esco*id! -M6

Otros ele"e.tos utiliI!dos !r! l! co.strucci:. del siste"!

Re'ulador C807K Estabilia el Eolta*e de 7< para todo el sistema!

Decodificador C-?S+I8>K El decodiJcador es un circuito &ue recibe n

entradas # produce 3

n

salidas! Puede Eerse como un 'enerador de

min tHrminos" puesto &ue cada salida corresponde a una de las 3

n

combinaciones de entrada! De todas las salidas" solo se 'enerar un

+ en la salida cu#o sub 9ndice corresponde al c/di'o binario de la

combinaci/n de entrada!

?os decodiJcadores se utilian en los sistemas di'itales para diEersas

aplicaciones" como lo sonK direccionar una localidad de memoria"

conEersi/n de datos binarios" # para 'enerar 4unciones l/'icas

++

Fi*6E ;abla de Eerdad para actiEaci/n de modos en la

EEPROM 38+,

Fi*65 Disposici/n de pines de DecodiJcador

C-?S+I8

Microprocesador Z80

ArJuitectur! del "icroroces!dor #$%

+3

Fig.6 Ar&uitectura del

microprocesador Z80

Microprocesador Z80

ArJuitectur! Ku.d!"e.t!l

+I

Fig.7 Ar&uitectura Oundamental del

microprocesador Z80

Microprocesador Z80

+-

Microprocesador Z80

CONCL(SIONES

El sistema es simple debido a su ar&uitectura

Zilo'" el 4abricante de este procesador brinda adems al'unos elementos

compatibles con Hste" como es el caso del Z80 PIO!

E? Z80 PIO no necesita direccionamiento pues no es un dispositiEo de

almacenamiento

E? Z80 PIO puede recibir no solo datos (in4ormaci/n)Fsino tambiHn

comandos (conJ'uraci/n)!

En el diseo no se necesita multiple8ar los buses de direcci/n # de datos"

pues son independientes

RECOMEN&ACIONES

Es necesario analiar las tablas de Eerdad antes de conectar los pines

correspondientes

Es importante no de*ar las entradas Notantes se debe ase'urarlas a un

estado l/'ico" utiliando las dos conJ'uraciones de resistencias Pullup o

PulldoYn

Para el diseo es importante determinar la aplicaci/n # el ambiente de

traba*o" pues con esto se puede determinar la utiliaci/n de elementos

para &ue el sistema soporte las condiciones de operaci/n!

BIBLIOGRAFA

%ttpK$$YYY!datas%eetcatalo'!com

%ttpK$$proton!uctin'!ud'!m8$dpto$maestros$mateos$80$ar&uitectura$ar&u

itectura!%tml

%ttpK$$YYY!80!in4o$ip$80piomn!pd4

%ttpK$$proton!uctin'!ud'!m8$dpto$maestros$mateos$memorias$memorias!

%tml

%ttpK$$YYY!specc#!or'$curso1cm$4rZcapI!%tml

%ttpK$$medusa!unimet!edu!Ee$sistemas$bpis0I$decodiJcadores!%tm

+7

También podría gustarte

- Solución Examen MicrocontroladoresDocumento4 páginasSolución Examen MicrocontroladoresDonato Aquino Barrios67% (3)

- Memoria EEPROMDocumento18 páginasMemoria EEPROMDenis Arturo Zarate VictoriaAún no hay calificaciones

- Capitulo7. Timer1 Del AVR Del ATmega32 (Español)Documento22 páginasCapitulo7. Timer1 Del AVR Del ATmega32 (Español)Fortino80% (5)

- Puerto ParaleloDocumento6 páginasPuerto ParaleloAndrés A. PavónAún no hay calificaciones

- ATmega 164p (ESP)Documento378 páginasATmega 164p (ESP)inalac2Aún no hay calificaciones

- Arquitectura Básica Del Computador (Informe) CarlosGarcia 28.347.014Documento47 páginasArquitectura Básica Del Computador (Informe) CarlosGarcia 28.347.014CarlosRamses GpAún no hay calificaciones

- Capitulo III - Interfaz ParalelaDocumento72 páginasCapitulo III - Interfaz ParalelaJorge Gianotti HidalgoAún no hay calificaciones

- Tarea 2 Héctor López MontielDocumento3 páginasTarea 2 Héctor López MontielLópez M. HéctorAún no hay calificaciones

- Instrucciones Basicas de QbasicDocumento8 páginasInstrucciones Basicas de QbasicJonathan BautistaAún no hay calificaciones

- Resumen de Hoja de Datos PIC16F877Documento21 páginasResumen de Hoja de Datos PIC16F87724santi100% (1)

- Guia Pics CompletaDocumento142 páginasGuia Pics Completaapi-27535945100% (4)

- PP PLC 003 v1.0 PLC Mitsubishi - Programacion SFCDocumento17 páginasPP PLC 003 v1.0 PLC Mitsubishi - Programacion SFCRicardo Pelao LetelierAún no hay calificaciones

- Programacion Z80 en EnsambladorDocumento52 páginasProgramacion Z80 en EnsambladorJosé Luis Pallo100% (5)

- Microprocesador Z80Documento8 páginasMicroprocesador Z80Alissa100% (1)

- Interrupciones Del Procesador Z80Documento5 páginasInterrupciones Del Procesador Z80Joel Lema ChulliAún no hay calificaciones

- Procesador z80Documento15 páginasProcesador z80Abraham Contreras100% (1)

- Un Microprocesador de 8 Bits Z80Documento85 páginasUn Microprocesador de 8 Bits Z80Sebastián SandovalAún no hay calificaciones

- 14 La Memoria y El z80Documento15 páginas14 La Memoria y El z80Anonymous qTKCWlxAún no hay calificaciones

- En La Familia Z8000 de Zilog Se Utiliza Un Formato de Instrucciones SimilaresDocumento1 páginaEn La Familia Z8000 de Zilog Se Utiliza Un Formato de Instrucciones SimilaresJorge Eduardo Pullaguari UchuariAún no hay calificaciones

- Exp No 8 El Microprocesador Z80Documento18 páginasExp No 8 El Microprocesador Z80Richy Ploneda100% (1)

- Capitulo6. Timer0 Del AVR Del ATmega32 (Español)Documento13 páginasCapitulo6. Timer0 Del AVR Del ATmega32 (Español)Fortino100% (3)

- Contador de Programa Del Microprocesador Z80Documento10 páginasContador de Programa Del Microprocesador Z80FernandoQuisaguano0% (1)

- Tutorial Asm Pic16f84 y Pic16f877aDocumento42 páginasTutorial Asm Pic16f84 y Pic16f877aAns Shel Cardenas YllanesAún no hay calificaciones

- Modulo Adc Atmega8Documento20 páginasModulo Adc Atmega8Jean MelendezAún no hay calificaciones

- Tesis de Ingenieria de Rodrigo Jiménez LópezDocumento199 páginasTesis de Ingenieria de Rodrigo Jiménez LópezRodrigoJiménez100% (4)

- Interrupciones en Mikroc: Una Ayuda Muy Valiosa: IntroducciónDocumento6 páginasInterrupciones en Mikroc: Una Ayuda Muy Valiosa: IntroducciónlervinjcAún no hay calificaciones

- Microcontroladores - Interrupciones para El PIC16F84A en Ensamblador.Documento10 páginasMicrocontroladores - Interrupciones para El PIC16F84A en Ensamblador.Alfre2AlcazarAún no hay calificaciones

- Pract Z80Documento31 páginasPract Z80Arturo GuerreroAún no hay calificaciones

- Contador de Pulsos de Encoder Con ArduinoDocumento4 páginasContador de Pulsos de Encoder Con ArduinoPablo Quiroz TorresAún no hay calificaciones

- Curso en C para Pic CcsDocumento91 páginasCurso en C para Pic CcsOmar SolanoAún no hay calificaciones

- P05 Programacion en MikroBasicDocumento9 páginasP05 Programacion en MikroBasicRicardo NarvaezAún no hay calificaciones

- 3 Progra Del Microcontrolador en Ensamblador (3) (2792)Documento32 páginas3 Progra Del Microcontrolador en Ensamblador (3) (2792)Alfredo Pacheco ZapataAún no hay calificaciones

- (BASIC-16f877a) Encender y Apagar Led Con El Mismo PulsadorDocumento1 página(BASIC-16f877a) Encender y Apagar Led Con El Mismo PulsadorJeysonAún no hay calificaciones

- Lenguaje Ensamblador Del Z80Documento16 páginasLenguaje Ensamblador Del Z80Daniel Hernandez0% (1)

- LAB 3 - Registros y Transferencia Datos - 2016-2 PDFDocumento5 páginasLAB 3 - Registros y Transferencia Datos - 2016-2 PDFjaimeAún no hay calificaciones

- Fundamentos de Lenguaje C para PICsDocumento0 páginasFundamentos de Lenguaje C para PICssaulin1965Aún no hay calificaciones

- Laboratorio #3 Circuitos ElectrónicosDocumento6 páginasLaboratorio #3 Circuitos ElectrónicosMARIAAún no hay calificaciones

- Usb Con Pic18f4550 y Labview - Rev 2012Documento18 páginasUsb Con Pic18f4550 y Labview - Rev 2012Maicol Javier D M80% (5)

- Tutorial Proton Parte 2Documento10 páginasTutorial Proton Parte 2HectorLopezAún no hay calificaciones

- Lectura de Teclado Con Pic 18f4550 AssemblerDocumento6 páginasLectura de Teclado Con Pic 18f4550 AssemblerDigby CastilloAún no hay calificaciones

- Manejo de Matriz de LedDocumento7 páginasManejo de Matriz de LedmarcosolveraAún no hay calificaciones

- Exposicion de Timer RetardoDocumento48 páginasExposicion de Timer RetardoAbrahan HCAún no hay calificaciones

- Curso de Programación de PIC en PICBasic Pro - Página 4Documento93 páginasCurso de Programación de PIC en PICBasic Pro - Página 4Rene Gonzales VasquezAún no hay calificaciones

- El Módulo Adc de Los Avr PDFDocumento27 páginasEl Módulo Adc de Los Avr PDFmi_papiAún no hay calificaciones

- Protocolo MDBDocumento16 páginasProtocolo MDBRoman ClarkAún no hay calificaciones

- Picbasic Manual EspañolDocumento79 páginasPicbasic Manual EspañolAdriàn Garcìa FelicianoAún no hay calificaciones

- Pid ArduinoDocumento13 páginasPid ArduinoCristoObal GuevaraAún no hay calificaciones

- 2 Teoria - Registro de PuertosDocumento4 páginas2 Teoria - Registro de PuertosIvan Andres MuñozAún no hay calificaciones

- Tutorial Basico de ProtonDocumento22 páginasTutorial Basico de Protonantonyjrp100% (1)

- CronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidDocumento10 páginasCronoCronometro Digital Controlado Por Bluetooth en Una Aplicación Androidmetro Digital Controlado Por Bluetooth en Una Aplicación AndroidHarold Stiven Amaya VillamilAún no hay calificaciones

- BascomDocumento51 páginasBascomLizette RojasAún no hay calificaciones

- Primer Examen Parcial de Microprocesadores IDocumento3 páginasPrimer Examen Parcial de Microprocesadores IGustavoPaolo MaldonadoCallisaya100% (1)

- Prueba de AmplificadorDocumento5 páginasPrueba de AmplificadorJuan Manuel SotomayorAún no hay calificaciones

- RS232 Converter MAX3232 PDFDocumento3 páginasRS232 Converter MAX3232 PDFVictor Colpo NavarreteAún no hay calificaciones

- INFORME mpZ80Documento14 páginasINFORME mpZ80Cristian PerugachiAún no hay calificaciones

- Proton - Ucting.udg - MX Dpto Maestros Mateos z80 ArquitectuDocumento7 páginasProton - Ucting.udg - MX Dpto Maestros Mateos z80 Arquitectusanchez2328Aún no hay calificaciones

- Análisis General de Un MicroprocesadorDocumento20 páginasAnálisis General de Un MicroprocesadoroposeitorAún no hay calificaciones

- Arquitectura Del Microprocesador z80Documento5 páginasArquitectura Del Microprocesador z80manue1969Aún no hay calificaciones

- Microprocesador PicDocumento8 páginasMicroprocesador PicYonni RosasAún no hay calificaciones

- Microprocesador Z80Documento8 páginasMicroprocesador Z80Eliuth Cruz CamarilloAún no hay calificaciones

- Sistemas EmbebidosDocumento86 páginasSistemas EmbebidosfrednielsAún no hay calificaciones

- El Microprocesador (P) Intel 8086/8088: I107 - Arquitectura de ComputadorasDocumento43 páginasEl Microprocesador (P) Intel 8086/8088: I107 - Arquitectura de ComputadorasLeventen Aldave RamirezAún no hay calificaciones

- Micro Lab1Documento9 páginasMicro Lab1Alex MercerAún no hay calificaciones

- Exposicion EconomicaDocumento13 páginasExposicion EconomicaBry Ruiz MendezAún no hay calificaciones

- DAQDocumento19 páginasDAQBry Ruiz MendezAún no hay calificaciones

- Exposicion EconomicaDocumento13 páginasExposicion EconomicaBry Ruiz MendezAún no hay calificaciones

- Costos - Grupo2Documento16 páginasCostos - Grupo2Bry Ruiz MendezAún no hay calificaciones

- Exposicion de Maquinas de Corriente Continua Mueses-Ruiz, SanchezDocumento14 páginasExposicion de Maquinas de Corriente Continua Mueses-Ruiz, SanchezBry Ruiz MendezAún no hay calificaciones

- Tutorial MatLab 16Documento28 páginasTutorial MatLab 16Pol VaquéAún no hay calificaciones

- ReadmeDocumento1 páginaReadmesport0378Aún no hay calificaciones

- Memorias Rom Con SemicondutoresDocumento8 páginasMemorias Rom Con SemicondutoresBry Ruiz MendezAún no hay calificaciones

- Codigo de La PrducciònDocumento88 páginasCodigo de La PrducciònBry Ruiz MendezAún no hay calificaciones

- EncapsulamientoDocumento2 páginasEncapsulamientoBry Ruiz MendezAún no hay calificaciones

- Cuestionario Tarjetas Madres 1Documento3 páginasCuestionario Tarjetas Madres 1DANIEL EDUARDO MADRID MADRIDAún no hay calificaciones

- Partes de La Placa BaseDocumento11 páginasPartes de La Placa BaseJean Marco Apaza MachacaAún no hay calificaciones

- 4 El8051Documento12 páginas4 El8051alexciviAún no hay calificaciones

- Aportes Fase 4Documento4 páginasAportes Fase 4carlos mancillaAún no hay calificaciones

- Especificaciones de La CPU: 4th Generation Intel® Core™ I5 Processors Products Formerly HaswellDocumento2 páginasEspecificaciones de La CPU: 4th Generation Intel® Core™ I5 Processors Products Formerly HaswellAxel Danger RodriguezAún no hay calificaciones

- Micro ProcesadoresDocumento9 páginasMicro ProcesadoresLeslie Burrita Cureño100% (1)

- Tarea ExcelDocumento6 páginasTarea ExcelRubén Michca HuayllaniAún no hay calificaciones

- Panel Trasero y ChipsetDocumento4 páginasPanel Trasero y Chipset3Seconds Loop / Cangrejo GentilAún no hay calificaciones

- 2 RISC y CISC - En.es PDFDocumento21 páginas2 RISC y CISC - En.es PDFGerald AburtoAún no hay calificaciones

- Microprocesador 1 - 2 PDFDocumento72 páginasMicroprocesador 1 - 2 PDFMar YfhAún no hay calificaciones

- Chipset 1Documento11 páginasChipset 1Guillermo CalderónAún no hay calificaciones

- Presupuesto 1Documento1 páginaPresupuesto 1vica0_0Aún no hay calificaciones

- CISC y RISCDocumento21 páginasCISC y RISCFernando Trujillo PlazaAún no hay calificaciones

- Modo Real y Protegido Mod PDFDocumento10 páginasModo Real y Protegido Mod PDFJhon LopezAún no hay calificaciones

- MicroI TeoriaDocumento48 páginasMicroI Teoriaottoniel RosarioAún no hay calificaciones

- Tema 2Documento35 páginasTema 2AlbertoAún no hay calificaciones

- LISTA PORTATILES JULIO 24 - CompressedDocumento3 páginasLISTA PORTATILES JULIO 24 - CompressedHanne J. Bayeh VillarrealAún no hay calificaciones

- Taller Ij Micros - TELADocumento2 páginasTaller Ij Micros - TELAJuan Esteban BarbosaAún no hay calificaciones

- Poliza Modelo Excel Coi7.0Documento8 páginasPoliza Modelo Excel Coi7.0Daniel RamosAún no hay calificaciones

- Práctica 1Documento6 páginasPráctica 1Julio A. PadillaAún no hay calificaciones

- Lista de Precios Ovalo 24 - Miercoles 13 de Octubre Del 2021Documento119 páginasLista de Precios Ovalo 24 - Miercoles 13 de Octubre Del 2021luisAún no hay calificaciones

- Sockets y Procesadores Intel y AMDDocumento21 páginasSockets y Procesadores Intel y AMDJuan67% (3)

- Memorias RamDocumento7 páginasMemorias RamjsbnsjszAún no hay calificaciones

- Microprocesador PDFDocumento19 páginasMicroprocesador PDFseleneAún no hay calificaciones

- BIOSDocumento20 páginasBIOSa.juanfernandezAún no hay calificaciones

- Clase 1 IntroDocumento65 páginasClase 1 IntrosilkersaAún no hay calificaciones

- Examen de Mantenimiento y Reparación de ComputadorasDocumento3 páginasExamen de Mantenimiento y Reparación de Computadorasmojica009Aún no hay calificaciones