Documentos de Académico

Documentos de Profesional

Documentos de Cultura

05 U1 Electrónica Digital - Familias Lógicas - Detección y Corrección de Fallas

Cargado por

Luis Armando Reyes CardosoDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

05 U1 Electrónica Digital - Familias Lógicas - Detección y Corrección de Fallas

Cargado por

Luis Armando Reyes CardosoCopyright:

Formatos disponibles

ElectrnicaDigital

22/05/2016

ElectrnicaDigital

FamiliasLgicas

Ing.LuisArmandoReyesCardoso

LuisArmandoReyesCardoso

IngenieroElectricista ITQ

PTC Mecatrnica.

email:

lreyes@uttt.edu.mx

7329112Mecatrnica

Ext.412

Ing.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

ElectrnicaDigital

22/05/2016

1.3 Familias Lgicas

Existen dos tecnologas de circuitos integrados digitales

que se usan para implementar las puertas lgicas

bsicas: CMOS y TTL. Las operaciones lgicas NOT, AND,

OR, NAND, NOR y ORexclusiva son las mismas,

independientemente de la tecnologa de circuitos

integrados que se utilice; es decir, una puerta AND tiene

la misma funcin lgica se implemente con la tecnologa

CMOS o TTL.

M.C.LuisArmandoReyesCardoso

1.3 Familias Lgicas

El trmino CMOS corresponde a Complementary MetalOxide Semiconductor

(semiconductor metal xido complementario) y se implementa con un tipo de

transistor de efecto de campo.

TTL (TransistorTransistor Logic, lgica transistortransistor) y se implementa

mediante transistores bipolares.

Tenga en cuenta que CMOS y TTL slo difieren en el tipo de componentes de circuito

y los valores de los parmetros, y no en las operaciones lgicas bsicas. Una puerta

AND CMOS realiza la misma operacin lgica que una puerta AND TTL. Esto tambin

es cierto para todas las operaciones lgicas bsicas restantes.

La diferencia entre CMOS y TTL se encuentra en las caractersticas de

funcionamiento, tal como la velocidad de conmutacin (retardo de propagacin), la

disipacin de potencia, la inmunidad al ruido y otros parmetros.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

ElectrnicaDigital

22/05/2016

CMOS

Existe poco desacuerdo sobre cul es la tecnologa de circuitos, CMOS o TTL, ms

ampliamente utilizada.

Parece que CMOS est comenzando a ser la tecnologa dominante y podra

reemplazar a la tecnologa TTL en los CI de pequea y mediana escala.

Aunque TTL ha dominado durante muchos aos, principalmente debido a sus altas

velocidades de conmutacin y a una enorme variedad de tipos de dispositivos, la

tecnologa CMOS siempre ha tenido la ventaja de ofrecer una mucho menor

disipacin de potencia, aunque dicho parmetro depende de la frecuencia.

Las velocidades de conmutacin de CMOS han mejorado extremadamente y ahora

pueden competir con TTL, a la vez que la baja disipacin de potencia y otros factores

deseables se han mantenido a medida que la tecnologa avanzaba.

M.C.LuisArmandoReyesCardoso

Series CMOS

Las categoras de CMOS en trminos de tensin de alimentacin continua son la

serie CMOS de 5 V, la serie CMOS de 3,3 V, la serie CMOS de 2,5 V y la serie CMOS de

1,8 V.

Las series CMOS de ms baja tensin son el resultado de un desarrollo ms reciente

y de un esfuerzo por reducir la disipacin de potencia.

Puesto que la disipacin de potencia es proporcional al cuadrado de la tensin, una

reduccin de 5 V a 3,3 V, por ejemplo, disminuye la potencia en un 34%, sin que el

resto de los factores varen.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

ElectrnicaDigital

22/05/2016

Series CMOS

Dentro de cada categora segn la tensin de alimentacin, hay

disponibles varias series de puertas lgicas CMOS.

Estas series pertenecientes a la familia CMOS difieren en sus

caractersticas de funcionamiento y se designan mediante los

prefijos 74 54, seguidos de una letra o letras que indican la serie y,

a continuacin, un nmero que indica el tipo de dispositivo lgico.

El prefijo 74 indica que se trata de un dispositivo comercial de

propsito general, y el prefijo 54 indica que es un dispositivo militar

para aplicaciones en entornos ms exigentes.

M.C.LuisArmandoReyesCardoso

Series CMOS

La serie bsica CMOS de 5 V y sus denominaciones son las siguientes:

74HC y 74HCT. CMOS de alta velocidad (la T indica compatibilidad TTL)

74AC y 74ACT. CMOS avanzada

74AHC y 74AHCT. CMOS de alta velocidad avanzada

La serie bsica CMOS de 3,3 V y sus denominaciones son las siguientes:

74LV. CMOS de baja tensin

74LVC. CMOS de baja tensin.

74ALVC. CMOS de baja tensin avanzada.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

ElectrnicaDigital

22/05/2016

Series CMOS

Adems de la serie 74, todava existe la serie 4000, que es una

tecnologa CMOS ms antigua y de baja velocidad, aunque su uso

est limitado.

Adems de las series CMOS "puras" existen series que combinan

ambas tecnologas, CMOS y TTL, que se denominan BiCMOS. La

serie bsica BiCMOS y sus denominaciones son las siguientes:

74BCT. BiCMOS

74ABT. BiCMOS avanzada.

74LVT. BiCMOS de baja tensin.

74ALB. BiCMOS de baja tensin.

M.C.LuisArmandoReyesCardoso

TTL

La tecnologa TTL ha sido y es todava una tecnologa de

circuitos integrados digitales muy popular.

Una ventajade esta tecnologa es que no es sensible a

las descargas electrostticas como lo es la tecnologa

CMOS y, por tanto, es ms prctica en la realizacin de

experimentos de laboratorio y la elaboracin de

prototipos, ya que no es necesario preocuparse por los

problemas de manipulacin.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

10

ElectrnicaDigital

22/05/2016

Series TTL

Al igual que con la tecnologa CMOS, hay disponibles varias series

de puertas lgicas TTL, las cuales operan todas ellas con 5 V de

alimentacin de continua.

Estas series pertenecientes a la familia TTL difieren en sus

caractersticas de funcionamiento y se denominan mediante los

prefijos 74 54 seguidos por una letra o letras que indican la serie y

un nmero que indica el tipo de dispositivo lgico de la serie.

Un circuito integrado TTL puede distinguirse de un circuito

integrado CMOS por las letras que siguen a los prefijos 74 y 54.

M.C.LuisArmandoReyesCardoso

11

Series TTL

Las series bsicas TTL y sus denominaciones son las

siguientes:

74:TTL estndar(sinletra).

74S:TTL Schottky.

74AS:TTL Schottky avanzada.

74LS:TTL Schottky debajapotencia.

74ALS:TTL Schottky debajapotenciaavanzada.

74F:TTL rpida.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

12

ElectrnicaDigital

22/05/2016

FamiliasLgicasSerie74BasadasenlaTecnologadelosCircuitos

M.C.LuisArmandoReyesCardoso

13

Tipos de Puertas Lgicas de Funcin Fija

Todas las operaciones lgicas bsicas: NOT, AND, OR,

NAND, NOR, ORexclusiva (XOR) y NORexclusiva

(XNOR) estn disponibles en las tecnologas CMOS y TTL.

Tambin estn disponibles puertas con salida bfer para

excitar cargas que requieran altas corrientes.

Los tipos de configuraciones de puerta normalmente

disponibles en los circuitos integrados se identifican

mediante los dos o tres dgitos finales de la designacin

de la serie.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

14

ElectrnicaDigital

22/05/2016

Tipos de Puertas Lgicas de Funcin Fija

Cudruple NAND de dos entradas: 00

CudrupleNOR dedosentradas:02

Inversorsxtuple:04

CudrupleANDdedosentradas:08

TripleNAND detresentradas:10

TripleANDdetresentradas:11

DobleNAND decuatroentradas:20

DobleANDdedosentradas:21

TripleNOR detresentradas:27

NAND deochoentradas:30

CudrupleOR dedosentradas:32

CudrupleXOR:86

CudrupleXNOR:266

M.C.LuisArmandoReyesCardoso

15

Encapsulados de Circuitos

Integrados

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

16

ElectrnicaDigital

22/05/2016

Encapsulados de Circuitos

Integrados

M.C.LuisArmandoReyesCardoso

17

Diagramas de

Configuracin de los Pines

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

18

ElectrnicaDigital

22/05/2016

Caractersticas y Parmetros de Funcionamiento

Existen varios puntos que definen el funcionamiento de un

circuito lgico.

Las caractersticas de funcionamiento son: la velocidad de

conmutacin medida en trminos del retardo de

propagacin, la disipacin de potencia, el fanout o

capacidad de excitacin, el producto velocidadpotencia,

la tensin de alimentacin continua y los niveles lgicos de

entrada/salida.

M.C.LuisArmandoReyesCardoso

19

Tiempo de Retardo de Propagacin

Este parmetro limita la frecuencia o velocidad de

conmutacin a la que un circuito lgico puede operar.

Cuando se aplican a los circuitos lgicos, los trminos baja

velocidad y alta velocidad hacen referencia al retardo de

propagacin.

Cuanto menor sea el tiempo de propagacin, mayor ser la

velocidad del circuito y mayor ser la frecuencia a la que

puede operar.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

20

10

ElectrnicaDigital

22/05/2016

Tiempo de Retardo de Propagacin

El tiempo de retardo de propagacin, tP, de una puerta lgica es el intervalo de

tiempo entre la aplicacin de un impulso de entrada y la aparicin del impulso de

salida resultante.

Existen dos medidas diferentes del tiempo de retardo de propagacin asociado

con una puerta lgica, que se aplican a todos los tipos de puertas bsicas:

tPHL: es el tiempo entre un punto de referencia especificado en el impulso de

entrada y el correspondiente punto de referencia en el impulso de salida, cuando la

salida cambia del nivel ALTO (H) al nivel BAJO (L).

tPLH: es el tiempo entre un punto de referencia especificado en el impulso de

entrada y el correspondiente punto de referencia en el impulso de salida, cuando la

salida cambia del nivel BAJO (L) al nivel ALTO (H).

M.C.LuisArmandoReyesCardoso

21

Ejemplo

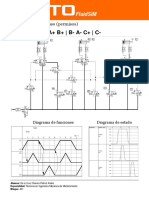

Determinar los tiempos de propagacin en el inversor de la siguiente figura.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

22

11

ElectrnicaDigital

22/05/2016

Solucin

Los tiempos de propagacin, tPHL y tPLH, se indican en la parte (b) de la figura.

En este caso, los retrasos se miden entre los puntos de pendiente del 50%

en los correspondientes flancos de los impulsos de entrada y salida. Los

valores de tPHL y tPLH no necesariamente son iguales pero, en la mayora de

los casos, s lo son.

ProblemaRelacionado

Una puerta lgica tiene una valor mximo especificado de 10 ns para tPHL y

tPLH. Para otros tipos de puertas este valor es de 4 ns. Cul es la puerta que

puede trabajar a la frecuencia mayor?

M.C.LuisArmandoReyesCardoso

23

Retardo de Propagacin

En las puertas TTL de la serie estndar, el retardo de

propagacin tpico es de 11 ns y para las puertas de la serie F

es de 3,3 ns.

Para las puertas CMOS de la serie HCT, el retardo de

propagacin es 7 ns, para la serie AC es de 5 ns y para la

serie ALVC es de 3 ns.

Todos los valores especificados dependen de determinadas

condiciones de operacin, tal y como se establece en las

hojas de caractersticas.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

24

12

ElectrnicaDigital

22/05/2016

Tensin de Alimentacin Continua (Vcc)

La tensin de alimentacin continua tpica para CMOS puede ser 5 V; 3,3 V, 2,5 V

o 1,8 V, dependiendo de la categora.

Una ventaja de CMOS es que las tensiones de alimentacin pueden variar en un

rango ms amplio que los dispositivos TTL.

Los CMOS de 5 V pueden tolerar variaciones de alimentacin desde los 2 V a 6 V y

an as funcionarn adecuadamente, aunque el retardo de propagacin y la

disipacin de potencia se vean significativamente afectadas.

Los dispositivos CMOS de 3,3 V pueden operar con tensiones de alimentacin

desde 2 V hasta 3,6 V.

La tensin de alimentacin continua tpica para dispositivos TTL es 5,0 V con un

mnimo de 4,5 V y un mximo de 5,5 V.

M.C.LuisArmandoReyesCardoso

25

Disipacin de Potencia

La disipacin de potencia, PD, de una puerta lgica es el producto de la tensin

de alimentacin continua y de la corriente media de alimentacin.

Normalmente, la corriente de alimentacin cuando la salida de la puerta est a

nivel BAJO es mayor que cuando la salida de la puerta est a nivel ALTO.

Generalmente, las hojas de caractersticas del fabricante especifican la corriente

de alimentacin para el estado de salida BAJO como ICCL y para el estado ALTO

como ICCH.

La corriente media de alimentacin se determina en funcin de un ciclo de

trabajo del 50% (nivel de salida BAJO la mitad del tiempo y la otra mitad nivel de

salida ALTO), por tanto la disipacin de potencia media de una puerta lgica es

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

26

13

ElectrnicaDigital

22/05/2016

Disipacin de Potencia

Las puertas de la serie CMOS tienen disipaciones de potencia muy bajas en

comparacin con las series TTL.

Sin embargo, la disipacin de potencia en los dispositivos CMOS depende de la

frecuencia de funcionamiento.

Para una frecuencia cero, la potencia est normalmente en el rango de los

microvatios por puerta, y en la frecuencia mxima de funcionamiento puede

estar en el rango de los miliwatts; por tanto, algunas veces la potencia se

especifica para una frecuencia determinada. Por ejemplo, la serie HC tiene una

potencia de 2,75 W/puerta para una frecuencia igual a 0 Hz y de 600 W/puerta

para 1 MHz.

La disipacin de potencia para los dispositivos TTL es independiente de la

frecuencia.

Por ejemplo, la serie ALS disipa 1,4 mW/puerta, independientemente de la

frecuencia y la serie F disipa 6 mW/puerta.

M.C.LuisArmandoReyesCardoso

27

Niveles Lgicos de Entrada y Salida

VIL es la tensin del nivel de entrada BAJO para una puerta lgica y VIH es la tensin de

entrada del nivel ALTO.

Los dispositivos CMOS de 5 V aceptan una tensin mxima de 1,5 V para VIL y una

tensin mnima de 3,5 V para VIH.

Los dispositivos TTL aceptan una tensin mxima de 0,8 V para VIL y una tensin

mnima de 2 V para VIH.

VOL es la tensin de salida para el nivel BAJO y VOH es la tensin de salida para el nivel

ALTO.

Para los dispositivos CMOS de 5 V, el valor mximo de VOL es de 0,33 V y el valor

mnimo para VOH es de 4,4 V.

Para los dispositivos TTL, el valor mximo VOL es de 0,4 V y el mnimo VOH es de 2,4 V.

Todos los valores dependende las condiciones de operacin, tal y como se especifica

en la hoja de caractersticas.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

28

14

ElectrnicaDigital

22/05/2016

Niveles Lgicos de Entrada y Salida

VCC

VOH

Salida

Entrada

VCC

1

VIH

Zona de

incertidumbre

VOL

0

VIL

0

VIH: Tensin de entrada mnima para asegurar que el nivel se interpreta como 1

VIL: Tensin de entrada mxima para asegurar que el nivel se interpreta como 0

VOH: Tensin de salida mnima a nivel alto

VOL: Tensin de salida mxima a nivel bajo

M.C.LuisArmandoReyesCardoso

29

Niveles Lgicos de Entrada y Salida

VCC

VOH

Salida

Entrada

VCC

1

VIH

Zona de

incertidumbre

VOL

0

VIL

0

Para que una entrada y una salida sean compatibles en niveles de tensin:

VOH > VIH

VOL < VIL

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

30

15

ElectrnicaDigital

22/05/2016

Niveles Lgicos de Entrada y Salida

Niveles de corriente:

IOH: es la corriente mxima que puede suministrar una salida a nivel alto

IOL: es la corriente mxima que puede absorber una salida a nivel bajo

IIH: es la corriente que consume una entrada a nivel alto

IIL: es la corriente que consume una entrada a nivel bajo

M.C.LuisArmandoReyesCardoso

31

Niveles Lgicos de Entrada y Salida

El parmetro SPP (SpeedPower Product) puede utilizarse como una medida del

funcionamiento de un circuito lgico que tiene en cuenta el retardo de propagacin y

la disipacin de potencia.

Es especialmente til para comparar las distintas series de puertas lgicas de las

familias CMOS o TTL o para comparar una puerta CMOS con una puerta TTL.

El producto SPP de un circuito lgico es igual al producto del retardo de propagacin

por la disipacin de potencia, y se expresa en julios (J), que es una unidad de energa.

La frmula es

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

32

16

ElectrnicaDigital

22/05/2016

Ejemplo

Una determinada puerta tiene un retardo de propagacin de 5 ns, ICCH = 1 mA e ICCL = 2,5

mA, con una tensin de alimentacin continua de 5 V. Determinar el producto

velocidadpotencia.

Solucin

Problema relacionado

Si el retardo de propagacin de una puerta es 15 ns y su SPP es igual a 150 pJ, cul es

su disipacin de potencia media?

M.C.LuisArmandoReyesCardoso

33

Fan Out y Carga

El fanout de una puerta lgica es el nmero mximo de entradas de la familia de

circuitos integrados de la misma serie que la puerta puede excitar, manteniendo a la

vez los niveles de salida dentro de los lmites especificados.

El fanout es un parmetro importante slo en la tecnologa TTL.

Dado que con los circuitos CMOS se asocian impedancias muy altas, el fanout es

muy alto, aunque depende de la frecuencia debido a los efectos capacitivos.

El fanout se especifica en trminos de cargas unidad.

Una carga unidad para una puerta lgica es igual a una entrada de un circuito similar.

Por ejemplo, una carga unidad para una puerta NAND 74LS00 es igual a una entrada

a una puerta lgica en la serie 74LS (no necesariamente una puerta NAND).

Puesto que la corriente para una entrada a nivel BAJO (IIL) de una puerta 74LS00 es

de 0,4 mA y la corriente que una salida a nivel BAJO (IIL) puede aceptar es de 8,0 mA,

el nmero de cargas unidad que una puerta 74LS00 puede excitar en el estado BAJO

es

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

34

17

ElectrnicaDigital

22/05/2016

M.C.LuisArmandoReyesCardoso

35

Comparacin TTL - CMOS

Disipacin

esttica

Disipacin a

100 kHz

Tpo.

propagacin

Fan-out

Cdigo

CMOS

Silicon-gate

74HC- 74HCT

2.5 nW

0.17 mW

8 ns

CMOS

Metal-gate

4000B

1 W

0.1 mW

50 ns

TTL

Estndard

74

10 mW

10 mW

10 ns

10

TTL

S

74S

19 mW

19 mW

3 ns

20

TTL

LS

74LS

2 mW

2 mW

10 ns

20

TTL

ALS

74ALS

1 mW

1 mW

4 ns

20

TTL

AS

74AS

8.5 mW

8.5 mW

1.5 ns

40

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

36

18

ElectrnicaDigital

22/05/2016

Hojas de Caractersticas

M.C.LuisArmandoReyesCardoso

37

M.C.LuisArmandoReyesCardoso

38

Hojas de Caractersticas

Ing.LuisArmandoReyesCardoso

19

ElectrnicaDigital

22/05/2016

Hojas de Caractersticas

M.C.LuisArmandoReyesCardoso

39

M.C.LuisArmandoReyesCardoso

40

Hojas de Caractersticas

Ing.LuisArmandoReyesCardoso

20

ElectrnicaDigital

22/05/2016

1.4 Medidas de seguridad en el manejo de las familias lgicas TTL y CMOS.

Precauciones para la Manipulacin de Dispositivos CMOS

Debido a su estructura, los dispositivos CMOS son muy sensibles a las cargas

estticas y pueden resultar daados por las descargas electrostticas si no se

manipulan correctamente. Al trabajar con dispositivos CMOS debern tomarse

las siguientes precauciones:

Los dispositivos CMOS deben ser suministrados y almacenados en espuma

conductiva.

Todos los instrumentos y bancos metlicos utilizado en las prueban debern

conectarse a una toma de tierra.

Las herramientas de trabajo deben conectarse a tierra a travs de un cable y

resistencias en serie de alto valor.

No debe retirarse un dispositivos CMOS (o cualquier dispositivo) de un

circuito mientras que la alimentacin continua est conectada.

o deben conectarse tensiones de seal o corriente a un dispositivo CMOS

cuando la alimentacin continua est apagada.

M.C.LuisArmandoReyesCardoso

41

1.4 Medidas de seguridad en el

manejo de las familias lgicas

TTL y CMOS.

Las entradas de puerta no utilizadas para TTL y CMOS deberan conectarse

al nivel lgico apropiado (ALTO o BAJO).

Para las puertas AND y NAND, es recomendable que las entradas no

utilizadas se conecten a VCC (a travs de una resistencia de 1,0 k para

TTL), y para las puertas OR y NOR, las puertas no utilizadas deberan

conectarse a tierra.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

42

21

ElectrnicaDigital

22/05/2016

1.5 Deteccin, Localizacin y Eliminacin de Fallas

La localizacin de averas es el proceso de reconocer, aislar y

corregir un fallo en un sistema o circuito.

Para poder localizar las averas de forma efectiva, debe entender

cmo se supone que trabaja el circuito o sistema y debe estar en

disposicin de reconocer un funcionamiento incorrecto.

Por ejemplo, para determinar si una puerta lgica tiene un fallo,

debe saber cul debe ser la salida para unas entradas dadas.

M.C.LuisArmandoReyesCardoso

43

Fallos Internos en las Compuertas Lgicas de los CI

Los circuitos abiertos y los cortocircuitos son los fallos ms

comunes en las puertas internas del CI.

Se pueden producir tanto en las entradas como en la salida de una

puerta contenida en el encapsulado del CI.

Antes de intentar solucionar cualquier avera, compruebe que la

alimentacin continua y la masa son correctas.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

44

22

ElectrnicaDigital

22/05/2016

Fallos Internos en las Compuertas Lgicas de los CI

Efectos de una entrada que se encuentra en circuito abierto internamente.

Un circuito abierto interno es el resultado de un componente en circuito abierto o

de una ruptura en la conexin entre el chip y el pin del encapsulado.

Una entrada en circuito abierto impide que una seal de impulsos en esta entrada

d lugar a una salida, como se muestra en la Figura (a) para la puerta NAND de 2

entradas.

Una entrada TTL en abierto acta como un nivel ALTO, por lo que los impulsos

aplicados a la entrada que est en buen estado pasan a travs de la puerta NAND

hasta la salida, como se muestra en la Figura (b).

M.C.LuisArmandoReyesCardoso

45

Condiciones para Probar las Compuertas

Al probar una puerta NAND o una puerta AND, debe asegurarse

siempre de que las entradas a las que no se aplican impulsos se

encuentren a nivel ALTO, para activar la puerta.

Cuando pruebe una puerta NOR o una puerta OR, debe asegurarse

siempre de que las entradas a las que no se aplican impulsos se

encuentran a nivel BAJO.

Cuando se prueba una puerta XOR o XNOR, el nivel de la entrada a

la que no se aplican impulsos no importa, ya que los impulsos

aplicados en la otra entrada forzarn a que las entradas se

encuentren, alternativamente, en el mismo nivel o en niveles

opuestos.

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

46

23

ElectrnicaDigital

22/05/2016

Localizacin de Fallo: Entrada en Circuito Abierto

La localizacin de este tipo de fallo es, en la mayora de los casos,

muy fcil utilizando un osciloscopio y un generador de funciones,

como se muestra en la Figura, para el caso de una puerta NAND de

2 entradas.

Al medir las seales digitales con un osciloscopio, emplee siempre

el acoplamiento en continua.

M.C.LuisArmandoReyesCardoso

47

Localizacin de Fallo: Entrada

en Circuito Abierto

M.C.LuisArmandoReyesCardoso

Ing.LuisArmandoReyesCardoso

48

24

También podría gustarte

- 100 circuitos de shields para arduino (español)De Everand100 circuitos de shields para arduino (español)Calificación: 3.5 de 5 estrellas3.5/5 (3)

- De Las Atribuciones y Funciones Del Presidente de La Junta de CondominioDocumento17 páginasDe Las Atribuciones y Funciones Del Presidente de La Junta de CondominioAnita Guedez67% (3)

- Conexion y Diagramas Motores ElectricosDocumento26 páginasConexion y Diagramas Motores Electricosvictorrecinos78% (23)

- .Documento92 páginas.Gabriela PavónAún no hay calificaciones

- Citrus Z450Documento2 páginasCitrus Z450elvis oriasAún no hay calificaciones

- Programación de Máquinas de CNC Con Códigos G&M - TecnoEduDocumento17 páginasProgramación de Máquinas de CNC Con Códigos G&M - TecnoEduHector HectorAún no hay calificaciones

- Proceso de Ensayo de Fatiga A Baja Frecuencia (Patente) DR JrasaDocumento11 páginasProceso de Ensayo de Fatiga A Baja Frecuencia (Patente) DR JrasaZoombisito FrancoAún no hay calificaciones

- Carrito Seguidor de LíneasDocumento13 páginasCarrito Seguidor de LíneasRicardo Victor Arroyo HuancaAún no hay calificaciones

- Tren de Engranes 3Documento5 páginasTren de Engranes 3Eduardo TapiaAún no hay calificaciones

- FAO Elearning Guide Es PDFDocumento144 páginasFAO Elearning Guide Es PDFquique100% (1)

- FAO Elearning Guide Es PDFDocumento144 páginasFAO Elearning Guide Es PDFquique100% (1)

- Lab02 - GL01Documento17 páginasLab02 - GL01Mario Ernesto Duran Lopez100% (1)

- Manual Fluid SimDocumento0 páginasManual Fluid SimSuray RezaAún no hay calificaciones

- Ejerciciario de LevasDocumento2 páginasEjerciciario de LevasCuauhtemoc Mazon ValadezAún no hay calificaciones

- Convertidor de 12V DC A 120V AC AutomáticoDocumento5 páginasConvertidor de 12V DC A 120V AC AutomáticoJaime PosadaAún no hay calificaciones

- John Deere Consejos Prácticos Motores Sistema de Admisión de Aire Del MotorDocumento2 páginasJohn Deere Consejos Prácticos Motores Sistema de Admisión de Aire Del MotorHenry ValenciaAún no hay calificaciones

- Instrumentación y Control. Equipo 6 - 5.3. - Actuadores (Servomotores)Documento35 páginasInstrumentación y Control. Equipo 6 - 5.3. - Actuadores (Servomotores)Noe Espinoza romeroAún no hay calificaciones

- Retícula Ingenieria Mecánica (Instituto Tecnológico de Nuevo Laredo)Documento2 páginasRetícula Ingenieria Mecánica (Instituto Tecnológico de Nuevo Laredo)Guillermo ReyesAún no hay calificaciones

- Algoritmo de Denavit-HartenbergDocumento3 páginasAlgoritmo de Denavit-HartenbergLuis LoyolaAún no hay calificaciones

- Tipos de Transmision de PotenciaDocumento1 páginaTipos de Transmision de PotenciaAntón SanchezAún no hay calificaciones

- Segundo Examen Parcial Mec2253Documento1 páginaSegundo Examen Parcial Mec2253JUAN FLORESAún no hay calificaciones

- Marco Teórico de EjesDocumento6 páginasMarco Teórico de EjesAndree Gutierrez Suclla100% (1)

- B) Metodo Paso A PasoDocumento4 páginasB) Metodo Paso A PasoandreAún no hay calificaciones

- 2012 Labview Pendulo SimpleDocumento6 páginas2012 Labview Pendulo SimpleAnderson Escobar0% (1)

- 1-3-Representación Matemática de Los Procesos de MuestreoDocumento3 páginas1-3-Representación Matemática de Los Procesos de MuestreoDicklizard GmAún no hay calificaciones

- Mecanismos de Retorno RápidoDocumento11 páginasMecanismos de Retorno RápidoFabio Milton CastroAún no hay calificaciones

- SistemasDocumento4 páginasSistemasBryan PupialesAún no hay calificaciones

- Evidencia 2 Interruptores ElectromagneticosDocumento14 páginasEvidencia 2 Interruptores ElectromagneticosVictor LiconaAún no hay calificaciones

- SprocketsDocumento18 páginasSprocketsFredi Isai Angeles MirandaAún no hay calificaciones

- Interferencia en EngranajesDocumento3 páginasInterferencia en EngranajesLuis Donaldo Flores MedinaAún no hay calificaciones

- Examen Segunda Unidad PDFDocumento7 páginasExamen Segunda Unidad PDFJsbonifazAún no hay calificaciones

- Instrumentación EjerciciosDocumento8 páginasInstrumentación EjerciciosNenita Dett100% (1)

- Circuitos de Descarga y Control de FaseDocumento11 páginasCircuitos de Descarga y Control de FaseDaniel Armando Lopez RodriguezAún no hay calificaciones

- Ajuste Científco 2da Parte UdemyDocumento23 páginasAjuste Científco 2da Parte UdemyJosue OrtizAún no hay calificaciones

- DiapositivasDocumento37 páginasDiapositivasDavidCPAún no hay calificaciones

- Unidad 3Documento22 páginasUnidad 3Guillen Jan Carlo0% (1)

- Lab 1 Convecional Vs ViwaDocumento3 páginasLab 1 Convecional Vs ViwaJefferson DefazAún no hay calificaciones

- Taller 1 de MecanismosDocumento2 páginasTaller 1 de MecanismostanainaAún no hay calificaciones

- Inversion de GrashofDocumento5 páginasInversion de GrashofLuis Angel Ortega MárquezAún no hay calificaciones

- Práctica 4Documento6 páginasPráctica 4Ramiro JanusAún no hay calificaciones

- SLC Lab 6Documento6 páginasSLC Lab 6davidvalenAún no hay calificaciones

- IEC61131Documento10 páginasIEC61131carlcoxAún no hay calificaciones

- TraccionDocumento19 páginasTraccionantonioAún no hay calificaciones

- Unidad 3 Circuitos HidraulicosDocumento20 páginasUnidad 3 Circuitos HidraulicosgacbvmAún no hay calificaciones

- Unidad 2 Sistemas de Manufactura FlexibleDocumento21 páginasUnidad 2 Sistemas de Manufactura FlexiblewaciAún no hay calificaciones

- Elementos Unidimensionales 1Documento47 páginasElementos Unidimensionales 1Andrés Edisson ÁguilaAún no hay calificaciones

- Analisis Cinematico Algebra ComplejaDocumento25 páginasAnalisis Cinematico Algebra ComplejaJhon SánchezAún no hay calificaciones

- Diagrama de Interconexión de RedDocumento3 páginasDiagrama de Interconexión de Redmilthon_carlos0% (1)

- Robot Sumo PDFDocumento10 páginasRobot Sumo PDFCarlos SánchezAún no hay calificaciones

- Practica de Eficiencia Del CompresorDocumento11 páginasPractica de Eficiencia Del CompresorIvan Gonzalez LaraAún no hay calificaciones

- Ciclo de PunteadoDocumento2 páginasCiclo de PunteadoAlex ChancúsigAún no hay calificaciones

- Circuito ElectroneumaticoDocumento6 páginasCircuito ElectroneumaticoRonaldo Chiche SurcoAún no hay calificaciones

- Juntas EmpernadasDocumento30 páginasJuntas EmpernadasMilagros Quispe PisconteAún no hay calificaciones

- CUESTIONARIODocumento4 páginasCUESTIONARIOAldo GuerraAún no hay calificaciones

- Cadena Cinematica2Documento2 páginasCadena Cinematica2Gianfranco Navarro TorrejonAún no hay calificaciones

- ElectroneumaticaDocumento6 páginasElectroneumaticaAndrezVasquezAún no hay calificaciones

- PDPIyPID COMPENSADORESDocumento56 páginasPDPIyPID COMPENSADORESPedro Tellez100% (1)

- Act. Aprendizaje Unidad 5Documento12 páginasAct. Aprendizaje Unidad 5Sinai RiveraAún no hay calificaciones

- Calculo de Velocidades de Piston y CaudalDocumento47 páginasCalculo de Velocidades de Piston y CaudalWalter Sarango0% (1)

- Disparo Lineal de TiristoresDocumento13 páginasDisparo Lineal de TiristoresRaul CarrilloAún no hay calificaciones

- Libro de Texto de MecanismosDocumento179 páginasLibro de Texto de MecanismosAlguien Por AkiAún no hay calificaciones

- Metodo D-H de Cinematica Directa-RoboticaDocumento9 páginasMetodo D-H de Cinematica Directa-RoboticaAnel Olivares CruzAún no hay calificaciones

- LAB4Documento4 páginasLAB4Jorge BorjaAún no hay calificaciones

- 01 Familias Compuertas LogicasDocumento5 páginas01 Familias Compuertas LogicasSergio Garcia HernandezAún no hay calificaciones

- Informe de Circuitos DigitalesDocumento16 páginasInforme de Circuitos DigitalesJudith MAAún no hay calificaciones

- Youtube 170211202901Documento19 páginasYoutube 170211202901Luis Armando Reyes CardosoAún no hay calificaciones

- Técnicas de Análisis de CD y CA PDFDocumento14 páginasTécnicas de Análisis de CD y CA PDFLuis Armando Reyes CardosoAún no hay calificaciones

- 1 Analisis y OsciloscopioDocumento9 páginas1 Analisis y Osciloscopioruiz_jeAún no hay calificaciones

- Técnicas de Análisis de CD y CA PDFDocumento22 páginasTécnicas de Análisis de CD y CA PDFLuis Armando Reyes CardosoAún no hay calificaciones

- AlgebraDocumento6 páginasAlgebraLuis Armando Reyes CardosoAún no hay calificaciones

- Guia CamtasiaDocumento29 páginasGuia CamtasiaElvira Berrospi CórdovaAún no hay calificaciones

- Gmailcontactshangouts 161127114040Documento46 páginasGmailcontactshangouts 161127114040Luis Armando Reyes CardosoAún no hay calificaciones

- Drive 161219203946Documento52 páginasDrive 161219203946Luis Armando Reyes CardosoAún no hay calificaciones

- GuiaVideoAccessible Sencera Cast PDFDocumento226 páginasGuiaVideoAccessible Sencera Cast PDFLuis Armando Reyes CardosoAún no hay calificaciones

- Classroom 160908160422Documento83 páginasClassroom 160908160422Mirene Ugarte100% (1)

- Pinza Amperimétrica de Verdadero Valor Eficaz de CADocumento6 páginasPinza Amperimétrica de Verdadero Valor Eficaz de CALuis Armando Reyes CardosoAún no hay calificaciones

- Cálculo Integral PDFDocumento15 páginasCálculo Integral PDFLuis Armando Reyes CardosoAún no hay calificaciones

- Técnicas de Análisis de CD y CA PDFDocumento14 páginasTécnicas de Análisis de CD y CA PDFLuis Armando Reyes CardosoAún no hay calificaciones

- Classroom 160908160422Documento30 páginasClassroom 160908160422Luis Armando Reyes CardosoAún no hay calificaciones

- Chrome 170111230038Documento33 páginasChrome 170111230038Luis Armando Reyes CardosoAún no hay calificaciones

- Técnicas de Análisis de CD y CA PDFDocumento14 páginasTécnicas de Análisis de CD y CA PDFLuis Armando Reyes CardosoAún no hay calificaciones

- Simbologia Iec 1Documento4 páginasSimbologia Iec 1Jackeline Roxana Huaman FernandezAún no hay calificaciones

- Tarifas Electricas 2001Documento2 páginasTarifas Electricas 2001Luis Armando Reyes CardosoAún no hay calificaciones

- La Rueda de La PedagogíaDocumento1 páginaLa Rueda de La PedagogíaAroldo NoriegaAún no hay calificaciones

- Rigidez DielectricaDocumento2 páginasRigidez DielectricaLuis Armando Reyes CardosoAún no hay calificaciones

- Tema04a.Aritmetica BinariaDocumento22 páginasTema04a.Aritmetica Binariarosemberg_trujilloAún no hay calificaciones

- PLDsDocumento20 páginasPLDsLuis Armando Reyes CardosoAún no hay calificaciones

- Fundamentos Del MaquinadoDocumento4 páginasFundamentos Del MaquinadoLuis Armando Reyes CardosoAún no hay calificaciones

- Electronica DigitalDocumento40 páginasElectronica DigitalIvannaKAún no hay calificaciones

- Tema02.Algebra de BooleDocumento66 páginasTema02.Algebra de BooleChristian Fonseca RodriguezAún no hay calificaciones

- Tema03.Circuitos Combinacionales PDFDocumento34 páginasTema03.Circuitos Combinacionales PDFAlan Cortés RamosAún no hay calificaciones

- Generalidades Redes IndustrialesDocumento58 páginasGeneralidades Redes IndustrialesChristian Ruben Corihuaman SotoAún no hay calificaciones

- Biodry HondurasDocumento2 páginasBiodry Hondurashector lopezAún no hay calificaciones

- Dialnet ConexionDeUnSistemaFotovoltaicoALaRedElectrica 4548810Documento6 páginasDialnet ConexionDeUnSistemaFotovoltaicoALaRedElectrica 4548810Ruben DavidAún no hay calificaciones

- Curso II Balanced ScorecardDocumento126 páginasCurso II Balanced Scorecardedwardvargasbengoa100% (1)

- Informe Dispositivos de Salida Entrada y AlmacenamientoDocumento2 páginasInforme Dispositivos de Salida Entrada y AlmacenamientosofiachachaAún no hay calificaciones

- El Transistor Como Interruptor PDFDocumento3 páginasEl Transistor Como Interruptor PDFaledangieAún no hay calificaciones

- Sist - Engrase DMM3Documento15 páginasSist - Engrase DMM3Edison CortesAún no hay calificaciones

- catalogo-SE-EQM Soft ExpertDocumento4 páginascatalogo-SE-EQM Soft ExpertClaudio Cruz RodríguezAún no hay calificaciones

- Críticas Al Paradigma de La Complejidad de Edgar Morin PDFDocumento18 páginasCríticas Al Paradigma de La Complejidad de Edgar Morin PDFfvaladez14Aún no hay calificaciones

- Estadistica Basica para IngenierosDocumento178 páginasEstadistica Basica para Ingenierosmjvn31Aún no hay calificaciones

- 15 - Modulo DROUTINGDocumento14 páginas15 - Modulo DROUTINGEdgar A CanizalezAún no hay calificaciones

- Hernandez 2Documento8 páginasHernandez 2Rodriguez JoseAún no hay calificaciones

- 1.3 - Seguridad (Normativa Básica)Documento9 páginas1.3 - Seguridad (Normativa Básica)María IsabelAún no hay calificaciones

- El Transistor BipolarDocumento30 páginasEl Transistor BipolarGio srzAún no hay calificaciones

- BackBox - Grupo 2Documento13 páginasBackBox - Grupo 2DAVID ALEJANDRO SILVA GUTIERREZAún no hay calificaciones

- Linea de Bancolombia en El Exterior - Google Search PDFDocumento1 páginaLinea de Bancolombia en El Exterior - Google Search PDFCarolina GutierrezAún no hay calificaciones

- FORMULARIODocumento4 páginasFORMULARIOLuis RubianoAún no hay calificaciones

- TESIS Rev.5 1Documento21 páginasTESIS Rev.5 1jvsv11100% (1)

- Estructura Del Informe de Auditoria OKDocumento24 páginasEstructura Del Informe de Auditoria OKMarco RamirezAún no hay calificaciones

- SIG PreguntasDocumento2 páginasSIG PreguntasHugo Oyola CortezAún no hay calificaciones

- Elk PDFDocumento2 páginasElk PDFTeufelCrazyAún no hay calificaciones

- Nuevas Tics 03Documento216 páginasNuevas Tics 03joto6693828100% (2)

- Cromatografo de Gases Ficha TecnicaDocumento54 páginasCromatografo de Gases Ficha Tecnicajavierpenagos92Aún no hay calificaciones

- Funciones de Jefe de Oficina BienestarDocumento4 páginasFunciones de Jefe de Oficina BienestarChristian AndrewAún no hay calificaciones

- Sistemas de Transporte Hospitalario - Módulo 1 - Sistemas de Transporte HospitalarioDocumento32 páginasSistemas de Transporte Hospitalario - Módulo 1 - Sistemas de Transporte HospitalarioGato RiosAún no hay calificaciones

- Luis Arias - Trabajo de Investigacion - Bachiller - 2019Documento62 páginasLuis Arias - Trabajo de Investigacion - Bachiller - 2019Edwin ReinosoAún no hay calificaciones

- Evidencia Caso de Estudio Pruebas de SoftwareDocumento20 páginasEvidencia Caso de Estudio Pruebas de Softwareleydi yohana sua niñoAún no hay calificaciones

- Dialnet DesarrolloYAprendizajeDelConocimientoEspacial 1317473Documento33 páginasDialnet DesarrolloYAprendizajeDelConocimientoEspacial 1317473gsolaresAún no hay calificaciones