Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Mult Iee 2 F

Cargado por

Daniel AvendañoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Mult Iee 2 F

Cargado por

Daniel AvendañoCopyright:

Formatos disponibles

1

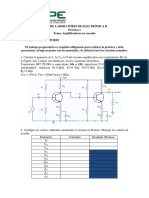

Amplicadores Multietapa

R. Carrillo, J.I. Huircan

Abstract Los amplicadores multieetapa son circuitos

electrnicos formados por varios transistores (BJT o FET),

que pueden ser acoplados en forma directa o mediante capacitores. Las conguraciones clsicas son el par Darlington

(alta impedancia de entrada e incremento de la gnancia de

corriente), el par diferencial (Relacin de rechazo en modo

comn elevada), el amplicador cascode (alta impedancia

de salida). Todas estas etapas amplicadoras pueden ser

integradas y encapsuladas en un chip semiconductor llamado Circuito Integrado (CI). En el CI las polarizacin de

las etapas se hace usando fuentes de corriente, debido a la

mayor facilidad de construccin (a travs de transistores).

La combinacin de distintas tecnologas permitir mejorar

la prestacin de los sistemas diseados.

Index Terms Amplicadores, Multietapas, BiCmos

Vcc

Vcc

RC

R1

Q1

v

i

RC

Q2

vo

R2

RE

1

RE

RB

V

BB

Q1

Vcc

Q2

RE

1

RE

(b)

(a)

Fig. 2. Transistores acoplados directamente.

I. Introduction

Un amplicador se describe un circuito capaz de procesar

las seales de acuerdo a la naturaleza de su aplicacin. El

amplicador sabr extraer la informacin de toda seal, de

tal manera que permita mantener o mejorar la prestacin

del sistema que genera la seal (sensor o transductor usado

para la aplicacin).

Se llama amplicador multietapa a los circuitos o sistemas que tienen mltiples transistores y adems pueden

ser conectadas entre s para mejorar sus respuestas tanto

en ganancia, Zin , Zout o ancho de banda. La aplicaciones

pueden ser tanto de cc como de ca.

El acoplamiento establece la forma en la cual se conectan

las distintas etapas amplicadores, dependiendo de la naturaleza de la aplicacin y las caractersticas de respuesta

que se desean. Existen distintos tipos de acoplamiento:

Acoplamiento directo, capacitivo y por transformador.

Vcc

Etapa

Etapa

Acopl.

Etapa

Acopl.

As

IB2 =

VCC

VBE2 IC1 RC

IC

= 2

( + 1) RE2

v

o

3

RL

Fig. 1. Acoplamiento.

A. Acoplamiento directo

Las etapas se conectan en forma directa, es permite una

amplicacin tanto de la componente de seal como de la

componente continua del circuito. Se dice que los circuitos

de cc se acoplan directamente. La Fig. 2 muestra una

aplicacin de acoplamiento directo.

En corriente continua se tiene

UFRO. DIE. Material preparado para la asignatura de Circuitos

Electrnicos I. Ver 3.5.

(3)

Dado que la malla de entrada ser

+1

VBB = IB1 RB + VBE1 + IC1

II. Tipos de acoplamiento

v

i

RC (IB2 + IC1 ) + VBE2 + IE2 RE2 = VCC

(1)

IE2 = IB2 ( + 1) (2)

RE1

(4)

Entonces

IC1 =

VBB

RB

+ VBE1 +

+1

(5)

RE1

De esta forma se determinan VCEQ1 y VCEQ2 . Note que

al hacer anlisis en cc, los efectos de la polarizacin de una

etapa afectan a la otra.

Por otro lado, realizando el analisis en ca se tiene

vo = (1 + hf e ) ib2 RE2

(hf e ib1 + ib2 ) RC = ib2 hie + vo

vi = ib1 (hie + (1 + hf e ) RE1 )

(6)

(7)

(8)

De esta forma despejando ib2 de (7) y reemplazando en

(6)

vo = (1 + hf e )

hf e ib1 RC vo

RE2

(hie + RC )

hf e RC RE2 (1 + hf e )

vo

=

vi

(hie + RC ) 1 +

(1+hf e )

(hie +RC ) RE2

(hie + (1 + hf e ) RE1 )

El efecto de los elementos de la primera y segunda etapa

estn presentes en la ganancia del sistema.

B. Acoplamiento capacitivo

El acoplamiento capacitivo o por condensador se usa

para interconectar distintas etapas, en las cuales slo se desea amplicar seal. La presencia del capacitor anula las

componentes de cc, permitiendo slo la amplicacin de

seales en ca. Los amplicadores de ca usan acoplamiento

capacitivo. Permite mayor libertad en el diseo, pues la

polarizacin de una etapa no afectar a la otra.

v

i1

vo

1

v

i2

v

o2

v

i2

v

o3

hfe i b

1

h ie

ib

1

+

v

i

vo

RE

RC

Fig. 5. Etapa emisor comun en ca.

vo

Etapa

Etapa

Etapa

v

i

En ca alterna analizando cada etapa por separado se

tiene, para la etapa 1 se determina la ganancia de voltaje.

Planteando las ecuaciones en el circuito de la Fig. 5.

RL

vo1 =

hf e ib1 RC

ib1

vi =

hie + RE (1 + hf e )

Fig. 3. Acoplamiento Capacitivo.

Extendiendo el sistema de la Fig. 3 a n-etapas, considerando la relacin de ganancia de cada una de llas se

tiene que la ganancia del sistema ser

Av =

vo

=

vi

von

vin

:::

vo1

vi1

vi1

vi

Luego se tiene que

vo1

hf e R C

=

vi

hie + RE (1 + hf e )

= 2:415

Av1 =

(9)

Considere amplicador emisor comn (sin CE ), de dos

etapas de la Fig. 4, donde R1 = 3 [K ], R2 = 1 [K ],

RE = 820 [ ], RC = 2 [K ] ; VCC = 10 [V ] : Por otro lado,

hf e = 100, hie pequeo.

o

La cual ser la misma de la etapa 2, Av2 = vvo1

= 2:4;

de acuerdo a (9) se tiene que la ganancia total del sistema

ser

V

CC

RC

RC

R1

C

C

C i

v

i

R1

Cc

R2

RE

h fe i

h ie

vo

b1

h fe i b2

h ie

vo

R2

AvT = Av1 Av2 = 5:83

vi

b1

RE

RE

RE

b2

RC

RC R1 R2

Fig. 4. Amplicador con etapas en cascada.

Fig. 6. Amplicador en ca.

Note que en cc ambas etapas quedan separadas, formarn un circuito de polarizacin universal, de esta forma

el punto de operacin para cada etapa ser

Sin embargo, si se toma el amplicador completo de

acuerdo a la Fig. 6, se tiene

R2

1 [K ]

= 10 [V ]

= 2:5 [V ]

R 1 + R2

3 [K ] + 1 [K ]

= R1 jjR2 = 3 [K ] jj1 [K ] = 750 [ ]

VT H = VCC

RT H

iC =

VT H

RT H

VBE

2:5 [V ] 0:7 [V ]

=

+1

7:5 + 1:01 820

RE

vo =

ib2 =

ib1 =

RC hf e ib2

1

hie +RE (1+hf e )

hf e ib1

1

1

hie +RE (1+hf e ) + R1 jjR2 jjRC

vi

hie + RE (1 + hf e )

De esta forma se tiene

= 2:15 [mA]

vCE = VCC

iC

RC +

+1

RE

=

Av =

= 10

(200 + 1:01 820) (2:15 [mA]) = 7:78 [V ]

vo

= R C hf e hf e @

vi

1

1

hie +RE (1+hf e )

h +RE (1+hf e )

+ ieR1 jjR

2 jjRC

1

A

AMPLIFICADORES MULTIETAPA

Considerando los datos, con hie ! 0

V

CC

Av = 1:58

Por qu dieren los dos clculos realizados?

Esto ocurre por el efecto de carga que representa la

segunda etapa al ser conectada a la primera. Desde el

punto de vista de seal, la primera etapa tiene una impedancia de salida Rsal = RC , dado que su ganancia ser

2:4, el amplicador visto desde la salida es una fuente

de voltaje controlado por voltaje. Por otro lado, la segunda etapa desde el punto de vista de la entrada, tiene

una Rin = R1 jjR2 jj (hie + (1 + hf e ) RE ) :

RC

+

vi

Av 1 vi

vo1

R1 R2

h ie

i

h fe i b2

b2

vo

RC

Rin

RL

R1

Q1

v

i

R2

RE

III. Configuracion Darlington

Esta conguracin corresponde a dos etapas seguidores

de emisor, tiene una alta impedancia de entrada y adems

produce un efecto multiplicativo sobre la corriente, se

conoce adems como par Darlington.

Vcc

RE (1 + hfe )

RB

R1 jjR2 jj (hie + (1 + hf e ) RE )

vi

R1 jjR2 jj (hie + (1 + hf e ) RE ) + RC

750 [ ] jj (101 820 [ ])

vi

2:4

750 [ ] jj (101 820 [ ]) + 2 [K ]

743 [ ]

2:415

= ( 2:415) 0:271vi

743 [ ] + 2 [K ]

Ci

IC

1

IB

1

Note que sin conectar la segunda etapa, la salida de la

primera ser vo1 = Av1 vi : Al conectar la segunda etapa al

amplicador, se produce un divisor de voltaje

v

i

(a)

vo

(b)

Fig. 9. (a) Conguracin Darlington. (b) Seguidor de emisor.

A. Anlisis en cc

Sea el circuito de la Fig. 10, en cc.

Vcc

Vcc

Por lo tanto, se debe considerar el efecto de carga que

representa la segunda etapa respecto de la primera.

Co

RE

IE

2

B2

Asi, la ganancia de la primera etapa considerando el

efecto de carga ser Av1 = vvo1i = ( 2:415) 0:271. Luego la

ganancia total del sistema

vo

= Av1 Av2

vi

vo1 vo

=

vi vo1

= ( 2:415) 0:27 ( 2:415)

= 1:58

IC

2

vo1 = Av1

CE

Fig. 8. Amplicador con carga acoplada por transformador.

Fig. 7. Amplicador completo en ca.

IC

1

RB

IB

1

IC

2

Q1

I

Q2

IE

2

B2

RE

Fig. 10. Par Darlington en cc.

Planteando la ecuacin en la malla de entrada

C. Acoplamiento por transfomador

Este acoplamiento es muy popular en el dominio de la

radio frecuencia (RF). El transformador como carga permitir aislar las seales y adems, dependiendo de la razn

de transformacin incrementar el voltaje y corriente.

En el circuito de la Fig. 8, la carga es alimentada a travs

de un transformador, la relacin de voltajes estar dada

2

por vv12 = N

N1 ; donde el segundo trmino es la relacin de

inversa de transformacin. Los transformadores permiten

aislar elctricamente las distintas etapas.

VCC = IB1 RB + VBE1 + VBE2 + IE2 RE

(10)

Pero

IB1 + IC1 = IB2 = (

Adems, dado que IE2 = (

VBE1 = VBE2 = VBE

IB1 =

+ 1) IB1

(11)

+ 1) IB2 y considerando

VCC 2VBE

RB + ( 1 + 1) ( 2 + 1) RE2

(12)

Calculando la corriente de colector total, IC2 , se tiene

IE2 = (

( + 1)

IC2 2

= (

2 + 1) (

2

+ 1) (

vi = ib1 hie1 + ib1 (hf e1 + 1) hie2 + vo

vo = ib1 (hf e1 + 1) (1 + hf e2 ) RE

1 + 1) IB1

1

+ 1) IB1

(13)

As

IC2 =

+ 1) IB1

(14)

Lo que determina el efecto multiplicativo en la corriente.

B. Anlisis en ca

h fe i b

Q1

R

ib

Q2

v

B

R

Luego

vi = ib1 fhie1 + (hf e1 + 1) hie2 + (hf e1 + 1) (1 + hf e2 ) RE g

(23)

Finalmente como Zin = ivbi

1

Zin = hie1 + (hf e1 + 1) (hie2 + (1 + hf e2 ) RE )

El circuito en ca de la Fig. 11a, se usar para determinar

las ganancias Av , Ai y la impedancia de entrada.

v

i

(21)

(22)

vo

ib

h ie

h fe i b

ib (1 + hf e2 )

io

= 2

ii

ib1

ib1 (1 + hf e1 ) (1 + hf e2 )

=

ib1

= (1 + hf e1 ) (1 + hf e2 )

Ai =

vo

R

(a)

Resulta ser un valor bastante grande si hf e1 ; hf e2 >> 1.

Clculo de Ai .

Dado que io = ib2 (1 + hf e2 ) e ib2 = ib1 (1 + hf e1 )

h ie

E

(b)

(24)

(25)

Donde (20) es factor multiplicativo de la seal de corriente.

Fig. 11. Amplicador Darlington en ca.

IV. Circuitos Cascode

Determinacin de Av .

Usando el equivalente a pequea seal de la Fig. 11b, se

plantean las ecuaciones de Kirccho

vi = ib1 hie1 + ib2 hie2 + vo

vo = ib2 (1 + hf e2 ) RE

(15)

(16)

Consiste en un amplicador en emisor comn acoplado

directamente con una conguracin en base comn. Dicho

circuito posee una impedancia de salida mayor y un ancho

de banda ms grande. El anlisis en ca, se realiza usando

el circuito equivalente de la Fig. 13.

Vcc

Pero ib2 = (hf e1 + 1) ib1

R3

RC

v

o

vi = ib1 hie1 + ib1 (hf e1 + 1) hie2 + vo

vo = ib1 (hf e1 + 1) (1 + hf e2 ) RE

(17)

(18)

CB

R1

v

Luego

RB

R2

RE

vo =

RC

vi vo

hie1 + (hf e1 + 1) hie2

(hf e1 + 1) (1 + hf e2 ) RE

CE

(b)

(a)

Fig. 12. (a) Amplicador Cascode. (b) Equivalente en ca.

vo

(hf e1 + 1) (1 + hf e2 ) RE

=

vi

hie1 + (hf e1 + 1) hie2 + (hf e1 + 1) (1 + hf e2 ) RE

(19)

Si hf e1 ; hf e2 >> 1, se comporta como seguidor de emisor.

vo

=

vi

RE

hie1 +(hf e1 +1)hie2

(hf e1 +1)(1+hf e2 )

Clculo de Zin .

+ RE

=1

(20)

Planteando la LVK en la salida

vo = RC (ib hf e )

hf e ib1 = ib (1 + hf e )

vi = ib1 hie

Finalmente se tiene

(26)

(27)

(28)

AMPLIFICADORES MULTIETAPA

ib

hfe i

hie

hfe i

v

i

RB

A. Conguracin del Amplicador Diferencial

v

o

El circuito de la Fig. 15 es un amplicador diferencial

transistorizado, tambin llamado par diferencial, donde la

variable vo es la salida y los terminales vi1 y vi2 son la

entrada. Considerando que los parmetros de circuito y

los transistores son idnticos, el voltaje aplicado a cada

uno de los terminales de entrada es el mismo, vo ser nulo.

Esto se conoce como circuito balanceado.

RC

b1

i b1

hie

Fig. 13. Modelo a pequea seal.

Vcc

RC

RC

vo

=

vi

RC h2f e

(hf e + 1) hie

v

+ o _

vo

1

(29)

Q1

v

i1

La resistencia de salida Rout , estar dada por RC .

Se dene as al sistema indicado en la Fig. 14, el cual

es una conguracin cuya seal de salida corresponde a la

diferencia entre dos seales de entrada.

v

i2

Amplificador

Diferencial

+

v

o

_

Q2

v

i2

RE

V. Amplificador diferencial

v

i1

vo

2

v

o1

-VEE

Fig. 15. Amplicador diferencial con transistores.

A.1 Anlisis en corriente continua

v

o2

Planteando la LVK en la malla de entrada

Fig. 14. Amplicador diferencial.

VBE1

En un amplicador ideal se debe cumplir que

VBE1 + IE RE

+ (IE1 + IE2 ) RE

VEE = 0

VEE = 0

(34)

Como ambos transistores son iguales se tiene que

vo1 = Ad (vi1 vi2 )

vo2 = Ad (vi1 vi2 )

(30)

(31)

Si la salida se considera como vo = vo1 vo2 , se dice

que corresponde a la salida balanceada, en cambio si vo =

vo1 ( vo = vo2 ), sta ser la salida asimtrica. En un

amplicador diferencial real se tiene

vo1 = Ad (vi2

vi1 ) + Ac

vi2 + vi1

2

(32)

Donde Ad es la ganancia diferencial y Ac es la ganancia

en modo comn.

El amplicador slo responder a la entrada diferencial si Ad >> Ac . Se dene as la relacin de rechazo

en modo comn (RRMC CMRR- Common Mode Reject

Rate) dada por el cociente

VBE1 + 2IE1 RE = VEE

(35)

Pero como IB1 + IC1 = IE1 = ( + 1) IB1 , se tiene que

IB1 =

VEE VBE1

2RE ( + 1)

(36)

En la prctica IE debe ser independiente de los transistores y de valor constante, tambin se desear que RE

sea lo ms grande posible, de esta forma el RRMC tendr

un valor alto y el amplicador tendr una respuesta ms

prxima a la ideal.

A.2 Anlisis en corriente alterna

Determinacin de la ganancia diferencial

Sea la salida vo2 , de acuerdo a la Fig. 16b, as

vo2 =

hf e ib2 Rc

Pero en la entrada

CM RR =

Ad

Ac

(33)

Esta relacin mide la calidad del amplicador diferencial, debido a que permite saber en que factor se atenua la

seal en modo comn, respecto de la seal diferencial.

vi1 = ib1 hie + iE RE

vi2 = ib2 hie + iE RE

Por otro lado

(37)

(38)

vo

1

v

i 1

RC

RC

RC

vo

2

Q

v

i2

h fe i b

h fe i b

(44)

Considerando que ib1 = ib2 = ib , entonces

RC

v

RE

i1

ib

hie

hie

ib

(a)

Fig. 16.

seal.

ib1 + hf e ib1 + ib2 + hf e ib2 = iE

(hf e + 1) (ib1 + ib2 ) = iE

vo

v

2

i2

vi = ib hie + iE RE

(hf e + 1) 2ib = iE RE

(b)

(45)

Finalmente

(a) Amp. diferencial en ca. (a) Equivalente a pequea

hf e R c

hie + 2RE (hf e + 1)

vo2

=

vi

Ac =

(46)

Determinacin de la RRMC

RRM C =

ib1 + hf e ib1 + ib2 + hf e ib2 = iE

ib1 =

ib2 +

iE

(39)

(1 + hf e )

Donde vi = vi2

ib1

VI. Amplificador diferencial con fuentes de

corriente

(40)

vi1 , entonces

vi = (ib2 ib1 ) hie

= 2ib2 hie

Considerando que los transistores Q1 y Q2 del circuito

de la Fig. 10 deben estar polarizados en cc, el valor de RE

debe ser limitado. Si RE se incrementa, el valor de VEE ,

tambin debe ser incrementado, para mantener la misma

corriente de polarizacin en los dos transistores.

Esto implica que el incremento de RE no es posible sin

un incremento en la tensin de polarizacin ( VEE ), luego,

el circuito descrito se modica usando una fuente de corriente constante ideal. Esto proveer una corriente de polarizacin constante para Q1 y Q2 y una resistencia innita

entre los dos emisores y tierra.

En trminos prcticos, la implementacin tpica de la

fuente de corriente puede ser en base a un transistor como

se indica en la Fig. 18a.

(41)

Finalmente, la ganancia diferencial Ad ser

Ad =

vo2

=

vi

hf e R c

2hie

(42)

Ganancia en modo comn

Considerando el circuito de la Fig. 17b.

RC

RC

vo

2

v

ic

RC

ib

vi

h fe i

b

vo

ib

RE

Vcc

hie

h fe i b

hie

R

RC

Vcc

RC

RC

v

i1

v

i2

RB

IE

vo

2

v

i1

IE

Fig. 17. (a) Amplicador en modo comn. (b) Circuito equivalente.

v

Sea vi = vi1 = vi2 , luego se tiene que Ac = voi2

Dado que vo2 = hf e ib2 Rc ; planteando la LVK en la

entrada

vi = ib1 hie + iE RE

(b)

(a)

RC

vo

2

RC

(43)

(47)

Se observa que si RE ! 1; el CMRR se hace muy

grande por lo tanto la componente en modo comn se

atenua, haciendo su comportamiento ideal.

Sea hf e >> 1, se despeja ib2 en funcin de ib1 , se tiene

ib2 =

Ad

hie + 2RE (hf e + 1)

=

Ac

2hie

RE

-V EE

-V EE

Fig. 18. (a)Fuente de corriente prctica. (b) Esquema.

Dado que IE = IC3 , se tiene que

v

i2

AMPLIFICADORES MULTIETAPA

RB3 IB3 + VBE3 + IE3 RE = VEE

(48)

Analizando en ca, el circuito en pequea seal queda,

luego, se puede determinar la relacin vo =vi .

(49)

vi = ib (RB + hie1 ) + ib (1 + hf e1 ) RE + vo

ic1 = ib2 hf e2

Como IE3 = ( + 1) IB3 se tiene

IB3 =

VEE VBE3

RB3 + ( + 1) RE

ib2 = ib2 hf e2 R1 jjR2 + RE

Por lo tanto

IE3 = ( + 1)

(50)

vo = vi

Seleccionando un RB3 adecuado se tiene que

IE3 =

(51)

RE

VII. Circuitos desplazadores de nivel

Como los amplicadores producen tensiones de cc en

la salida, an si la entrada tiene valor medio cero, la salida tiene una tensin distinta de cero, debido a efectos de

polarizacin (son desplazamientos indeseados).

Los trasladores de nivel son amplicadores que suman o

restan de la entrada una tensin desconocida, para compensar la tensin de desplazamiento en la entrada. Este

circuito funciona como ganancia unitaria para ca y a la

vez proporciona una salida ajustable para cc.

La Fig. 19a, muestra un circuito desplazador de nivel el

cual se encuentra polarizado por fuente de corriente.

Vcc

v

i

RB

+

V

BB

VIII. Amplificadores diferenciales Integrados

A. Fuentes de corriente en la polarizacin de circuitos integrados

Los circuitos de polarizacin analizados con 4 resistores,

son adecuados para los circuitos discretos. Sin embargo,

en los circuitos integrados los resistores consumen un rea

excesiva del chip, por lo que se deben usar otros mtodos

para la polarizacin.

Usando transistores y pocos resistores es posible implementar fuentes de corriente para polarizar los amplicadores integrados.

Example 1: Sea el circuito de la Fig. 20, considerando

Q1 y Q2 idnticos (no ocurre as para circuitos discretos)

15[V]

v

i

Q3

vo

Q1

Q2

+

VBB

RE

2[mA]

RE

vo

R1

-V

EE

Q

R2

(a)

Fig. 20. Amplicador diferencial polarizado por fuente de corriente.

,

RE

IE1 + IE2 = 2 [mA]

IE1 = IE2 = 1 [mA]

-V

EE

(b)

Luego

Fig. 19. (a) Desplazador de nivel. (b) Implementacin.

IC1 = IC2

VBB = IB RB + VBE + IE RE + Vo

(52)

Luego

RB IC

IE2

= 9:9 [ A]

+1

= 0:99 [mA]

IB1 = IB2 =

En corriente contnua se tiene

Vo = VBB

5 [mA]

RC

Vcc

(57)

Dando el comportamiento como seguidor de emisor.

VBE3

Note que IE es constante y RE no necesariamente es

elevada.

RB

(56)

Luego ib2 = 0, as ic1 = 0, ib = 0, entonces

VEE VBE3

RB3 + ( + 1) RE

VEE

(54)

(55)

IC RE

VBE

(53)

Seleccionando RE , Vo se puede colocar en cualquier nivel

de cc menor que VBB VBE .

Si se desea desplazamiento positivo, se puede usar un

circuito similar con un transitor pnp.

Si

IE3 = 5 [mA]

IE3

IB3 =

= 49:5 [ A]

+1

As la corriente por el resistor de 5 [K ] ser

I = IC2 IB3

= 0:99 [mA]

49:5 [ A] = 0:94 [mA]

Planteando la ecuacin en la salida

iC

2

1

m= r

o

15[V ] + VBE2 = VCE1 + I 5 [K ]

VCE1 = 10:99 [V ]

M argen de trabajo

Por otro lado para Q3 se tiene

I 5 [K ]

v CE

0:7 [V ] = 15 [V ] VE3

VE3 = 10:99 [V ]

Fig. 22. Margen de trabajo.

Vcc

Note que los transistores estn en zona activa.

Vcc

B. Espejos de Corriente

Vcc

vi

10K

Una forma simple de implementar fuentes de corriente

para los circuitos integrados son los espejos de corriente,

los cuales permiten a partir de una corriente de referencia

(Iref ), generar mltiples fuentes de corriente.

vi

vo

vo

RL

Q

I BIAS

RL

-VEE

-VEE

Vcc

I ref

Fig. 23. Seguidor de emisor polarizado por corriente.

R

IC

Q1

I ref = I C 2

Example 2: Un circuito seguidor de emisor polarizado

por una fuente de corriente se muestra en la Fig. 23.

Para cc se tiene que

Q2

Fig. 21. Espejo de corriente.

IBIAS = IC2 =

El circuito bsico se muestra en la Fig. 21. Considerando

los transistores iguales, por ende las tensiones VBE iguales,

se tiene que IB1 = IB2 : ; luego

IC1 = IC2 = IB1

(58)

Como

Iref = IC1 + IB1 + IB2 = IC1 +

= IC1 + IC1

= IC1

1+

IC1

VCC

VBE + VEE

10 [K ]

(61)

Para ca se tendr que vi = vo , sin embargo, debido a que

est acoplado directamente, puede considerarse la cada de

voltaje de 0:7 [V ] :

Como para el voltaje de entrada cero, la salida vo =

0:7 [V ] ; se plantea la opcin de la Fig. 24.

Vcc

Vcc

IC2

I2

Q

vo

Q2

RL

I1

-VEE

Finalmente

IC1 = IC2 =

Iref

1+

Fig. 24. Modicacin de la polarizacin del seguido de emisor.

(59)

En cc se tiene que

Para >> 1; se tiene que IC1 = IC2 = Iref :

Debido que IC1 = IC2 el circuito se llama espejo de corriente e Iref es la corriente de referencia. Luego

VBE

(60)

R

Esta fuente de corriente posee un margen de trabajo, el

cual est delimitado de acuerdo a la curva del transistor

que se muestra en la Fig. 22. Se observa qure la pendiente

de la curva est dada por el inverso ro (resistencia de salida

del transistor). En condiciones ideales ro ! 1:

Iref =

Vcc

VBE1 = VBE2 + VE2

Por lo tanto vo = VE2 = VBE1

En ca

(62)

VBE2 = 0

vo = (1 + hf e2 ) ib2 RL

ib2 = ib1 (1 + hf e1 )

vi = ib1 (hie1 + hie2 ) + vo

(63)

(64)

(65)

AMPLIFICADORES MULTIETAPA

As

vo

vo = (1 + hf e2 ) (1 + hf e1 ) RL

(hie1 + hie2 )

0

1

= @

=

(1+hf e2 )(1+hf e1 )RL

(hie1 +hie2 )

(1+hf e2 )(1+hf e1 )RL

+

(hie1 +hie2 )

1

(1+hf e2 )(1+hf e1 )RL

+1

VT

ln

R2 =

IE

(66)

B.1 Espejo de corriente de Wilson

El circuito de la Fig. 25 se conoce como fuente de corriente Wilson.

Vcc

Iref

IC

R

Q

IC

2

= IE2 R2 ;

Iref =

Vcc

IC1

IC2

VBE1

(71)

= IC1

R1

(72)

C. Polarizacin de Amplicadores mediante mltiples

fuentes de corriente

Cuando se requiere polarizar varias etapas en un circuito

integrado, se puede reproducir el efecto de la corriente de

referencia conectando un tercer transistor en el espejo de

corriente, en la base de Q2 , lo cual se podra extender a un

nmero limitado de transistores.

Vcc

I ref = I C

2

Q

IC

1

luego

vi

= vi

(70)

Entonces de (69) y (70), se tiene VT ln

A vi

IC

IS

VBE = VT ln

vi

I ref

R

IC

IC

Fig. 25. Espejo de corriente de Wilson.

(a)

Para esta fuente de corriente se tiene que

IC2 =

Considerando

2

+2 +2

Iref

Fig. 27. (a) Incremento de fuentes de corriente. (b) Duplicador de

corriente de referencia.

(67)

>> 1, entonces, IC2 = Iref ; donde

Iref =

Vcc

VBE2

R

VBE3

(68)

B.2 Espejo de corriente de Widlar

Tambin es posible generar una corriente cuyo valor sea

el doble o el triple de la corriente de referencia, lo cual se

logra duplicando (o triplicando) el rea de la juntura de

transistor y resulta equivalente a tener dos (o tres) transitores conectados en paralelo. El circuito de la Fig. 28,

indica un esquema de polarizacin para mltiples etapas.

El circuito de la Fig. 26 se conoce como espejo de corriente de Widlar.

Vcc

Vcc

I ref

IC

R1

(b)

Q

1

I1

2

I ref

I3

R

I

I4

R2

-V

EE

Fig. 28. Polarizacin para mltiples etapas.

Fig. 26. Espejo de corriente de Widlar.

Para esto se tiene

Planteando la LVK, se tiene

VEB1 VBE2

R

Para esta situacin se tiene que I1 = I2 = Iref , I3 =

2Iref , I4 = 3Iref .

Iref =

VBE1 = VBE2 + IE R2

Como

(69)

VCC

VEE

10

Finalmente

D. Amplicadores diferenciales con carga activa

Cuando se requiere una mejora en la ganancia del amplicador diferencial, se sustituyen las resistencias de colector

por una carga activa, como se muestra en la Fig. 29.

IX. Amplificador diferencial con FET

vo

Q

v

i1

hf e

2hie

1

hoe

Esto implica que si la resistencia de salida del transistor

Q4 es grande, se incrementa la ganancia.

Vcc

Q3

Ad =

El amplicador diferencial puede ser implementado con

FET, en el circuito de la Fig.31, se han usado MOSFET

canal n (nMOS).

v

i2

IE

VDD

-V EE

RD

RD

vo

Fig. 29. Amplicador diferencial con carga Activa.

vi

Q2

Q

1

Considerando que la ganancia diferencial dada por (42)

depende de RC , un incremento en dicha resistencia (como

sera sustituir RC por h1oe ) incrementara la ganancia.

Anlisis en ca

vi

2

-VSS

Fig. 31. Amplicador diferencial nMOS.

Q3

1

hoe

hfe i b3

ib3

i b4

hie

hie

hfe i b4

1

hoe

vo

2

v

i1

vo

hfe i b1

v

i2

hfe i b2

hie

v

i1

(a)

hie

i b2

i b1

v

i2

v

i

1

vo2 = (hf e ib4 hf e ib2 )

(73)

hoe

Por LCK se tiene, ib4 + hf e ib3 + ib3 + ib3 hie hoe = hf e ib1 :

Como ib4 hie = ib3 hie , entonces, ib4 = ib3 : Dado que

(1 + hf e ) ib1 + (1 + hf e ) ib2 = 0; entonces, ib1 = ib2 :

Planteando la LVK en la malla de entrada se tiene

vi1 = ib1 hie ib2 hie + vi2

vi1 vi2

vi

vi1

ib2 =

= 2

2hie

2hie

(74)

(75)

fe

; as, reemPero se tiene que ib4 = ib2 2+hf e +h

ie hoe

plazando la corriente en (73)

hf e

ib2

hf e

2 + hf e + hie hoe

hoe

2 + 2hf e + hie hoe hf e ib2

1

' hf e

2 + hf e + hie hoe

hoe

hoe

RD

RD

vo

Reemplazando los modelos de los transistores de acuerdo

a la Fig. 30b, sea la resistencia de salida h1oe , Q1 = Q2 y

Q3 = Q4 , se tiene que

RD

RD

(b)

Fig. 30. (a) En ca. (b) Circuito equivalente.

vo2 =

Este conguracin mejora la impedancia de entrada, sto

debido a la resistencia de entrada del transistor nMOS.

Anlisis en ca

v

i

v

i

v+

gs1

_

g v

m

g v

m

gs2

gs1

vo

+

v

_gs2

v

i

(b)

(a)

Fig. 32. (a) Diferencial en ca. (b) Equivalente.

De la Fig. 32a, se tiene

vo =

RD gm vgs2

Planteando una LVK en la entrada

vi1 = vgs1

vgs2 + vi2

Luego por LCK se tiene que gm vgs1 + gm vgs2 = 0; lo que

implica que vgs1 = vgs2 ; as, vi1 vi2 = vgs1 vgs2 =

2vgs2 :Deniendo vi = vi2 vi1 ; se tiene

vo

=

vi

RD gm

2

A. Espejos de corriente con transistores nMOS

hf e

vi1 vi2

2hie

Estos circuitos permiten polarizar las distintas etapas

amplicadoras. Como se muestra en la Fig. 33a, se tiene

que para cada transistor nMOS

AMPLIFICADORES MULTIETAPA

11

V

DD

I ref

Io

Io

Q1

Q2

Q3

Q

2

vi

BIA S

-VSS

(a)

RL

vo

Q

2

Q

1

(a)

-VSS

Q2

I

BIAS

Q

3

Q

4

Q

1

Io

I ref

VDD

IREF

V

CC

VDD

(b)

(b)

vi

-VSS

vi

vo

Fig. 33. (a) Espejo de corriente nMOS. (b) Espejos alternativos.

gmv

GS

v

GS

ib

(c)

(76)

h ib

fe

vo

RL

iD = K (vGS VT )

1 0W

2

= k

(vGS VT )

2 L

h

ie

RL

(d)

Fig. 34. (a) Amplicador Darlington BiCMOS. (b) Aplicacin. (c)

En ca. (d) A pequea seal.

Para el circuito mostrado

ID1 = Iref =

VDD

VGS

(77)

De acuerdo a la ecuacin (76), se determinan Io e ID1 .

1 0

k

2

1 0

Io = k

2

ID1 =

W

L

W

L

(78)

(79)

(vGS

VT )

(vGS

VT )

(80)

(81)

(82)

Reemplazando (81) en (82) se tiene que vi = vgs +

vi vo

gm vgs hie + vo ; entonces vgs = 1+g

, por lo tanto, reemm hie

plazando la corriente en (80) y luego vgs , se tiene

vo = RL (1 + hf e ) gm vgs = RL (1 + hf e ) gm

Para nalmente tener

Io = Iref

vo = RL (1 + hf e ) ib

gm vgs = ib

vi = vgs + ib hie + vo

W

L 1

W

L 2

La Fig. ??b, muestra distintas implementaciones de espejos de corriente con transistores nMOS, las cuales permitirn polarizar el amplicador diferencial.

vi vo

1 + gm hie

vo

(RL (1 + hf e ) gm )

=

RL (1+hf e )gm

vi

(1 + gm hie )

1 + 1+gm hie

Para determinar Rin se tiene que ii ! 0, luego Rin = 1.

Para calcular Rout , se anula la excitacin de acuerdo a la

Fig. 35, luego se plantean las ecuaciones.

X. Circuitos BiCMOS

Debido a que el BJT tiene mejor transconductancia que

el MOSFET, para los mismos valores de corriente de polarizacin en cc, tendrn mejor ganancia. Por otro lado,

el MOSFET tienen mejor impedancia de entrada, lo que

lo hace ideal para circuitos con entrada de voltaje. La

combinacin de ambas tecnologas con el n de mejorar

las prestaciones de amplicadores multietapas permite el

nacimiento de los circuitos BiCMOS, los cuales tiene mejoras sustanciales en los circuitos para aplicacin digital y

anloga.

A. BiCMOS Darlington

Este amplicador se muestra en la Fig. 34a, posee una

alta impedancia de entrada y una gran capacidad de corriente. Para la aplicacin tipo seguidor de emisor de la Fig.

34b, se determina la ganancia de voltaje, as

gmv

GS

h

ie

v

GS

_

+

h ib

fe

ip

ib

vp

vi =0

Fig. 35. Clculo de Rout .

ip = ib (1 + hf e )

vp = ib hie vgs

gm vgs = ib

Asi resolviendo se tiene Rout =

vp

ip

hie + g1m

(1+hf e ) :

12

B. BiCMOS Diferencial

V

CC

El circuito de la Fig. 36 es un amplicador diferencial

con nMOS con carga activa. Este ser un circuito con muy

alta impedancia de entrada y muy alta ganancia de voltaje.

I

vo

V

BIAS

Q2

Q1

v

i

VDD

I

Fig. 38. Amplicador Cascode BiCMOS.

Q2

Q1

v

i1

Q3

v

i2

vo

2

conectada con otra etapa en base comn. Note que la base

es un terminal de polarizacin. Circuito de alta impedancia de entrada y alta impedancia de salida.

Anlisis en ca

Q4

-Vss

v

i

Fig. 36. Amplicador Diferencial BiCMOS.

v

i1

vg s1

vg s2

RL

vgs

_

hie

hie

ib3

hoe

i b4

vo =

vo2 = (gm vgs2

hf e ib4 )

1

hoe

(83)

Considerando que Q3 = Q4 ; hie3 = hie4 = hie ,

1

1

1

hoe3 = hoe4 = hoe ; se tiene que ib4 = ib3 , entonces,

2ib4 + hf e ib4 + ib4 hie hoe = gm vgs1 . Despejando la corrig vgs1

ente ib4 = 2+hfme +h

:

ie hoe

Dado que vgs1 = vgs2 , y por la malla de entrada se

tiene que vi1 vi2 = vgs2 vgs1 = 2vgs2

gm vgs2

= vgs2 gm

gm vgs1

1

2 + hf e + hie hoe hoe

2 + 2hf e + hie hoe

1

2 + hf e + hie hoe hoe

hf e

(84)

Si hf e >> 1, se puede aproximar a

vo2 ' vgs2 gm 2

1

=

hoe

gm

vi

hoe

hfe i b

vp

De acuerdo al equivalente de la Fig. 39a, se tiene que

ii = 0, luego Rin = viii ! 1: Por otro lado, usando un

generador de prueba en la salida se tiene que ip = hf e ib ,

pero como vi = 0, esto implica que gm vgs = 0, as ib +

v

hf e ib = 0, luego, ib = 0, por lo tanto, Rout = ipp ! 1.

La ganancia de voltaje se determina de (86).

hfe i b4

ib

hie

(b)

Fig. 37. Diferencial BiCMOS en ca.

vo2 =

gm vg s

i

2

g s2

vo

hfe ib3

hie

Fig. 39. (a) Cascode con carga RL . (b) Determinacin de Rout:

gmv

g s1

ib h

fe i b

gm vg s

v

o

(a)

gmv

hoe

+

v gs

_

Analizando en en ca

ip

ii

hf e ib RL =

hf e

gm vi

RL

(1 + hf e )

(86)

XI. Conclusiones

Los circuitos multietapa son sistemas construidos a partir de varios transistores, estos pueden estar acoplados entre s, ya sea en forma directa o a travs de un capacitor.

Cuando las etapas son acopladas por capacitor se habla de

circuitos de ca, si son acopladas en forma directa se habla

de circuitos en cc y ca. Las conguraciones multietapa

clsicas, el par darlington, el amplicador diferencial y el

cascode, presentan caractersticas propias, alta impedancia

de entrada e incremento de la corriente, alto RRMC y alta

impedancia de salida respectivamente, las cuales pueden

ser mejoradas combinando dichos circuitos con otros elementos, ya sea para su polarizacin (fuentes de corriente

activas) o como carga. La tecnologa BiCMOS aprovecha

lo mejor de ambas familias de transistores, de tal forma de

incrementar las prestaciones, en Rin , Av y Rout .

References

(85)

C. BiCMOS Cascode

El circuito de la Fig. 38 es un amplicador cascode BiCMOS, para este caso se tiene una etapa en fuente comn

[1] Savant, C. Roden, M, Carpenter, G. 1992. Diseo electrnico.

Adisson Wesley Iberoamericana.

[2] Sedra, A. Smith, K. 1998. Microelectronics Circuits. Oxford

Press.

También podría gustarte

- Armónicas en Sistemas Eléctricos IndustrialesDe EverandArmónicas en Sistemas Eléctricos IndustrialesCalificación: 4.5 de 5 estrellas4.5/5 (12)

- Amplificador BJT Darling Ton y Par de RetroalimentacionDocumento4 páginasAmplificador BJT Darling Ton y Par de RetroalimentacionJavier AhumadaAún no hay calificaciones

- Trucos InversoresDocumento3 páginasTrucos InversoresPiter De AzizAún no hay calificaciones

- Pack Examen de ControlDocumento1 páginaPack Examen de ControlElizabeth Milene Ccorimanya AlvarezAún no hay calificaciones

- RF Circuits With Multisim 10 - Exp - 9 - 21.en - EsDocumento56 páginasRF Circuits With Multisim 10 - Exp - 9 - 21.en - EsAga MenonAún no hay calificaciones

- Diagrama Eléctrico de Fuerza para Semaforo de 2 VíasDocumento1 páginaDiagrama Eléctrico de Fuerza para Semaforo de 2 VíasGarcia JairoAún no hay calificaciones

- ApuntesDocumento10 páginasApuntesAbraham Cesar Hernandez ChiñasAún no hay calificaciones

- Transistor BJT EjerciciosDocumento21 páginasTransistor BJT EjerciciosManuel AbrahamAún no hay calificaciones

- 12 Fallas LCD EyserDocumento59 páginas12 Fallas LCD EyserGaby YugeAún no hay calificaciones

- Ejercicios Resueltos Amplificadores MultietapaDocumento14 páginasEjercicios Resueltos Amplificadores MultietapaPaDRAún no hay calificaciones

- BAF 1545 Instr PDFDocumento37 páginasBAF 1545 Instr PDFFernando Leco HuertaAún no hay calificaciones

- Amplificador de Potencia Clase A SintonizadoDocumento6 páginasAmplificador de Potencia Clase A SintonizadoGerardo LopezAún no hay calificaciones

- Cabina ActivaDocumento9 páginasCabina ActivaRobert RmzAún no hay calificaciones

- Laboratorio de FiltrosDocumento17 páginasLaboratorio de FiltrosLuis Mendoza100% (1)

- Amplificador de 100wDocumento20 páginasAmplificador de 100wFidel Condori GuevaraAún no hay calificaciones

- Diseño de Un Sumador RestadorDocumento16 páginasDiseño de Un Sumador RestadorNERY CRISTINAAún no hay calificaciones

- Funcionamiento de La Pantalla LCDDocumento16 páginasFuncionamiento de La Pantalla LCDDaniela ReyezAún no hay calificaciones

- Informe Fuente de CorrienteDocumento8 páginasInforme Fuente de CorrienteHaider Navarro100% (2)

- Guía 6 Amplficadores RFDocumento2 páginasGuía 6 Amplficadores RFMenaly Luzuriaga MoranAún no hay calificaciones

- Informe Matriz de Led SDocumento19 páginasInforme Matriz de Led Smonserin3363Aún no hay calificaciones

- 9619 - Samsung - 540N 540B 740N 740B 740T 940B 940T 940N - Manual - de - EntrenamientoDocumento0 páginas9619 - Samsung - 540N 540B 740N 740B 740T 940B 940T 940N - Manual - de - Entrenamientocalderon64Aún no hay calificaciones

- Tabla Esr 1Documento4 páginasTabla Esr 1silvertronicAún no hay calificaciones

- Amplificador de Potencia Clase (A, B, AB)Documento8 páginasAmplificador de Potencia Clase (A, B, AB)Fabricio Borja Reinoso100% (1)

- Amplificador de AudioDocumento7 páginasAmplificador de AudioKevin PerezAún no hay calificaciones

- Preparatorio07 Lab - Circuitos Electronicos GR7 Arellano KevinDocumento10 páginasPreparatorio07 Lab - Circuitos Electronicos GR7 Arellano KevinKevin ArellanoAún no hay calificaciones

- Informe Del Audio Como AmplificadorDocumento12 páginasInforme Del Audio Como AmplificadorDante Ebrain Condori HuallpaAún no hay calificaciones

- Amplificador Clase BDocumento5 páginasAmplificador Clase Bdixmh2303100% (1)

- Puertas LogicasDocumento6 páginasPuertas LogicasJose luisAún no hay calificaciones

- Sustentacion Compensador Adelanto-Atraso g1Documento17 páginasSustentacion Compensador Adelanto-Atraso g1Carlos LópezAún no hay calificaciones

- Marcador de Baloncesto Con PicDocumento16 páginasMarcador de Baloncesto Con Piccorpses88Aún no hay calificaciones

- Acoplamiento Capacitivo EiiDocumento42 páginasAcoplamiento Capacitivo EiiEve AleAún no hay calificaciones

- 5° PRACTICA LABORATORIO Decodificadores, Multiplexores y SumadoresDocumento14 páginas5° PRACTICA LABORATORIO Decodificadores, Multiplexores y Sumadoresandy77740Aún no hay calificaciones

- Circuito Amplificador de Potencia Con T - 2n3055Documento39 páginasCircuito Amplificador de Potencia Con T - 2n3055JazmínDayannPeraltaBustillos0% (1)

- Configuraciones en Colector Común y en Base Común en AcDocumento5 páginasConfiguraciones en Colector Común y en Base Común en Acjol1386Aún no hay calificaciones

- Amplificador de 12V Con TDA2003Documento6 páginasAmplificador de 12V Con TDA2003Juan Da FonsecaAún no hay calificaciones

- Simulación #5 Motor A PasosDocumento2 páginasSimulación #5 Motor A PasosThelma MoralesAún no hay calificaciones

- Laboratorio3 Respuesta TransitoriaDocumento15 páginasLaboratorio3 Respuesta TransitoriaMiguel CorreaAún no hay calificaciones

- Proteus Practica 2 AscensorDocumento1 páginaProteus Practica 2 AscensorGregorio Caballero RosalesAún no hay calificaciones

- P4G3-Informe FinalDocumento17 páginasP4G3-Informe FinalAnderson EAAún no hay calificaciones

- Medidor de Capacitancia e InductanciaDocumento2 páginasMedidor de Capacitancia e InductanciaJose A. B. MedinaAún no hay calificaciones

- Filtro MultibandaDocumento8 páginasFiltro MultibandaJuan GarciaAún no hay calificaciones

- Mosfet D Amplificador 2N7000Documento8 páginasMosfet D Amplificador 2N7000Julian Andres VictoriaAún no hay calificaciones

- Informe Clase DDocumento35 páginasInforme Clase DJhonattan YanqueAún no hay calificaciones

- Informe Espejos de CorrienteDocumento4 páginasInforme Espejos de CorrienteIvan Andres MuñozAún no hay calificaciones

- Proyecto FinalDocumento14 páginasProyecto FinalYeli FabulosaAún no hay calificaciones

- C3 - El Transistor BJT PDFDocumento169 páginasC3 - El Transistor BJT PDFJhonny PalaguachiAún no hay calificaciones

- Paper Amplificadores OperacionalesDocumento4 páginasPaper Amplificadores OperacionalesMauricio Jumbo CarrionAún no hay calificaciones

- INTRODUCCIÓN Tda 7294Documento20 páginasINTRODUCCIÓN Tda 7294JoseLuisMesaMurciaAún no hay calificaciones

- Problemas de AmplificadoresDocumento11 páginasProblemas de AmplificadoresGary Diaz100% (2)

- Manual de Enconado de BocinasupDocumento5 páginasManual de Enconado de BocinasupJosue Giovani Jasso SanchezAún no hay calificaciones

- Acoplamiento CapacitivoDocumento11 páginasAcoplamiento CapacitivoMiguel Angel100% (1)

- Circuitos MultietapaDocumento12 páginasCircuitos MultietapaOsvaldo Meli0% (1)

- Guia de Laboratorio 1 Amplificadores en CascadaDocumento7 páginasGuia de Laboratorio 1 Amplificadores en CascadaJeffersonLeonRapAún no hay calificaciones

- Informe 2Documento12 páginasInforme 2FRANCISCO JIMENO YUCUMA MORALESAún no hay calificaciones

- Polarizacion BJT Problemas ResueltosDocumento15 páginasPolarizacion BJT Problemas ResueltosFrancisco AlvaradoAún no hay calificaciones

- AMPLIFICADORES, Taller 8Documento11 páginasAMPLIFICADORES, Taller 8Andres Felipe Pulgarin BermudezAún no hay calificaciones

- Capitulo 1 - Generador de FuncionesDocumento18 páginasCapitulo 1 - Generador de Funcionesoscar_ceja_02Aún no hay calificaciones

- Conexiones Con Varios TransistoresDocumento12 páginasConexiones Con Varios TransistoresRoberto Rocca JuárezAún no hay calificaciones

- Informe 1 Circuitos Electronicos IiDocumento27 páginasInforme 1 Circuitos Electronicos IiRamón Gustavo Luque VildozoAún no hay calificaciones

- Diseño de Amplificador MultietapaDocumento7 páginasDiseño de Amplificador MultietapaJose Fernando Fuentes RoaAún no hay calificaciones

- Armar El Siguiente Circuito Que Se Muestra A ContinuaciónDocumento2 páginasArmar El Siguiente Circuito Que Se Muestra A ContinuaciónAnthony JaimeAún no hay calificaciones

- Proyecto EólicoDocumento7 páginasProyecto EólicoALVARO MANUEL GOMEZ GALLEGOSAún no hay calificaciones

- Asociacion de ResistenciasDocumento40 páginasAsociacion de Resistenciaswiledu10Aún no hay calificaciones

- Tabla de Conversión de UnidadesDocumento9 páginasTabla de Conversión de UnidadesSálluryAún no hay calificaciones

- TALLER AutoguardadoDocumento13 páginasTALLER AutoguardadoRolando ChangoAún no hay calificaciones

- Asignaci N 1 Dinamica Aplicada HF PDFDocumento8 páginasAsignaci N 1 Dinamica Aplicada HF PDFchvnAún no hay calificaciones

- Maquinas TermicasDocumento13 páginasMaquinas TermicasSergio MontenegroAún no hay calificaciones

- Tec Bio Futbol1Documento61 páginasTec Bio Futbol1Andres Felipe Parra SandovalAún no hay calificaciones

- Aire Acondicionado: Eficiencia ConsumoDocumento2 páginasAire Acondicionado: Eficiencia ConsumoMiguel RujasAún no hay calificaciones

- Moldeamiento de ArmónicosDocumento146 páginasMoldeamiento de ArmónicosJhonatanBrayamHOAún no hay calificaciones

- Unidad 5 Mecánica ClásicaDocumento29 páginasUnidad 5 Mecánica ClásicaAlexis Santos EscobarAún no hay calificaciones

- FisicaDocumento5 páginasFisicaMarthin Gilari QuispeAún no hay calificaciones

- Informe - 2 TermodinamicaDocumento13 páginasInforme - 2 TermodinamicaGonzalez Cedillo JuanAún no hay calificaciones

- Sol FísicAplicadDocumento106 páginasSol FísicAplicadRodolfo Esteban Andrades EscobarAún no hay calificaciones

- 9 RFT MDTDocumento29 páginas9 RFT MDTMitsúMilagrosToroSayasAún no hay calificaciones

- Ejercicios Termodinamica Unidad 2Documento12 páginasEjercicios Termodinamica Unidad 2Ricardo Emmanuel SierraAún no hay calificaciones

- Inspección Tubular en La Industria PetroleraDocumento130 páginasInspección Tubular en La Industria PetroleraAntonioAvalosAún no hay calificaciones

- 2-Memoria de CálculoDocumento48 páginas2-Memoria de CálculoanalisisnAún no hay calificaciones

- Tarea 5Documento5 páginasTarea 5Germán SuárezAún no hay calificaciones

- Ficha Tecnica R404A PDFDocumento4 páginasFicha Tecnica R404A PDFJosé L RegattoAún no hay calificaciones

- Actividades de HidrostaticaDocumento5 páginasActividades de HidrostaticaAriel Ulises Cortes LeonAún no hay calificaciones

- Control de Pozos PreventivoDocumento352 páginasControl de Pozos PreventivoMario Moises Sagahonj JuarezAún no hay calificaciones

- Ejercicios de Cinética QuímicaDocumento6 páginasEjercicios de Cinética QuímicaROBERTO JOSE AVILA HUACCHAAún no hay calificaciones

- Up Espanol Manual de CarrierDocumento8 páginasUp Espanol Manual de CarrierGabriel Baza Gonzalez0% (1)

- Practica 1-Conocimiento Del Equipo de Laboratorio de Control de Maquinas ElectricasDocumento16 páginasPractica 1-Conocimiento Del Equipo de Laboratorio de Control de Maquinas ElectricasHombre De negociosAún no hay calificaciones

- Maquinas Electricas Cap06Documento22 páginasMaquinas Electricas Cap06William Andrès Coronel CarpioAún no hay calificaciones

- 3 - P53 - Capitulo # 3 - OPAM PDFDocumento121 páginas3 - P53 - Capitulo # 3 - OPAM PDFdanilo ruizAún no hay calificaciones

- Catalogo FlamingoDocumento3 páginasCatalogo Flamingojesus isaias solorioAún no hay calificaciones

- Protocolo Puesta A Tierra PDFDocumento5 páginasProtocolo Puesta A Tierra PDFMiguel Sifuentes PolicarpoAún no hay calificaciones

- Escuela Politécnica Nacional: "Diseño Y Construcción de Un Inversor Bifásico Con Igbt'S"Documento110 páginasEscuela Politécnica Nacional: "Diseño Y Construcción de Un Inversor Bifásico Con Igbt'S"Jose Gregorio LoboAún no hay calificaciones