Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Analisis de Circuitos Convinacionales

Cargado por

Johnnie AustriaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Analisis de Circuitos Convinacionales

Cargado por

Johnnie AustriaCopyright:

Formatos disponibles

TEMA III.

- ANLISIS DE CIRCUITOS COMBINACIONALES

En el presente tema, vamos a presentar los mecanismos y procedimientos para poder

obtener el comportamiento, tanto lgico como temporal (en un grado no excesivamente pre-

ciso), de un circuito combinacional.

1. Introduccin.

Dentro de la Electrnica, existen dos problemas bsicos: anlisis y diseo de circuitos.

Luego antes de abordar dichos problemas, vamos a darles una posible denicin.

El problema de anlisis (que trataremos con respecto a los circuitos combinacionales en

este tema) se puede argumentar de la siguiente forma:

Dado un circuito electrnico, determina el comportamiento

y la funcionalidad que presenta dicho circuito.

En cambio, el problema del diseo (que veremos en el tema IV y siguientes con respecto a los

circuitos combinacionales) es el siguiente:

Dados un comportamiento y una funcionalidad, determina el

circuito electrnico que los presenta.

Es decir, un problema es el inverso del otro.

Estos dos problemas se pueden afrontar desde tres formas diferentes:

Mediante tcnicas algebraicas, generalmente clculos a mano. Este hecho conlleva

una limitacin a bloques o circuitos pequeos.

Mediante simulacin hardware o emulacin. Este mtodo se basa en la construccin

de un modelo fsico, siendo este ltimo el que es estudiado. Por ejemplo, montando

un circuito en una placa de entrenamiento.

Mediante simulacin. Nos ayudamos de las herramientas de diseo asistido por orde-

nador (C.A.D.), en la que emulamos el circuito. Estas herramientas se pueden clasi-

car en herramientas de simulacin (para obtener el comportamiento de un circuito) y

de sntexis (para obtener un circuito a partir de un comportamiento).

De las tres formas, la ms empleada es la simulacin por ser la que mayor potencia de clculo

presenta y por lo tanto la que mayores sistemas puede abarcar.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 32

2. Puertas Lgicas.

Una de las principales ventajas de utilizar el lgebra de conmutacin radica en que las

operaciones bsicas de este lgebra (operacin AND, OR y NOT) tienen un equivalente directo

en trminos de circuitos. Estos circuitos equivalentes a estas operaciones reciben el nombre de

puertas lgicas. No obstante, el resto de circuitos lgicos bsicos tambin reciben el nombre

de puertas, aunque su equivalencia se produce hacia una composicin de las operaciones lgi-

cas bsicas.

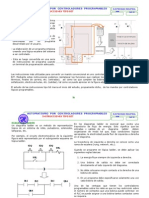

Las tres puertas fundamentales reciben el mismo nombre que los operadores, es decir,

existen las puertas AND, puertas OR y puertas NOT. La ltima puerta recibe el nombre ms

usual de inversor. En la gura 3.1 mostramos los smbolos de estas puertas tanto tradicionales

como internacionales, aunque usaremos preferentemente los smbolos tradicionales.

En primer lugar debemos identicar aquellos conjuntos de puertas con los que se puede

implementar cualquier funcin lgica. As

Un conjunto de puertas completo es aquel conjunto con el

que se puede implementar cualquier funcin lgica

El conjunto completo ms intuitivo es aquel formado por todas las operaciones bsicas del

lgebra de conmutacin, es decir, el conjunto formado por puertas AND, OR e inversores.

El siguiente paso consiste en identicar cuando un conjunto de puertas es completo. Si

nos guiamos por la denicin, podramos pensar que si empezamos a implementar funciones

arbitrarias, podramos determinar si el conjunto de puertas es completo. No obstante, este

mtodo no sera muy prctico ya que siempre existira la duda de si alguna funcin que no

A

B

Q

F

A

B

Q

F

A

F

Puerta AND Puerta OR

Puerta NOT o inversor

F = AB...Q

F = A+B+...+Q F = A = A

A

B

Q

F

&

A

B

Q

F 1

A

F 1

Smbolos

tradicionales

Smbolos

internacionales

Figura 3.1.- Simbologa tradicional e internacional correspondiente a las puertas lgicas

bsicas.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

33

hubisemos implementado, no podra implementarse con dicho conjunto. Por lo tanto, tenemos

que buscar otro mtodo que no deje lugar a dudas.

Este mtodo podra consistir en obtener las puertas de un conjunto completo ya cono-

cido, por ejemplo, las tres puertas bsicas. Si esta transformacin es factible, podemos garanti-

zar que el nuevo conjunto es completo. De hecho, para implementar una funcin en el nuevo

conjunto, podramos ir transformando puerta a puerta (aunque esta solucin no sera ptima).

Por ejemplo, probaremos con el conjunto formado con las puertas AND y los inversores (gura

3.2):

Luego, el conjunto formado por las puertas AND e inversores forman un conjunto completo.

De idntica forma se puede probar que el conjunto formado por las puertas OR y los inversores

forman un conjunto completo.

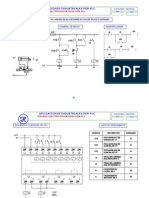

Debido a esta propiedad (que las puertas AND e inversores, al igual que las puertas OR e

inversores, forman un conjunto completo), cobra especial importancia la unin de una puerta

AND (u OR) con un inversor, dando lugar a puertas especcas llamadas puertas NAND

(AND-NOT) y NOR (OR-NOT), cuyos smbolos se muestran en la gura 3.3.

Se puede probar que tanto las puertas NAND como las puertas NOR forman un conjunto com-

pleto, como vemos en la gura 3.4:

A

B

F = AB

A F = A

A

B

F = (AB) = A + B

Puerta AND

Inversor

Puerta OR

Figura 3.2.- Conjunto completo formado por puertas AND e inversores.

A

B

Q

F

A

B

Q

F

Puerta NAND Puerta NOR

F = AB...Q

F = A+B+...+Q

A

B

Q

F &

A

B

Q

F 1

Smbolos

tradicionales

Smbolos

internacionales

Figura 3.3.- Simbologa tradicional e internacional de las puertas NAND y NOR.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 34

Dentro de las denominadas puertas, que no implementan un operador directo, se encuen-

tra la conocida como OR-exclusiva o XOR. Esta puerta muestra la siguiente funcionalidad: Y

= A'B + AB'. La importancia radica en su amplio uso en la aritmtica binaria (siendo la puerta

base de la suma). Tambin es muy usada en las circuiteras de deteccin y correccin de erro-

res, implementando funciones de comparacin y paridad. Su smbolo y tabla de combinaciones

se muestra en la gura 3.5.

Adems de tener las propiedades conmutativas y asociativas, algunas igualdades tiles son las

siguientes:

(x y)' = x' y = x y'

(x y) = (xy+xy) = (xy)(xy) = (x+y)(x+y) = xy + xy

x y = xy + xy

x y = xy + xy

x x = 0

x x = xx + xx = 0 + 0 = 0

x x' = 1

x x = xx + xx = x + x = 1

A F

A F

A

B

F

A

B

F

F

A

B

F

A

B

Figura 3.4.- Conjuntos completos formados por puertas (a) NAND y (b) NOR.

(a)

(b)

A

B

F = A B

A B F

0 0 0

0 1 1

1 0 1

1 1 0

Figura 3.5.- Smbolo y tabla de verdad de la funcin XOR (exclusiva OR).

=1

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

35

x 1 = x'

x 1 = x0 + x1 = 0 +x = x

x 0 = x

x 0 = x1 + x0 = x + 0 = x

x(y z) = (xy) (xz)

x(y z) = x(yz + yz) = xyz + xyz

(xy) (xz) = (xy)(x+z) + (x+y)(xz) = xyz + xyz

x (xy') = x +y

x (xy) = x(x+y) + x(xy) = xy

x (x+y) = x'y

x (x+y) = x(xy) + x(x+y) = xy

Como podemos ver, la negacin se obtiene con una puerta XOR y el valor lgico 1; no obs-

tante, no podemos conseguir ninguna puerta AND u OR a partir exclusivamente de una puerta

XOR, ya que para obtener una de las operaciones bsicas debemos ayudarnos de la otra.

Luego, la puerta XOR no forma un conjunto completo, pero si le aadimos una puerta AND o

una puerta OR, s se convierten en un conjunto completo.

Una nota importante en todos los smbolos es que la presencia de un crculo indica una

inversin, como podemos ver en la gura 3.6:

3. Anlisis.

El comportamiento de los circuitos combinacionales slo depende de las seales de

entrada en un instante determinado, y no de la secuencia de entradas, es decir, de la historia del

circuito. Este hecho no quiere decir que el comportamiento temporal no sea importante, de

hecho una de las principales caractersticas de los circuitos que se tienen en cuenta es la veloci-

dad de operacin o el retraso de propagacin. En funcin de este retraso, podemos encontrar

dos zonas temporales de operacin bien diferenciadas: estado estacionario y estado transitorio.

Una posible denicin de estos estados sera la siguiente:

El estado transitorio es aquel espacio temporal que va

desde el cambio de las entradas hasta que la salida se

estabilice.

En este estado, tanto las seales internas como las de salida pueden sufrir cambios (no necesa-

riamente uno solo, sino que pueden ser varios), aunque las seales de entrada no cambien.

Estos posibles cambios son los necesarios para que el circuito busque su estabilizacin.

F = (A B)

A

B

Figura 3.6.- Utilizacin de los crculos como smbolo de negacin.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 36

El estado estacionario es aquel espacio temporal que va

desde la estabilizacin del circuito lgico hasta que las

entradas vuelvan a cambiar.

En este estado, ninguna de las seales del circuito puede sufrir ningn cambio, a no ser que

sean las seales de entrada. Esta diferencia se puede apreciar en la gura 3.7. Es decir, en el

estado transitorio se producen todos los cambios necesarios en las seales de salida (e internas)

hasta conseguir la estabilizacin del circuito. En cambio, en el estado estacionario, las seales

de salida (e internas) estn estables a su valor correcto. Por lo tanto, el comportamiento lgico

hay que observarlo en el estado estacionario, en el cual no se producir ningn cambio adicio-

nal debido al cambio actual de las seales de entrada.

3.1. Anlisis estacionario.

Una vez planteado en la zona temporal donde nos encontramos, el estado estacionario,

vamos a afrontar el anlisis estacionario de un circuito combinacional. En este estado, las sea-

les del circuito no cambian, luego lo signicativo de este estado es su valor. Una forma simple

de analizar un circuito en su estado estacionario consiste en etiquetar todos los nodos del cir-

cuito con la funcin lgica que realizan. Por lo tanto, la frmula de conmutacin coincidir con

la etiqueta del nodo de salida, sustituyendo las seales internas por sus funciones de las varia-

bles de entrada.

En la gura 3.8 mostramos un ejemplo de anlisis estacionario. Por lo tanto, una vez que

tenemos etiquetado la(s) seal(es) de salida, tenemos que recorrer el circuito en orden inverso

para determnar las frmulas de cada una de las seales internas.

Una vez que tenemos la frmula con la que hemos implementado la funcin, se puede

representar mediante su tabla de combinaciones, mostrada en la tabla 3.1. Como ya comenta-

mos, la tabla de verdad debe tener como mnimo todas las seales de entrada y salida. No obs-

tante, puede ser interesante incluir las seales internas para una obtencin ms segura. Este

Seales

de entrada

Seales

de salida y/o internas

Estado

transitorio

Estado

estacionario

Figura 3.7.- Separacin entre estados transitorios y estacionarios.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

37

hecho suele cobrar ms sentido cuando el circuito que tenemos que analizar sea ms complejo,

tanto en dimensiones como en complejidad de los componentes.

Algunas recomendaciones simples para una mayor facilidad de obtener los valores de

una frmula lgica pueden ser las siguientes:

Si la frmula es una suma de trminos, el valor ser igual a 1 siempre y cuando algu-

nos de los trminos sea 1. Luego, nos centramos trmino a trmino para ver si su

valor es 1. En todos los casos en que ningn trmino sea 1, el valor es 0.

Si la frmula es una producto de trminos, el valor ser igual a 0 siempre y cuando

algunos de los trminos sea 0. Luego, nos centramos trmino a trmino para ver si

su valor es 0. En todos los casos en que ningn trmino sea 0, el valor es 1.

Si la frmula es una mezcla de sumas y productos, se aplican las recomendaciones

anteriores segn corresponda

3.2. Anlisis transitorio.

El estado transitorio, como ya hemos visto, tiene unos lmites temporales y la posibilidad

de cambiar un nmero aleatorio de veces las seales del circuito. Por lo tanto, lo importante de

este estado ser conocer ese lmite temporal, y las transiciones no necesarias que se produci-

rn.

A B C N1 N2 N3 N4 F

0 0 0 0 1 1 1 1

0 0 1 0 0 1 0 0

0 1 0 0 1 0 0 0

0 1 1 0 0 0 0 0

1 0 0 0 1 0 0 0

1 0 1 0 0 0 0 0

1 1 0 1 1 0 0 1

1 1 1 1 0 0 0 1

Tabla 3.1. Tabla de verdad del ejemplo de la gura 3.8.

A

B

C

A

B

N1 = AB

N2 = C

N3 = A+B

N4 = N2N3

F = N1 + N4

Figura 3.8.- Ejemplo de anlisis estacionario de un circuito lgico.

F = AB + cN3

F = AB + c(A+B)

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 38

3.2.1. Caminos crticos

El primer dilema con el que nos encontramos es discenir cuando acaba el estado transito-

rio y empieza el estado estacionario. Esta frontera se podra encontrar obteniendo el retraso de

propagacin del circuito (duracin del estado transitorio). Este retraso ser igual a la suma de

los retrasos de las puertas por las que se transmiten los datos. En el ejemplo anterior podemos

distinguir tres caminos diferentes por simple inspeccin:

AND - OR --> T = T

AND

+ T

OR

INV - AND - OR --> T = T

INV

+ T

AND

+ T

OR

NOR - AND - OR --> T = T

NOR

+ T

AND

+ T

OR

Ahora nos encontramos ante el problema de qu camino deberamos escoger. No obs-

tante, no podemos perder de vista que lo realmente imortante es el tiempo que transcurre desde

que entra la seal hasta que llega a la salida. Luego, puede que existan caminos equivalentes

(en el sentido de que tengan el mismo retraso). De estos caminos debemos elegir los ms len-

tos, con el n de garantizar que cualquier combinacin de entrada habr llegado a la salida

transcurrido dicho tiempo.

Cada combinacin de entradas llegar al nodo de salida por uno o varios de esos caminos

(siempre el ms rpido cortando el ms lento). Igual que una combinacin puede llegar a la

salida por varios caminos, se puede dar el caso de que un camino se encuentre permanente-

mente cortado, es decir, siempre exista otro con menor retraso. Por lo tanto, tenemos que

garantizar que el camino, que hayamos elegido como crtico, se siga por alguna combinacin.

Las situaciones ms usuales en las que un camino se corta son las siguietnes:

F 0, ya que la salida no depende del camino elegido, sino que siempre valdr 0

F + 1, por la misma razn anterior.

Veamos qu combinaciones sigue cada camino del circuito de la gura 3.8:

En el caso del primer camino, la operacin c(A+B)no debe inuir en la operacin

OR. Por lo tanto, sta debe valer 0 para que x + 0= x. Luego las combinaciones

que siguen este camino son:

ABC = 001 - 011 - 101 - 111 - 010 - 100 - 110

En el caso del segundo camino, la operacin c(A+B) s debe inuir en la operacin

OR, por lo que en este caso AB debe valer 0 para que 0 + x = x. Adems, la ope-

racin NOR no debe inuir en la operacin AND, por lo que A+B debe valer 1 para

que 1 x = x. Luego las combinaciones que siguen este camino son:

ABC = 000 - 001

La descripcin del tercer camino ser semejante a la del segundo intercambiando los

papeles del inversor y la puerta NOR. Luego las combinaciones sern:

ABC = 000 - 010 - 100

Como podemos ver, tenemos combinaciones que verican ms de un camino como puede ser

la combinacin 000 (entre otras). Cuando estamos en estas situaciones, el retraso de dicha

combinacin ser el menor retraso (ya que en ese momento, la seal ha llegado a la salida).

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

39

Por lo general, los estados transitorios y estacionarios no estn referenciados a cada com-

binacin de las seales de entrada, sino al circuito en s mismo. Luego, la duracin del estado

transitorio se toma como la ms larga, asegurando as que en el estado estacionario las seales

de salida estarn estabilizadas.

El camino crtico se define como aquel camino que produce

el mayor retraso para alcanzar la estabilizacin de las

seales del circuito.

Luego lo realmente interesante es obtener el camino crtico. Para ello deberamos conocer el

retraso de cada puerta. En el caso de no conocerse se toma por convencin el mismo retraso

para todas las puertas, luego, ser aquel por el que pase ms puertas. En nuestro ejemplo ten-

dramos como caminos crticos los dos ltimos (con un retraso de tres puertas). Pero antes de

asignar este camino, debemos garantizar que este camino es seguido por alguna combinacin.

3.2.2. Azares

El segundo aspecto del anlisis transitorio consiste en deducir las transiciones que ten-

drn lugar en dicho estado. Sera lgico pensar que para cada cambio de las seales de entrada,

debera existir como mximo un cambio en cada seal de salida (si tuviese que cambiar su

valor lgico) o ninguno (si no tuviese que cambiar dicho valor). No obstante esto no se produce

en la mayora de los casos reales.

El principal error consiste en suponer que se pueden producir cambios simultneos de las

diferentes seales del circuito. Como podemos apreciar en la gura 3.9, las seales no llegan

de forma simultnea a todas las partes del circuito debido a los diferentes retrasos de cada

puerta utilizada. Podemos apreciar que las seales de entrada al circuito han cambiado simult-

neamente, pero a la puerta C no llegan los cambios de forma simultnea, sino que el cambio de

X

1

llega antes. Luego la puerta C realizar dos operaciones en lugar de una, como era de espe-

rar.

Estos retrasos no son controlados ya que adems de la funcin lgica, dependen de otros

muchos factores, tanto internos (dispositivos parsitos) como externos (temperatura). Adems,

la insercin de las seales de entrada (ya sea por un operador hmano, mecnico o electrnico)

no garantiza que se puedan producir cambios simultneos de seales, sino todo lo contrario

(debido a la no idealidad de los operadores).

T

A

T

B

T

C

X

1

X

2

X

21

X

11

X

1

X

11

X

2

X

21

T

B

T

A

Figura 3.9.- Imposibilidad de tener transiciones simultneas en ms de una seal digital.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 40

Por lo tanto, estas transiciones no consideradas son de gran importancia, ya que nos pue-

den conducir a situaciones errneas, y no necesariamente de forma transitoria. Si dicho cir-

cuito se comporta como entrada de otro, puede que una situacin anmala produzca que la

situacin inicial no sea la correcta, obteniendo un comportamiento diferente al deseado. Ade-

ms, cuanto ms transiciones sean necesarias para la estabilizacin del circuito, quiere decir

que el circuito consumir ms potencia (la energa necesaria para llevar a cabo su operacin

por unidad de tiempo); este parmetro cobra cada vez ms importancia con el auge de los siste-

mas sin cable. Por lo tanto,

se denomina azar a cualquier desviacin del comporta-

miento esperado, potencial o real, de un circuito de con-

mutacin cuando sufre un cambio en sus entradas.

Las desviaciones potenciales, no reales, se siguen considerando azares debido a que el com-

portamiento de un circuito (y en mayor grado, su rgimen transitorio) puede depender de las

condiciones de operacin en la que se encuentre el circuito, como son la temperatura de opera-

cin, la vida de los dispositivos, etc. A una determinada temperatura, no se observa la presen-

cia del azar, pero si se altera dicha temperatura, los retrasos de las puertas pueden variar,

ocasionando la presencia del azar.

Supongamos que queremos pasar de la combinacin 000 a la 110 en la funcin con

las tablas de combinaciones de la gura 3.10. Como hemos visto antes, no podemos cambiar

ms de una seal de forma simultnea; luego primero debemos cambiar una seal de entrada y

luego la otra. Si tenemos en cuenta este razonamiento, la salida pasar por un valor 0 sin que

nosotros esperemos este nivel. Por lo tanto, este pulso, mostrado en la gura 3.10, ser consi-

derado un azar, por la razn de que no es esperado.

0 1 0 0

A C F

0 0 1 0

1 0 1 0

1 0 0 0

0 1 0 1

0 0 1 1

1 1 1 1

1 1 0 1

B

0 1 0 0

A C F

0 0 1 0

1 0 1 0

1 0 0 0

0 1 0 1

0 0 1 1

1 1 1 1

1 1 0 1

B

A

B

C

F

Figura 3.10.- Ejemplo de azar de funcin.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

41

Una vez que hemos detectado la presencia de azares, la cual va a reducir las prestaciones

del diseo, tenemos que obtener las causas de estos azares. Como ya hemos dicho la causa

principal de los azares es la imposibilidad de tener cambios simultneos de ms de una seal.

As, una primera causa son los cambios simultneos de las seales de entrada, que debido a la

funcin lgica implementada provocar un azar.

Los azares provocados por la funcin lgica en s misma se

denominan azares de funcin.

Un ejemplo de azar de funcin es el mostrado en el ejemplo anterior. En ese ejemplo, el azar

era debido a que para llegar a la combinacin nal se deba pasar por otras combinaciones en

las que la salida tomaba un valor diferente.

Una forma sencilla de evitar los azares de funcin ser imponer la restriccin de no per-

mitir cambios simultneos de seales de entrada. Con esta medida, la transicin desde 000 a

110 no sera permitida y tendramos que elegir alguno de los dos caminos anteriores. El

comportamiento sera el mismo pero con la salvedad de que, en caso de elegir el primer

camino (donde se obtiene la presencia del azar), el pulso de bajada es esperado y ya no sera

considerado azar.

Hasta ahora slo hemos tratado las seales de entrada, no obstante, en un circuito existen

tres tipos de seales: entrada, salida e internas. La imposibilidad de cambiar simultneamente

ms de una seal interna producir un comportamiento similar, aunque solamente se haya cam-

biado una seal de entrada. La funcin anterior puede tener la implementacin mostrada en la

gura 3.11.

Vamos a estudiar la transicin 011 a 001. En esta transicin slo cambia la seal B,

por lo que no existirn azares de funcin. No obstante, podemos apreciar que se tiene que pro-

ducir una transicin simultnea de las seales N2 y N3. Como esto no es posible, se producir

un azar en la seal N4 que se transmitir a la salida.

Si estudiamos la transicin 111 a 101, podemos apreciar que no existirn azares de

funcin, ya que al igual que antes slo se produce el cambio de una sola seal de entrada. No

obstante se deberan producir una transicin simultnea en las seales N2, N3 y N5. Como esto

no es posible, se producir un azar en la seal N4 (debido a la transicin de N2 y N3) que se

unir a otro en la salida (debido al azar de N4 y a N5).

Estos ltimos azares no son debidos a la funcin lgica, sino al circuito lgico que

implementa la funcin lgica.

Los azares provocados por la implementacin lgica del

circuito se denominan azares lgicos.

En este caso se aprecia ms claro que la no simultaneidad de las transiciones se debe a los

retrasos de las puertas utilizadas y a su interconexin.

En el ejemplo anterior, hemos observado dos comportamientos diferentes. La diferencia

radica en que la seal de salida, al alcanzar el estado estacionario, deba cambiar de valor o no.

Esta diferencia nos da otra clasicacin de azares:

Azares estticos.- donde la seal de salida en la que se produce el azar no debera

cambiar su estado. Este tipo de azares se debe a que dos seales que deberan ser com-

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 42

plementarias entre s, no lo son en un determinado intervalo temporal dentro del

estado transitorio. En nuestro caso seran N2, que debera valer B, y N3, que debera

valer B; pero debido a los retrasos de las puertas se observa que en el transitorio B =

B, que ser imposible en el estado estacionario.

Azares dinmicos.- donde la seal de salida en la que se produce el azar s debe cam-

biar de estado. Este tipo de azares se puede ver como un azar esttico al que se le ha

aadido la transicin de una seal. En nuestro caso sera el azar esttico producido por

las seales N2 y N3, al que se le ha aadido la transicin de la seal B a travs de N5.

Esta clasicacin es vlida tanto para azares de funcin como para azares lgicos. Como

hemos visto que la forma de eliminar los azares de funcin consiste en prohibir cambios en

varias seales de forma simultnea, de ahora en adelante nos referiremos a azares lgicos per-

mitiendo nicamente cambios en un sola seal de entrada.

A

B

B

B

C

A

B

C

N4

N1

N2

N3

F

N5

N5

N3

N1

N2

N4

F

T

inv

T

AND

T

AND

T

OR

T

OR

T

OR

T

OR

T

OR

T

OR

T

OR

T

inv

T

AND

T

AND

T

AND

A = 0

B = 1

C = 1

N1 = 0

N2 = 1

N3 = 0

N4 = 0

N5 = 0

F = 0

A = 0

B = 0

C = 1

N1 = 0

N2 = 0

N3 = 1

N4 = 0

N5 = 0

F = 0

A = 1

B = 1

C = 1

N1 = 0

N2 = 1

N3 = 0

N4 = 0

N5 = 1

F = 0

A = 1

B = 0

C = 1

N1 = 0

N2 = 0

N3 = 1

N4 = 0

N5 = 0

F = 1

Figura 3.11.- Ejemplo de azares lgicos.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

43

Antes de seguir con los azares lgicos, vamos a ver una nueva forma tabular de represen-

tar funciones de conmutacin, denominada mapa de Karnaugh. Este mapa es una tabla donde

las columnas y las son las posibles combinaciones que pueden tomar las diferentes seales de

entrada, encontrndose en el interior de cada celda el valor de la funcin para la combinacin

en cuestin. La peculiaridad de esta tabla es que las combinaciones de seales de entrada de

cada celda adyacente deben tener una distancia de uno (solamente una seal puede tener un

valor diferente). Con esta situacin se consigue que el camino seguido por un cambio de sea-

les de entrada debe seguir a travs de celdas adyacentes, comprobando fcilmente la presencia

de azares de funcin y lgicos (como ya veremos).

En la gura 3.12 se mostrarn los mapas de Karnaugh correspondientes a funciones

hipotticas de 2, 3 y 4 variables:

Un ejemplo de la utilidad de los mapas de karnaugh consiste en la identicacin de los

azares de funcin, como podemos ver en la gura 3.13. Los caminos que han sido expuestos no

son los nicos que se pueden dar. En el caso del azar esttico podemos comprobar que existen

dos caminos diferentes para llevar a cabo la transicin. En cambio, en el caso del azar din-

mico, podemos comprobar que existen seis caminos diferentes para obtener dicha transicin.

No obstante, con la simple condicin de que se obtenga un azar para alguna de las combinacio-

nes, ya se dir que existe el azar debido a la caracterstica de potencial.

0 1 00 01 11 10

00 01 11 10

0

1

0

1

00

01

11

10

Figura 3.12.- Ejemplos de mapas de Karnaugh.

00 01 11 10

0

1

1 1 0 1

0 0 1 0

000

0

010

1

011

0

000

0

001

1

011

0

111

1

00 01 11 10

0

1

1 1 0 1

0 0 1 0

Azar esttico

Azar dinmico

Figura 3.13.- Ejemplos de azares estticos y dinmicos de funcin.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 44

Una vez que hemos denido lo que se entiende por azar y cul es su comportamiento, el

siguiente paso ser determinar si en un circuito en particular se da su presencia. Una forma de

llevar a cabo esta tarea podra ser estudiar cada transicin de combincaciones de entrada de la

misma forma que en la gura 3.11. No obstante, este mtodo sera inviable debido al creci-

miento exponencial de transiciones con el nmero de seales de entrada. Otra forma ms via-

ble ser la siguiente.

El principal motivo de la existencia de azares lgicos estticos consiste en la aparicin de

variables complementadas y sin complementar (que deberan tener siempre valores opuestos)

con el mismo valor de forma transitoria debido generalmente al retraso de las puertas lgicas.

Por lo tanto, a la hora de analizar algn circuito en rgimen transitorio (y observar la posible

presencia de azares) no podemos hacer uso del 4 postulado del lgebra de Boole ni de los teo-

remas basados en l. Por lo tanto, un mtodo para detectar la presencia de azares estticos, se

basa en el siguiente procedimiento:

A partir de la frmula original, si existe alguna combi-

nacin de las seales de entrada que la transforme en

alguna de las formas del 4 postulado, se puede demostrar

que para dicha transicin existe un azar esttico.

Si reducimos la frmula a una de las expresiones del cuarto postulado, en la transicin de la

variable que nos queda cambiarn de valor los dos trminos, y a valores diferentes. sta, como

recordamos, es la condicin de azar: un cambio simultneo de varias seales (dos seales inter-

nas en este caso).

No obstante, haciendo uso de los mapa de karnaugh, existe un mtodo simple para deter-

minar la presencia de azares estticos, el cual sigue el procedimiento expuesto a continuacin:

En el caso de los azares de 1, se obtiene la suma de pro-

ductos de la funcin (sin aplicar el cuarto postulado, ni

los teoremas asociados) y se rodean los 1's que son gene-

rados por cada trmino producto. Si existen 1's adyacen-

tes que no son generados por el mismo trmino producto, se

demuestra que en dichas transiciones existen azares.

En el caso de los azares de 0, se opera de la misma forma

pero cambiando trminos producto por trminos suma, suma

de productos por producto de sumas y 1's por 0's. Tambin

se puede operar de la misma forma que antes, pero teniendo

en cuenta ahora la funcin complementada (ya que un azar

de 0 se convierte en un azar de 1 en la frmula complemen-

tada).

En este caso, existen dos trminos suma o producto que deben cambiar de valor de forma

simultnea. Es decir, tendremos una condicin de azar en dicha transicin.

En el caso de azares lgicos dinmicos, no debemos perder de vista que se trata de un

azar esttico al que se le ha aadido una transicin. La forma de aadir esa transicin puede set

a travs de un producto o una suma lgica. Por lo tanto, las ecuaciones a las que se llegara

sern las siguientes:

F = x + xx

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

45

F = x(x+x)

Las otras dos condiciones [ xxx y x+x+x ] no seran azares ya que se trataran de la misma

transicin en instantes diferentes, es decir, la ms lenta no se producira. En este caso se aade

que dos seales que deberan tener el mismo valor presentan valores diferentes. Luego, en la

manipulacin de la frmula lgica no seran aplicables los teoremas de idempotencia, absro-

cin, ni los derivados de ellos.

4. Ejemplo de aplicacin.

A continuacin veremos como ejemplo el anlisis, tanto estacionario como transitorio

(con respecto a azares lgicos estticos y al camino crtico), del circuito mostrado en la gura

3.14:

4.1. Anlisis estacionario

La meta del anlisis estacionario es obtener la funcin del circuito que se desea analizar.

Este objetivo e consiguir obteniendo la frmula lgica y/o la tabla de verdad del circuito.

La frmula obtenida del circuito es:

N1 = c

N2 = b+N1 = b + c

N3 = b

N4 = N3 N2

N5 = ab

F(a,b,c) = N5 + N4 = ab + b(b+c)

A continuacin, para acabar el anlisis estacionario, mostramos la tabla de verdad en la tabla

3.2. Una forma rpida de obtener la tabla consiste en pasar la frmula a suma de productos

(producto de sumas); una vez expresada de esta forma, determinar las combinaciones para las

que cada trmino producto (suma) toma el valor 1 (0); el resto de combinaciones tomar el

valor 0 (1).

A

B

B

B

C

N5

N3

N1

N2

N4

F

Figura 3.14.- Ejemplo de anlisis estacionario y transitorio.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 46

4.2. Anlisis transitorio

Una vez que hemos obtenido la funcin implementada por el circuito, pasaremos a reali-

zar el anlisis transitorio. Este anlisis llevar la determinacin del camino crtico as como de

los azares lgicos. En este tipo de problemas no hay que estudiar los azares de funcin, ya que

stos son inherentes a la funcin lgica, y no al circuito que es lo que se est estuadiando.

4.2.1. Camino crtico

Para empezar el anlisis transitorio, vamos a hallar y cuanticar el camino crtico. Como

no nos dan los retrasos de las puertas, supondremos que todas tienen el mismo retraso, por lo

que el camino crtico ser aquel que atraviese ms puertas. Este camino ser el siguiente: INV-

OR-AND-OR. Una vez hallado el camino con mayor retraso, debemos garantizar que alguna

combinacin de entrada siga dicho camino:

Para que la ltima puerta OR espere a la puerta AND, se debe cumplir que N5 = ab =

0, luego a y/o b debe valer 0.

Para que la puerta AND espere a la puerta OR, se tiene que cumplir que N3 = b = 1,

luego b debe valer 0.

Para que la puerta OR espere al inversor, se debe cumplir que b = 0, luego b debe valer

0.

Por lo tanto, las combinaciones que siguen el camino crtico sern aquellas que cumplan las

condiciones anteriores. stas se muestran en la tabla 3.3:

A B C F Trminos con valor 1

0 0 0 1 bc

0 0 1 0 --

0 1 0 0 --

0 1 1 0 --

1 0 0 1 bc

1 0 1 0 --

1 1 0 1 ab

1 1 1 1 ab

Tabla 3.2. Tabla de verdad del circuito de la gura 3.14.

A B C

0 0 0

0 0 1

1 0 0

1 0 1

Tabla 3.3. Combinaciones de seales de entrada que siguen el camino crtico.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

47

4.2.2. Azares lgicos estticos

El siguiente paso del anlisis ser determinar la presencia de azares (por ahora estticos).

Para utilizar el mtodo del mapa, partiremos de la funcin estacionaria, la cual pasaremos a

suma de productos (sin utilizar el 4 postulado ni sus teoremas asociados) para determinar la

presencia de azares estticos de 1.

F = ab + b(b+c) = ab + bb + bc

El mapa de karnaugh se muestra en la gura 3.15. El trmino bb no tiene ningn 1 ya que su

valor estacionario es 0. En el mapa podemos apreciar que existen dos 1s adyacentes que no

son agrupados por el mismo trmino, luego existir un azar para dicha combinacin. Esta com-

binacin es A=1, B= b, C = 0, por lo que el azar se produce para la transicin en la seal B.

Para estudiar la presencia de azares de 0, pasaremos la funcin a producto de sumas,

para lo cual complementaremos dos veces la expresin en suma de productos (de nuevo sin uti-

lizar el 4 postulado ni sus teoremas asociados).

F = (a+b)(b+b)(b+c) = (ab + b)(b+c) = ab + bb + bc

F = (a+b)(b+b)(b+c)

En este caso, el mapa de karnaugh ser el mostrado en la gura 3.16. De nuevo, podemos apre-

ciar que existen dos 0s adyacentes sin que sean englobados por el mismo trmino suma. Por lo

tanto, existir un azar para la combinacin A=0, B=b, C=1.

00 01 11 10

0

1

0 1 0 0

1 1 0 1

AB

C

F

AB

BC

Figura 3.15.- Obtencin de azares lgicos estticos de 1, utilizando el mapa de karnaugh.

00 01 11 10

0

1

0 1 0 0

1 1 0 1

AB

C

F

A+B

B+C

Figura 3.16.- Obtencin de azares lgicos estticos de 0, utilizando el mapa de Karnaugh.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 48

Un mtodo para eliminar los azares estticos consiste en evitar situaciones como las des-

critas anteriormente, es decir, que no existan 1's (0's) adyacentes sin que sean cubiertos por

alguna puerta. Por lo tanto, aadiremos trminos producto (para los azares de 1) y trminos

suma (para los azares de 0) que engloben los 1s y 0s adyacentes que no sean englobados

para un mismo trmino producto y suma. Debemos notar que una expresin en trminos suma

(producto) no contar con la presencia de azares de 1 (0).

Si se lleva a cabo este mismo estudio por mtodos algebraicos, llegaremos a la misma

conclusin. La frmula de partida es: F = ab + b(b+c). La condicin de que pueda existir

azar esttico es que una misma seal aparezca, negada y sin negar; luego en el caso que nos

ocupa slo puede existir para una transicin en la seal b.

F = b + b,

se tiene que cumplir que ab = b, luego a=1

se tiene que cumplir que b(b+c) = b, luego b+c=1 (sin dar ningn valor a la

variable b en la que se producir la transicin), por lo que c=0

F = bb

se tiene que cumplir b(b+c) = bb, luego c=1

para evitar la inuencia del trmino ab se tiene que cumplir que ab=0, luego a=0

Por lo tanto, podemos apreciar que existe un azar de 1 para una transicin en la seal b

cuando a=1 y c=0; y existe un azar de 0 para una transicin en la seal b cuando a=0 y c=1.

Estos resultados corroboran el anlisis llevado a cabo mediante los mapas de Karnaugh.

4.2.3. Azares lgicos dinmicos

Un azar lgico dinmico es un cambio transitorio de un valor de salida que slo debera

tener una transicin, pero presenta ms de una de ellas (generalmente tres) ante una transicin

en una variable de entrada.

El principal motivo de la existencia de azares lgicos dinmicos consiste en la aparicin

de variables complementadas y sin complementar (como en los azares estticos) que siguen

ms de un camino, tal que la funcin pueda escribirse de la siguiente forma:

F = a

1

+ a

2

a'

3

--> F= a

1

(a

2

+ a'

3

)

Donde 1, 2 y 3 identican tres caminos diferentes desde la entrada a hasta el nodo de salida. El

azar dinmico viene dado por la diferencia de retrasos como indica la siguiente secuencia,

como podemos ver en la gura 3.17.

De aqu obtenemos un mtodo para detectar los azares dinmicos. El procedimiento a

seguir es el siguiente:

Se etiquetan los diferentes caminos que puede seguir

caminos una variable hasta el nodo de salida, tomando las

variables etiquetadas con ndice diferentes como varia-

bles distintas. Por lo que adems de no poder usar el 4

postulado, tampoco se puede usar los teoremas de idempo-

tencia, ni los asociados.

TEMA III.- ANLISIS DE CIRCUITOS COMBINACIONALES

49

Se obtiene de nuevo la frmula de productos y de sumas, y

se trata de reducir a una de las expresiones mencionadas

anteriormente, dando valores al resto de entradas. Si

dicha transformacin es posible, se dice que el circuito

tiene un azar lgico dinmico.

Si volvemos al ejemplo anterior, la frmula lgica quedara de la siguiente forma:

F = a

5

b

5

+ b

3

(b

2

+c

1

)

Segn lo anteriormente visto, slo se podrn encontrar azares dinmicos en aquellas seales

que sigan tres o ms caminos diferentes (en los que haya negados y sin negar). Por lo tanto,

solo podremos encontrar azares dinmicos en la seal B. Si pasamos la frmula a suma de pro-

ductos:

F = a

5

b

5

+ b

3

(b

2

+c

1

) = a

5

b

5

+ b

3

b

2

+ b

3

c

1

Luego se observa la presencia de un azar dinmico en la seal B cuando A=1 y C=1. La

seal C debe valer 1 ya que b

3

b

2

+ b

3

= b

3

.

Al pasar la frmula a producto de sumas, obtendramos:

F=(a

5

+b

5

)(b

3

+b

2

)(b

3

+c

1

) = (a

5

b

3

+a

5

b

2

+b

5

b

3

+b

5

b

2

)(b

3

+c

1

) =

a

5

b

3

+ a

5

b

2

c

1

+ b

5

b

3

+ b

5

b

2

c

1

F = (a

5

+b

3

)(a

5

+b

2

+c

1

)(b

5

+b

3

)(b

5

+b

2

+c

1

)

El presunto azar estara formado por el trmino (b

5

+b

3

) y otro trmino donde estuviese la

seal B en otro camino diferente, como b

2

. Los trminos (a

5

+b

3

) y (b

5

+b

2

+c

1

) deben valer

1 para que no inuyan en el comportamiento, por lo tanto, A = 1 y C = 0. Con estos valo-

res la frmula quedara:

F = (b

5

+b

3

)

a

1

a

2

a

3

F

a

1

a

2

a

3

F

Figura 3.17.- Comportamiento de los azares dinmicos.

Dpto. Ingeniera Electrnica de Sistemas Informticos y Automtica 50

que no es ninguna condicin de azar dinmico. Por lo tanto, concluimos con que slo existe un

azar dinmico. El trmino (b

5

+b

2

+c

1

) no ha sido considerado como posible camino de b

2

debido a la presencia de b

5

. sta deshabilitara la diferencia de retraso entre b

2

y b

5

, eliminado

el tercer camino de la variable b.

Una nota importante es que si no existen azares estticos, tampoco existen azares din-

micos. Esto es debido a que cualquier situacin de azar dinmico lleva implcito un azar est-

tico. Por lo tanto, para evitar situaciones de azares dinmicos, bastara con evitar todos los

azares estticos.

También podría gustarte

- Motores de Induccion Monofasicos - Manual Del EstudianteDocumento46 páginasMotores de Induccion Monofasicos - Manual Del EstudianteLiam JJAún no hay calificaciones

- Tesla Logo Tarea 1Documento15 páginasTesla Logo Tarea 1Liam JJ100% (4)

- 3 A. El Método CientíficoDocumento17 páginas3 A. El Método CientíficoSIABATO ORDUZ VICTOR HUGOAún no hay calificaciones

- Axiomas. Raiffa PDFDocumento9 páginasAxiomas. Raiffa PDFAdolfo AcostaAún no hay calificaciones

- Manual para Ser Profesional Técnico en Mecànica de Producción (2) - 1Documento46 páginasManual para Ser Profesional Técnico en Mecànica de Producción (2) - 1Liam JJAún no hay calificaciones

- Tabla de Verificacion e Inspeccion Del TornoDocumento20 páginasTabla de Verificacion e Inspeccion Del TornoLiam JJ63% (8)

- Logo Set Reset TotalDocumento49 páginasLogo Set Reset TotalLiam JJ100% (3)

- Tesla Logo Bit 2008Documento26 páginasTesla Logo Bit 2008Liam JJAún no hay calificaciones

- Logo Temporizador TotalDocumento54 páginasLogo Temporizador TotalLiam JJAún no hay calificaciones

- Tesla Logo Teoria 2008 - 2Documento28 páginasTesla Logo Teoria 2008 - 2Liam JJ100% (2)

- Tesla Logo Marca 2008Documento6 páginasTesla Logo Marca 2008Liam JJ0% (1)

- Tesla Logo Marca 2008alumnoDocumento21 páginasTesla Logo Marca 2008alumnoLiam JJAún no hay calificaciones

- Tesla Logo Contador 2008alumnoDocumento22 páginasTesla Logo Contador 2008alumnoLiam JJ100% (2)

- Tesla Logo Bit 2008Documento26 páginasTesla Logo Bit 2008Liam JJAún no hay calificaciones

- Tesla Logo Tarea 4Documento10 páginasTesla Logo Tarea 4Liam JJ0% (1)

- Tesla Logo Teoria 2008 - 1Documento44 páginasTesla Logo Teoria 2008 - 1Liam JJAún no hay calificaciones

- Tesla Logo Tarea 0Documento13 páginasTesla Logo Tarea 0Liam JJAún no hay calificaciones

- Tesla Logo Tarea 2Documento8 páginasTesla Logo Tarea 2Liam JJ100% (1)

- Tesla Logo AplicacionesDocumento31 páginasTesla Logo AplicacionesGiovanni HFAún no hay calificaciones

- Intermedios Nano PLCDocumento61 páginasIntermedios Nano PLCLiam JJAún no hay calificaciones

- UE LOGO! CompetenciaDocumento6 páginasUE LOGO! CompetenciaLiam JJAún no hay calificaciones

- Tesla Logo ElectroneumaticaDocumento6 páginasTesla Logo ElectroneumaticaLiam JJ100% (1)

- UE LOGO!-Características GeneralesDocumento15 páginasUE LOGO!-Características GeneralesLiam JJ100% (1)

- Material Impreso Curso LOGO! - SDocumento94 páginasMaterial Impreso Curso LOGO! - SLiam JJ100% (4)

- LogoDocumento235 páginasLogorampacas9214100% (3)

- Introducción Pedro Ribas Crítica Razón Pura de Immanuel KantDocumento7 páginasIntroducción Pedro Ribas Crítica Razón Pura de Immanuel KantjcalzamoraAún no hay calificaciones

- Apuntes de Matematica Elemental250 251Documento11 páginasApuntes de Matematica Elemental250 251Nick Perez GomezAún no hay calificaciones

- Numeros RealesDocumento21 páginasNumeros RealesFernanda ChavezAún no hay calificaciones

- Argument Juridica Aut8Documento3 páginasArgument Juridica Aut8yomangi_881416028Aún no hay calificaciones

- Guias de Lectura Aristoteles y PerelmanDocumento2 páginasGuias de Lectura Aristoteles y PerelmanSusana Paola LafuenteAún no hay calificaciones

- Stahl - La Lógica de Las PreguntasDocumento5 páginasStahl - La Lógica de Las PreguntasJulian BecerraAún no hay calificaciones

- ¿Qué Es La Justificación EpistémicaDocumento11 páginas¿Qué Es La Justificación EpistémicaPedro ViverosAún no hay calificaciones

- Trabajo Práctico N°1 Introudccion Al DerechoDocumento10 páginasTrabajo Práctico N°1 Introudccion Al Derecholuis ziniAún no hay calificaciones

- Ejercicios de Fórmula LógicaDocumento2 páginasEjercicios de Fórmula Lógicakarlos Olivera0% (1)

- Plantin - Un Modelo DialogalDocumento31 páginasPlantin - Un Modelo DialogalAshlar Trystan100% (1)

- Tarea 3 - Aplicación de La Teoría de Conjuntos - Wendy YepesDocumento7 páginasTarea 3 - Aplicación de La Teoría de Conjuntos - Wendy YepesLaura Mejia CastroAún no hay calificaciones

- Tabla de La Verdad RayDocumento7 páginasTabla de La Verdad Rayrayfred valeroAún no hay calificaciones

- Resumen Segundo ParcialDocumento130 páginasResumen Segundo ParcialCarina Elisabeth Suarez BrunaAún no hay calificaciones

- Matemática BásicaDocumento60 páginasMatemática BásicaMichael Donovan Quiroz Barboza100% (1)

- Circuitos Lógicos Ejercicios Resueltos2Documento13 páginasCircuitos Lógicos Ejercicios Resueltos2carlos britoAún no hay calificaciones

- Laudan La Ciencia y El Relativismo Cap 3 HolismoDocumento14 páginasLaudan La Ciencia y El Relativismo Cap 3 HolismoWalter Lomb100% (1)

- Logica Juridica UsacDocumento4 páginasLogica Juridica UsacCarlos Mbl BlAún no hay calificaciones

- Arguemntos Falsos (Falacias)Documento8 páginasArguemntos Falsos (Falacias)Guido Escobar RojasAún no hay calificaciones

- Argumentación Jurídica Sesion #04: MGTR - Jesus Manuel Chanta MoncadaDocumento22 páginasArgumentación Jurídica Sesion #04: MGTR - Jesus Manuel Chanta MoncadaJAMILLE NAOMI GRILLO RUIZAún no hay calificaciones

- DescubreDocumento25 páginasDescubreveronica parradoAún no hay calificaciones

- El Metodo CientificoDocumento5 páginasEl Metodo CientificoJOSE ALEX VASQUEZ FERNANDEZAún no hay calificaciones

- M4 Lectura 5 - Lógica SimbólicaDocumento22 páginasM4 Lectura 5 - Lógica SimbólicaiuiuiyiytitiutiutyiuAún no hay calificaciones

- Miscelánea #2 - Raz. LógicoDocumento13 páginasMiscelánea #2 - Raz. LógicowylinsAún no hay calificaciones

- Ejercicio 1 Unidad 2Documento8 páginasEjercicio 1 Unidad 2Gerson Leandro RizoAún no hay calificaciones

- Naturaleza de La Filosofía e Imaginación en Giordano BrunoDocumento11 páginasNaturaleza de La Filosofía e Imaginación en Giordano BrunoMauricioAndrésAún no hay calificaciones

- Fichas Adicionales 3ºDocumento26 páginasFichas Adicionales 3ºricardosnxzAún no hay calificaciones

- Matematica ESFORCE-signedDocumento2 páginasMatematica ESFORCE-signeddanny de la cruzAún no hay calificaciones

- X Es Racional y Distinto de Cero y Y Es Irracional Entonces X+y y Xy Son RacionalesDocumento2 páginasX Es Racional y Distinto de Cero y Y Es Irracional Entonces X+y y Xy Son RacionalesgustavogabrielmenAún no hay calificaciones