Documentos de Académico

Documentos de Profesional

Documentos de Cultura

BER Tester

Cargado por

didiTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

BER Tester

Cargado por

didiCopyright:

Formatos disponibles

IMPSAT

Capacitación & Laboratorio

BER Tester

Apr-18 BER Tester - Rel. 1 1

Agenda del curso

1. Mediciones empleando dos BER Testers

2. Mediciones empleando un BER Tester

3. Patrones

4. Velocidades

5. Interfases

6. Simulación de DTE y DCE

7. RS232 – V.35

8. G.703

9. Timing

10. Indicadores de calidad

11. Presentación de los resultados

Apr-18 BER Tester - Rel. 1 2

1. BER Tester inyectando datos

BER TESTER ENLACE

Apr-18 BER Tester - Rel. 1 3

2.Verificación de un enlace con dos BER Testers

BER TESTER ENLACE BER TESTER

Apr-18 BER Tester - Rel. 1 4

3. Verificación de un enlace con un BER Tester

BER TESTER ENLACE LOOP

Apr-18 BER Tester - Rel. 1 5

4. Patrones de datos: Uso

Patrón Uso

63 (26 -1) Recomendado para pruebas sobre canales sincrónicos y sobre canales

asincrónicos. Es el patrón seudoaleatorio menos exigente.

511 (29 - 1) Recomendado para pruebas a velocidades menores de 9.6 Kbps.

2047 (211 - 1) Adecuado para pruebas a velocidades entre 9.6 Kbps y 56 Kbps.

215 - 1 Compatible con la recomendación O.151 para velocidades de 64 Kbps,

1544 Kbps, 2048 Kbps, 3152 Kbps y 6312 Kbps. Es el standard para

el testeo de G.703.

220 - 1 Tiene una mayor exigencia que el patrón 215 - 1. No puede

usarse en modo asincrónico.

223 - 1 Es el patrón seudoaleatorio con mayor exigencia. No puede

usarse en modo asincrónico.

FOX Es el patrón asincrónico standard para las comunicaciones de teletipo.

Apr-18 BER Tester - Rel. 1 6

5. Data Rates

Fireberd HP37732A RAD LBT RAD HBT

6000

50 bps

75 bps

600 bps

38.4 Kbps

48 Kbps

2048 Kbps

15 Mbps

Apr-18 BER Tester - Rel. 1 7

6. Interfases

Fireberd HP37732A RAD LBT RAD HBT

6000

RS232 I I I P

DTE

RS232 I I N/A N/A

DCE

V35 DTE P I N/A P

V35 DCE P I N/A N/A

G.703 P I N/A P

RS449 P I N/A N/A

T1 P N/A N/A P

I = Incorporado; P = Plug-in; N/A = No disponible

Apr-18 BER Tester - Rel. 1 8

7. Selección de cada interfase

Firebed 6000 HP37732A

RS232 DTE Conectar a “TO DCE” y Seleccionar por software

Seleccionar “EMULATE DTE” “Interface DTE”

RS232 DCE Conectar a “TO DTE” y Seleccionar por software

Seleccionar “EMULATE DCE” “Interface DCE”

V35 DTE Conectarse a la interfase Seleccionar por software

V.35 (Plug in) “Interface DTE”

V35 DCE Conectar a la interfase un Seleccionar por software

cable conversor, el que la “Interface DCE”

transforma en DCE

Apr-18 BER Tester - Rel. 1 9

8. Señales importantes en RS232

Circuito de Equivalente Pin Nº Descripción Sentido

intercambio C.C.I.T.T.

BA 103 2 Transmitted DTEDCE

Data

BB 104 3 Received Data DTEDCE

DB 114 15 Transmit Clock DTEDCE

DA 113 24 External DTEDCE

Transmit Clock

DD 115 17 Receive Clock DTEDCE

Apr-18 BER Tester - Rel. 1 10

9. BER Tester simulando un DTE (1)

BER TESTER GENERANDO LIBREMENTE EL CLOCK DE TRANSMISION

- FIREBERD 6000: GEN CLK = SYNTH

- HP37732A: TX CLOCK SOURCE = INTERNAL

- RAD LBT / HBT: CLOCK INTERNAL

2 (Tx Data)

24 (Ext Tx Clk)

BER TESTER DCE

3 (Rx Data)

17 (Rx Clk)

Apr-18 BER Tester - Rel. 1 11

10. BER Tester simulando un DTE (2)

BER TESTER GENERANDO EL CLOCK DE TRANSMISION A PARTIR DE UN CLOCK

RECIBIDO DESDE EL DCE

- FIREBERD 6000: GEN CLK = INTERFACE

- HP37732A: TX CLOCK SOURCE = INTERFACE

- RAD LBT / HBT: CLOCK EXTERNAL

2 (Tx Data)

24 (Ext Tx Clk)

BER TESTER DCE

15 (Tx Clk)

3 (Rx Data)

17 (Rx Clk)

Apr-18 BER Tester - Rel. 1 12

11. BER Tester simulando un DCE (1)

BER TESTER GENERANDO LIBREMENTE EL CLOCK DE RECEPCION

- FIREBERD 6000: GEN CLK = SYNTH

- HP37732A:

* TX CLOCK SOURCE = INTERNAL

FB: si Aux Fun 7 = TT

HP: si Rx Clk Source=Intfce 2 (Tx Data) FB: si Aux Fun 7 = ST

HP: si Rx Clk Source = Internal

24 (Ext Tx Clk)

15 (Tx Clk)

BER TESTER

DTE

3 (Rx Data)

17 (Rx Clk)

En FB 6000: Si Aux Fun 7=AUTO, el FB busca el TT (24); si no lo encuentra toma el ST (15)

Apr-18 BER Tester - Rel. 1 13

12. BER Tester simulando un DCE (2)

BER TESTER GENERANDO EL CLOCK DE RECEPCION A PARTIR DEL RECIBIDO DESDE EL DTE

- FIREBERD 6000: GEN CLK = INTFC

- HP37732A:

* TX CLOCK SOURCE = INTERFACE

* RX CLOCK SOURCE = INTERFACE

2 (Tx Data)

24 (Ext Tx Clk)

17 (Rx Clk)

BER TESTER DTE

15 (Tx Clk) (no usado)

(HP)

3 (Rx Data)

Apr-18 BER Tester - Rel. 1 14

13. Señales en RS232 y Señales en V.35

RS-232 V.35

Pin 2 (Transmit Data) Par P-S (Send Data)

Pin 3 (Receive Data) Par R-T (Receive Data)

Pin 15 (Transmit Clock) Par Y-AA (Serial Clock

Transmit)

Pin 17 (Receive Clock) Par V-X (Serial Clock

Receive)

Pin 24 (External Transmit Par U-W (Serial Clock

Clock) Transmit External)

Apr-18 BER Tester - Rel. 1 15

14. BER Tester con interfase G.703 (1)

BER TESTER GENERANDO LIBREMENTE EL CLOCK DE TRANSMISION, A PARTIR DE UN

OSCILADOR INTERNO

- FIREBERD 6000: GEN CLK = SYNTH

- HP37732A: TX CLOCK SOURCE = INTERNAL

- RAD LBT / HBT: CLOCK INTERNAL

BER TESTER Tx Data

Rx Data

Apr-18 BER Tester - Rel. 1 16

15. BER Tester con interfase G.703 (2)

BER TESTER GENERANDO LIBREMENTE EL CLOCK DE TRANSMISION, A

PARTIR DE UN OSCILADOR DE LA INTERFASE (PLUG IN)

- FIREBERD 6000: GEN CLK = INTF & XTAL/RECOV=XTAL

BER TESTER Tx Data

Rx Data

Apr-18 BER Tester - Rel. 1 17

16. BER Tester con interfase G.703 (3)

BER TESTER GENERANDO EL CLOCK DE TRANSMISION A PARTIR DE UN

CLOCK RECIBIDO DESDE EL EQUIPO CONECTADO A EL

- FIREBERD 6000: GEN CLK = INTERFACE & XTAL/RECOV SW=RECOV

- HP37732A: TX CLOCK SOURCE = LOOP TIMED

- RAD LBT / HBT: CLOCK EXTERNAL

BER TESTER Tx Data

Rx Data

Apr-18 BER Tester - Rel. 1 18

17. BER Tester con interfase G.703 (4)

FIGURA 18

BER TESTER GENERANDO EL CLOCK DE TRANSMISION A PARTIR DE UN

CLOCK RECIBIDO A TRAVES DE UN CONECTOR ESPECIAL

- FIREBERD 6000: GEN CLK = BNC

- HP37732A: TX CLOCK SOURCE = EXTERNAL

BER TESTER Tx Data

Rx Data

FB: BNC Input

HP: Clock In

Apr-18 BER Tester - Rel. 1 19

18. HP 37732A: Timing (DTE) (1)

Tx Output Clock Sense: determina con qué flanco (ascendente ó descendente) del clock puesto

por el BER Tester (pin 24) cambia el dato. Este seteo no se ve afectado por la selección de “Tx

Clock “

2 (Td)

24 (Ext Tx Clk)

2 (Td)

24 (Ext Tx Clk)

Apr-18 BER Tester - Rel. 1 20

19. HP 37732A: Timing (DTE) (2)

Tx Clock Source: determina con qué flanco (ascendente ó descendente) del clock recibido por el

BER Tester (pin 15) cambia el dato

2 (Td)

15 (Tx Clk)

2 (Td)

15 (Tx Clk)

Apr-18 BER Tester - Rel. 1 21

20. HP 37732A: Timing (DTE) (3)

Rx Clock Source: determina con qué flanco (ascendente ó descendente) del clock de recepción

(pin 17) se lee el dato.

3 (Rd)

17 (Rx Clk)

3 (Rd)

17 (Rx Clk)

Apr-18 BER Tester - Rel. 1 22

21. Fireberd 6000: Timing (DTE) (1)

Auxiliary Function 1: Normal / Inverted: determina con qué flanco (ascendente ó descendente)

del clock puesto por el BER Tester cambia el dato.

2 (Td)

Normal

24 (Ext Tx Clk)

2 (Td)

Inverted

24 (Ext Tx Clk)

Apr-18 BER Tester - Rel. 1 23

22. Fireberd 6000: Timing (DTE) (2)

Rx Clock Polarity: determina con qué flanco (ascendente ó descendente) del clock de recepción

(pin 17) se lee el dato.

3 (Rd)

Normal

17 (Rx Clk)

3 (Rd)

Inverted

17 (Rx Clk)

Auto: elige el flanco correcto automáticamente

Apr-18 BER Tester - Rel. 1 24

23. HP 37732A: Timing (DCE) (1)

Tx Output Clock Sense: determina con qué flanco (ascendente ó descendente) del clock puesto

por el BER Tester (pin 17) cambia el dato. Este seteo no se ve afectado por la selección de “Tx

Clock Source”

3 (Rd)

17 (Rx Clk)

3 (Rd)

17 (Rx Clk)

Apr-18 BER Tester - Rel. 1 25

24. HP 37732A: Timing (DCE) (2)

Tx Clock Source: determina con qué flanco (ascendente ó descendente) del clock recibido por el

BER Tester (pin 24) cambia el dato

3 (Rd)

24 (Ext Tx Clk)

3 (Rd)

24 (Ext Tx Clk)

Apr-18 BER Tester - Rel. 1 26

25. HP 37732A: Timing (DCE) (3)

Rx Clock Source: determina con qué flanco (ascendente ó descendente) del clock de recepción

(pin 24 ó 15) se lee el dato.

2 (Td)

24 (Ext Tx Clok) ó 15 (Tx Clk)

2 (Td)

24 (Ext Tx Clok) ó 15 (Tx Clk)

Apr-18 BER Tester - Rel. 1 27

26. Fireberd 6000: Timing (DCE) (1)

Auxiliary Function 1: Normal / Inverted: determina con qué flanco (ascendente ó descendente)

del clock puesto por el BER Tester (pin 17) cambia el dato.

3 (Rd)

Normal

17 (Rx Clk)

3 (Rd)

Inverted

17 (Rx Clk)

Apr-18 BER Tester - Rel. 1 28

27. Fireberd 6000: Timing (DCE) (2)

Rx Clock Polarity: determina con qué flanco (ascendente ó descendente) del clock de recepción

(pin 24 ó 15) se lee el dato.

2 (Td)

Inverted

24 (Ext Tx Clk) ó 15 (Tx Clk)

2 (Td)

Normal

24 (Ext Tx Clk) ó 15 (Tx Clk)

Auto: elige el flanco correcto automáticamente

Apr-18 BER Tester - Rel. 1 29

28. Indicadores de la calidad del enlace (1)

FIREBERD 6000 HP 37732A SIGNIFICADO

CATEGORIA

“ERROR”

Bit Errors Bit Errors Número de bits erróneos contados desde el inicio de la prueba

Average BER BER Bit Errors / Bits examinados desde el inicio de la prueba

BER Bit Errors en el último intervalo de prueba / Bits examinados en el último

intervalo de prueba

Blocks Block Count Número de bloques recibidos desde el inicio de la prueba. El tamaño del

bloque es seteable.

Block Errors Block Errors Número de bloques recibidos desde el inicio de la prueba que contiene uno

ó más bits erróneos.

Average Block Error Block error Ratio Block Errors / Número de bloques examinados desde el inicio de la prueba.

Ratio (BLER)

Pattern Slips Clock Slips Número de ocasiones desde el inicio de la prueba en las que se encontró

que bits de datos se han agregado o borrado con respecto al patrón a

recibir.

Apr-18 BER Tester - Rel. 1 30

29. Indicadores de la calidad del enlace (2)

FIREBERD 6000 HP 37732A SIGNIFICADO

CATEGORIA

“PERFORMANCE”

Available seconds, % Availability (%) Según la recomendación G.821 de la C.C.I.T.T., un sistema se transforma en “disponible”

Available Seconds luego que la tasa de error medida en intervalos de 1 segundo es menor ó igual que 10 -3-

por 10 ó más segundos consecutivos. Esos 10 segundos son considerados “tiempo

disponible”. En %, se mide con relación al Nº de segundos desde la sincronización.

Unavailable seconds Unavailable seconds Según la recomendación G.821 de la C.C.I.T.T., un sistema se transforma en

“indisponible” luego que la tasa de error medida en intervalos de 1 segundo es mayor ó

igual que 10-3 por 10 ó más segundos consecutivos. Esos 10 segundos son considerados

“tiempo indisponible”.

Severely Errored Second Severely Errored Número de segundos disponibles durante el cual el BER es mayor que 10-3

Second

G.821 Errored seconds Error Seconds Número de segundos disponibles en los cuales se ha encontrado uno ó más bits erróneos

(GERR SEC)

Degraded minutes Degraded minutes Número de bloques de 60 segundos disponibles, no severamente errados, en los cuales la

tasa de error fue peor que 10-6. Resultan de restar de la cantidad total de segundos los

segundos de indisponibilidad y los segundos severamente errados, y agrupar los

segundos que quedan en bloques de 60. El BER promedio se calcula para el bloque de 60

segundos, y si es peor que 10-6, el bloque se cuenta como un minuto degradado.

Apr-18 BER Tester - Rel. 1 31

30. Indicadores de la calidad del enlace (3)

FIREBERD 6000 HP 37732A SIGNIFICADO

CATEGORIA “ALARM”

Pattern Pattern Sync Loss Número de veces que se detectó un Pattern Sync Loss.

Synchronization Loss

Count (PATT LOSS)

Receiver Data Loss Número de veces que una pérdida de sincronismo se debe a la pérdida de

Count (DAT LOSS) datos.

Receiver Clock Loss Data Loss Número de veces que una pérdida de sincronismo se debe a la pérdida de

Count (CLK LOSS) clock. (En el HP, Data Loss significa que no se recibieron clocks en modo

sincrónico, y que no se recibieron caracteres en modo asincrónico)

Clock - Data Phase Número de veces que la relación de fase entre datos y clock cambió desde

Change (C-D CHA) el inicio de la prueba

Power Loss Número de pérdidas de energía desde el último reinicio manual de la

(PWR LOSS) prueba ó último cambio importante de un switch.

Signal Loss Número de veces que se perdió la señal recibida

(SIG LOSS)

Apr-18 BER Tester - Rel. 1 32

31. Indicadores de la calidad del enlace (4)

FIREBERD 6000 HP 37732A SIGNIFICADO

CATEGORIA “TIME”

Pattern Sync Loss Pattern Loss Número de segundos durante el cual el receptor no estuvo en constante

Seconds (PATL SEC) sincronización al patrón

Elapsed Seconds Elapsed Time Número de segundos transcurridos desde el último cambio de switch

(ELAP SEC) importante ó reinicio de la prueba

Error Analysis Tiempo durante el cual se realizó el análisis de error. Este tiempo depende

Seconds (EA SEC) de la sincronización del receptor al patrón y del seteo de la función auxiliar

Nº 3 (Receiver Action Upon Sync Loss)

Time of day (TIME) Time Hora del día, en horas, minutos y segundos

Calendar Date (DATE) Date Fecha (día, mes y año)

Apr-18 BER Tester - Rel. 1 33

32. Indicadores de la calidad del enlace (5)

FIREBERD 6000 HP 37732A SIGNIFICADO

CATEGORIA “SIGNAL”

Delay (DELAY) Delay Ultimo intervalo medido entre el inicio y fin de eventos específicos. Estos

eventos se seleccionan en la función auxiliar 31.

Receiver Frequency Receive frequency Frecuencia del clock de recepción

(RCV FREQ)

Generator Frequency Transmit Frecuencia del clock del generación

(GEN FREQ) Frequency

Apr-18 BER Tester - Rel. 1 34

33. Presentación de los resultados

HP 37732A FIREBERD 6000

Panel frontal

Histograma en

pantalla

Impresora serie

Control remoto

Apr-18 BER Tester - Rel. 1 35

También podría gustarte

- Conceptos Basicos de ElectricidadDocumento36 páginasConceptos Basicos de Electricidadeetn2-taller100% (16)

- Instalaciones Electricas (1) ResidencialesDocumento60 páginasInstalaciones Electricas (1) Residencialesmelfer-130393% (42)

- Pruebas Técnicas Ipasolink Vr10Documento64 páginasPruebas Técnicas Ipasolink Vr10didi100% (1)

- GiANO HR EDocumento255 páginasGiANO HR ELalo EduAún no hay calificaciones

- Curso VR10 410L Diciembre 2015Documento111 páginasCurso VR10 410L Diciembre 2015didiAún no hay calificaciones

- Procedimiento para TaladroDocumento5 páginasProcedimiento para TaladroRicardoPastorAún no hay calificaciones

- Curso RectificadoresDocumento27 páginasCurso RectificadoresdidiAún no hay calificaciones

- Power Tronic Compact Spagna-1Documento18 páginasPower Tronic Compact Spagna-1Jaime Basquez PaccoAún no hay calificaciones

- Comisionamiento Radios Nec Ipasolink Vr10Documento39 páginasComisionamiento Radios Nec Ipasolink Vr10didi100% (2)

- Practica BERTDocumento5 páginasPractica BERTdidiAún no hay calificaciones

- Sunrise E20 BasicoDocumento11 páginasSunrise E20 BasicodidiAún no hay calificaciones

- Calculo de Enlaces 2018Documento4 páginasCalculo de Enlaces 2018didiAún no hay calificaciones

- Anexo 6 - Diagramas CASOS - 2015-08-10Documento32 páginasAnexo 6 - Diagramas CASOS - 2015-08-10didiAún no hay calificaciones

- Conceptos Basicos Sobre Electricidad2Documento24 páginasConceptos Basicos Sobre Electricidad2didi100% (1)

- Reglamento de Instalaciones Elec PDFDocumento119 páginasReglamento de Instalaciones Elec PDFCAR6Aún no hay calificaciones

- 1 GeneralDocumento16 páginas1 GeneraldidiAún no hay calificaciones

- Conceptos Basicos Sobre Electricidad1Documento41 páginasConceptos Basicos Sobre Electricidad1didiAún no hay calificaciones

- Pozo VerticalDocumento9 páginasPozo VerticaldidiAún no hay calificaciones

- 3.2.3.4 Criterios Puesta A TierraDocumento33 páginas3.2.3.4 Criterios Puesta A TierradidiAún no hay calificaciones

- Tema 4 ApoyoDocumento14 páginasTema 4 ApoyoJuan Luis Diaz AylasAún no hay calificaciones

- 3.2.3.4 Criterios Puesta A TierraDocumento33 páginas3.2.3.4 Criterios Puesta A TierradidiAún no hay calificaciones

- Pozo PlanoDocumento10 páginasPozo PlanodidiAún no hay calificaciones

- 5 TransientesDocumento21 páginas5 TransientesdidiAún no hay calificaciones

- Electronica BasicaDocumento18 páginasElectronica BasicaleonilicoAún no hay calificaciones

- Puesta A TierraDocumento14 páginasPuesta A TierraJuan EscalonaAún no hay calificaciones

- Proteccion CaidasDocumento2 páginasProteccion CaidasdidiAún no hay calificaciones

- Principios de ElectricidadDocumento22 páginasPrincipios de ElectricidadJohn Fredy Martínez Cardona100% (4)

- 06-07 Tema 2 - 4º ESO - Repaso de ElectricidadDocumento14 páginas06-07 Tema 2 - 4º ESO - Repaso de Electricidadsanisidrotecno100% (54)

- Componentes Pasivos PDFDocumento29 páginasComponentes Pasivos PDFpacobu128100% (1)

- Parte Dos Ministerio Ed EnergiaDocumento20 páginasParte Dos Ministerio Ed EnergiaBus NunezAún no hay calificaciones

- Decrpt0 PDFDocumento1 páginaDecrpt0 PDFdidiAún no hay calificaciones

- Material de Apoyo (1) INSTRUMENTOS DE MEDIDAS PDFDocumento19 páginasMaterial de Apoyo (1) INSTRUMENTOS DE MEDIDAS PDFdidiAún no hay calificaciones

- P-EC-01 Procedimiento Escrito para TrabajoDocumento2 páginasP-EC-01 Procedimiento Escrito para TrabajolisymeAún no hay calificaciones

- Diagrama de ParetoDocumento3 páginasDiagrama de ParetoAlexis OscarAún no hay calificaciones

- Catalogo BticinoDocumento28 páginasCatalogo BticinoJulio GarciaAún no hay calificaciones

- Formato Inspeccion de Grua Pluma y AccesoriosDocumento9 páginasFormato Inspeccion de Grua Pluma y AccesoriosJulian Andres Acosta CastilloAún no hay calificaciones

- Colombia-RETIE TC Mono CRS17737Documento9 páginasColombia-RETIE TC Mono CRS17737luz osorioAún no hay calificaciones

- Proyecto de Aplicación de Automatización Básica (6333) - WikifabDocumento43 páginasProyecto de Aplicación de Automatización Básica (6333) - WikifabLndIngenieriaAún no hay calificaciones

- Torno CNC y Torno ConvencionalDocumento5 páginasTorno CNC y Torno ConvencionalLuis Albert Alvarez GutierrezAún no hay calificaciones

- Comprar Colimador LáserDocumento5 páginasComprar Colimador LáserjiekeAún no hay calificaciones

- Impri MirDocumento20 páginasImpri MirCarlos FernandezAún no hay calificaciones

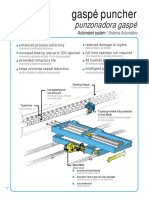

- Auto Gaspe Brochure SpanishDocumento4 páginasAuto Gaspe Brochure SpanishFelipe Andres Jaque DelgadoAún no hay calificaciones

- Analisis de Precios UnitariosDocumento14 páginasAnalisis de Precios UnitariosEliasServantesEduardoAún no hay calificaciones

- Estación TotalDocumento21 páginasEstación TotalJoseLuisQuispeAún no hay calificaciones

- Dillon xl650 Manual SpanishDocumento60 páginasDillon xl650 Manual SpanishAdrian CaduzAún no hay calificaciones

- Catalogo General Esquemas Tecnicos PDFDocumento62 páginasCatalogo General Esquemas Tecnicos PDFalex_tamayo_7Aún no hay calificaciones

- Calculo de Fusil y CablesDocumento7 páginasCalculo de Fusil y Cablesalvaro rojas100% (1)

- GENROD Catalogo 3 Jabalina PDFDocumento16 páginasGENROD Catalogo 3 Jabalina PDFDiego OjedaAún no hay calificaciones

- Torneado ResumenDocumento3 páginasTorneado ResumenPeter Harold El TigreAún no hay calificaciones

- Catalogo General - Fibra ÓpticaDocumento82 páginasCatalogo General - Fibra ÓpticaDilmer Javier Puel CruzAún no hay calificaciones

- Guia Brujo CamperDocumento55 páginasGuia Brujo CamperCumanes CumanaAún no hay calificaciones

- Identificación de Terminales de Mando de Limpia Parabrisas Frontal y PosteriorDocumento10 páginasIdentificación de Terminales de Mando de Limpia Parabrisas Frontal y PosteriorJohann Claros AnzoleagaAún no hay calificaciones

- Elementos Del MotherboardDocumento5 páginasElementos Del MotherboardEmily Yurany LedesmaAún no hay calificaciones

- Cámara de Desinfección PortátilDocumento6 páginasCámara de Desinfección PortátilJuan NuñezAún no hay calificaciones

- Taller MedicionesDocumento20 páginasTaller MedicionesAntony Quispe AlvaresAún no hay calificaciones

- Termostato Proporcional PDFDocumento6 páginasTermostato Proporcional PDFCharlie MartinezAún no hay calificaciones

- Tornillos para MaderaDocumento1 páginaTornillos para MaderaEmily AcostaAún no hay calificaciones

- Mapa Conceptual de La Arquitectura Laura Guevara PDFDocumento1 páginaMapa Conceptual de La Arquitectura Laura Guevara PDFNiyirethCangrejoSeguraAún no hay calificaciones

- Acta de Verificación de Armament0 1Documento3 páginasActa de Verificación de Armament0 1SandraFloresAún no hay calificaciones