Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Simplificación Con Mapas de Karnaugh

Cargado por

Nikole YanezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Simplificación Con Mapas de Karnaugh

Cargado por

Nikole YanezCopyright:

Formatos disponibles

Indice

1. Introduccin o 2. Marco Terico o 3. Desarrollo 3.1. Tabla de verdad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2. Mapa de Karnaugh . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3. Circuito . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4. Conclusiones 5. Bibliograf a 3 3 3 4 4 5 6 6

1.

Introduccin o

La siguiente tarea es un recurso para practicar simulaciones a travs de software y con mapas de e Karnaugh para la simplicacin de la suma de productos todo esto para la preparacin del primer o o examen del cuatrimestre. En este documento incluye, tabla de verdad, mapa de Karnaugh y una imagen para poder observar de manera grca el comportamiento del circuito. a La tarea fue desarrollada con tres programas. Digital Work 3.04 para realizar las simulaciones de las compuertas solicitadas de la tarea. Software ejecutado sobre Wine 1.3 en Ubuntu GNU/Linux 11.10. Nested 1.2.2, programa para la creacin de documentos estructurados para realizar este docuo mento.

2.

Marco Terico o

La tarea nmero dos se desarrolla primeramente haciendo una simplicacin La simplicacin u o o consiste en implementar una funcin con el menor nmero de puertas posibles(Thomas L. 2006, p. o u 214). La resolucin comienza con la tabla de verdad. Esta tabla muestra la salida para cada posible o entrada en trminos de niveles y bits correspondientes(Thomas L. 2006, p. 214) para 4 variables de e entrada (ABCD) son diecisis (24 =16) posibles combinaciones de valores, para evaluar la ecuacin se e o hace que en la tabla de verdad cada ecuacin sea igual a 1. Se procede a identicar Para cada trmino o e de la suma de productos, se coloca un 1 en el mapa de Karnaugh en la celda correspondiente al valor del producto(Thomas L. 2006, p. 231). Posterior a colocar cada trmino en el mapa de Karnaugh se identican las adyacencias o agrupae ciones para la simplicacin de la ecuacin, ya que esta nos ayuda a la simplicacin y legibilidad del o o o circuito. Podemos agrupar los mapas de Karnaugh de acuerdo con las reglas siguientes, rodeando las celdas adyacentes que contengan unos(Thomas L. 2006, p. 235) Luego de identicar la adyacencia se procede a la minimizacin Se denomina minimizacin al o o proceso que genera una expresin que contiene el menor nmero posible de trminos con el m o u e nimo nmero de variables posibles.(Thomas L. 2006, p. 214). Esta accin se realiza cancelado los valores u o opuesto por ejemplo eliminar amos A con A en el caso contrario A con A si las dos son idnticas las e copiamos para que se denan junto con las dems variables como la ecuacin nal. a o

3.

Desarrollo

El circuito a desarrollar presenta la siguiente ecuacin de suma de productos: o ABCD + ABCD + ABCD + ABCD + ABCD + ABCD

A continuacin se muestra la tabla de verdad, mapa de Karnaugh y el circuito perse desarrollados o segn la ecuacin. u o

3.1.

Tabla de verdad

La resolucin comienza con la tabla de verdad : Esta tabla muestra la salida para cada posible o entrada en trminos de niveles y bits correspodientes(Thomas L. 2006, p. 214) para 4 varibales de e entrada (ABCD) son diecisis (24 =16) posibles combinaciones de valores, para evaluar la ecuacin se e o hace que en la tabla de verdad cada ecuacin sea igual a 1. o A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Salida 0 0 1 1 0 0 0 0 1 0 1 1 1 0 0 0 Trmino producto e ABCD ABCD ABCD ABCD ABCD ABCD -

3.2.

Mapa de Karnaugh

Genera una expresin que contiene el menor nmero posible de trminos con el m o u e nimo nmero de u variables posibles.

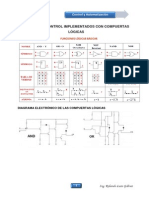

Figura 1: Mapa de Karnaugh. La simplicacin consiste en implementar una funcin con el menor nmero de puertas posibles. o o u Simplicacin = ACD + BC o

3.3.

Circuito

El circuito de suma de productos se implementa con una puerta OR y dos o ms puertas AND a a continuacin su desarrollo es el siguiente: o

Figura 2: Circuito desarrollado.

En este circuito se requiere tres puertas: dos AND, una de dos entradas y otra de tres, y una puerta OR de dos entradas. La primera puerta AND de dos entradas se utiliza para obtener BC y la segunda puerta de tres entradas se utiliza para obtener ACD. Finalmente se suman las salidas de las puertas AND con la puerta OR de dos entradas.

Figura 3: Logic History.

4.

Conclusiones

El manejo correcto de los siguientes trminos, tabla de verdad, simplicacin, mapa de karnaugh, e o adyacencia, suma de productos, variables. La utilizacin correcta del mapa de Karnaugh y terminar de comprender su funcionamiento para o la simplicacin de ecuaciones. o Un repaso del uso de las puertas AND y OR y la utilizacin de los inversores. o Aplicar los conocimientos adquiridos de la lectura del libro de Thomas L. Floy para la realizacin o de la tarea con mucha utilidad gracias a la variedad de ejercicios realizados.

5.

Bibliograf a

Libro de texto: Floyd, Thomas L. (2006). Fundamentos de sistemas digitales. Editorial Perason Prentice Hall, 9a . Edicin Espaa, Madrid. ISB 10:84-8322-085-7 o n Castro Chaves, Karol. (2012). Orientacin para el curso Organizacin de Computadores. EUNED. o o Costa Rica.

También podría gustarte

- Diseño y construcción de algoritmosDe EverandDiseño y construcción de algoritmosCalificación: 4 de 5 estrellas4/5 (6)

- Apol Matematicas Libro Rojo.Documento562 páginasApol Matematicas Libro Rojo.Pedro Goya85% (266)

- Evaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores - (Grupo1)Documento29 páginasEvaluacion Final - Escenario 8 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores - (Grupo1)Lui MoreAún no hay calificaciones

- Laboratorio - Informe - 5 Sumador y Restador CompletosDocumento3 páginasLaboratorio - Informe - 5 Sumador y Restador CompletosBryan RodriguezAún no hay calificaciones

- B3 - T8 - Ejercicios de Map Reduce PDFDocumento12 páginasB3 - T8 - Ejercicios de Map Reduce PDFLeroy DenizAún no hay calificaciones

- Practica 2 Logica DigitalDocumento7 páginasPractica 2 Logica DigitalEdison SànchezAún no hay calificaciones

- Guia de Ejercicios Algebra LinealDocumento20 páginasGuia de Ejercicios Algebra LinealNelson AlvaradoAún no hay calificaciones

- PRACTICA 4 Colector de MonedasDocumento6 páginasPRACTICA 4 Colector de MonedasHaziel DiazAún no hay calificaciones

- Fundamentos de Programación (Cuestionario 1)Documento13 páginasFundamentos de Programación (Cuestionario 1)felipe berrioAún no hay calificaciones

- 4.practica Cuatro Analisis CircuitosDocumento8 páginas4.practica Cuatro Analisis CircuitosJuliana Velásquez EstradaAún no hay calificaciones

- Circuitos, Mapas de Karnaugh, Clase ComputadoresDocumento9 páginasCircuitos, Mapas de Karnaugh, Clase ComputadoresNikole Yanez100% (1)

- Sumador de 2 BitsDocumento4 páginasSumador de 2 BitsJoan Jose100% (1)

- Reporte ConvertidorDocumento18 páginasReporte ConvertidoremanuelquintanillaAún no hay calificaciones

- Ejercicios de SEDDocumento31 páginasEjercicios de SED勵志楊Aún no hay calificaciones

- Unidad 3Documento15 páginasUnidad 3LUIS HUMBERTO DEL PRADO AGUIRREAún no hay calificaciones

- Lab 1 s12Documento14 páginasLab 1 s12Bell KunAún no hay calificaciones

- IDL2020 Pca2Documento7 páginasIDL2020 Pca2Electro MotiveAún no hay calificaciones

- U05Documento3 páginasU05aetheusdrumAún no hay calificaciones

- Circuitos ReporteDocumento7 páginasCircuitos ReporteAlex Elvis Gonzalez RabaquinoAún no hay calificaciones

- Informe Práctica IIDocumento20 páginasInforme Práctica IIKLEVER GEOVANNY CHACHAPOYA ESPINAún no hay calificaciones

- Calculadora Binaria de 3 BitDocumento19 páginasCalculadora Binaria de 3 BitRellenito0% (1)

- Problemas 3 Motores AsíncronosDocumento7 páginasProblemas 3 Motores Asíncronoswilliam flores humerezAún no hay calificaciones

- Sumador 4 BitsDocumento9 páginasSumador 4 BitsCristian GonzalezAún no hay calificaciones

- Diseño de Sumador Con ArduinoDocumento17 páginasDiseño de Sumador Con ArduinoMOC-3 oneAún no hay calificaciones

- Definición de Mapa de KarnaugDocumento15 páginasDefinición de Mapa de KarnaugDiegoAún no hay calificaciones

- Practica PLCDocumento26 páginasPractica PLCJoel OchoaAún no hay calificaciones

- PRACTICA 1.3 "Medida de La Información"Documento17 páginasPRACTICA 1.3 "Medida de La Información"luis angelAún no hay calificaciones

- Discret ADocumento13 páginasDiscret ALeonardo AlmeidaAún no hay calificaciones

- SUMADORDocumento9 páginasSUMADORJESUSAún no hay calificaciones

- Calculo de Area de Un Poligono Irregular Por Metodo Monte CarloDocumento13 páginasCalculo de Area de Un Poligono Irregular Por Metodo Monte CarlocegarciaAún no hay calificaciones

- Implementacion de Funciones LogicasDocumento31 páginasImplementacion de Funciones LogicasManuelAún no hay calificaciones

- ProyectoDocumento9 páginasProyectoKevin Emmanuel Gomez ValenciaAún no hay calificaciones

- Mapas de KarnaughDocumento9 páginasMapas de KarnaughAnzaldo Rojano MaximilianoAún no hay calificaciones

- Mapa de KarnaughDocumento13 páginasMapa de KarnaughFranklin MontañezAún no hay calificaciones

- TP2 Simplificación-2024Documento5 páginasTP2 Simplificación-2024Magali GutierrezAún no hay calificaciones

- Actividad 6Documento15 páginasActividad 6tototytamAún no hay calificaciones

- Informe Control AutomaticoDocumento21 páginasInforme Control AutomaticoJuan Francisco Vera AbarcaAún no hay calificaciones

- Decodificador Binario A HexadecimalDocumento5 páginasDecodificador Binario A HexadecimalEmmanuel E. AguïlarAún no hay calificaciones

- LABORATORIO 1 Digitales.Documento5 páginasLABORATORIO 1 Digitales.Daniela Paez BoteroAún no hay calificaciones

- Circuitos Lógicos CombinacionalesDocumento21 páginasCircuitos Lógicos CombinacionalesLuisitoAún no hay calificaciones

- Mapa de KarnaughDocumento13 páginasMapa de KarnaughSERVICIOS DOCUMENTALESAún no hay calificaciones

- Presentación Capitulo IIIDocumento70 páginasPresentación Capitulo IIIOswaldo CázaresAún no hay calificaciones

- Practica 3 - 7 Segmentos KarnaughDocumento6 páginasPractica 3 - 7 Segmentos Karnaughprofeitm100% (4)

- Convertidor BCDDocumento19 páginasConvertidor BCDDAVID JONATHANAún no hay calificaciones

- Reporte de LecturaDocumento12 páginasReporte de LecturaRosalino Mayoral LagunesAún no hay calificaciones

- Practica 2Documento19 páginasPractica 2Daniel Esteban HoyosAún no hay calificaciones

- Informe 4 Elec. DigitalDocumento11 páginasInforme 4 Elec. DigitalKevin Santiago Aguirre LondonoAún no hay calificaciones

- 11º-5 Guía Electronica Ciudadela Educativa Guìa de Trabajo en Clase y Extra Clase Ii Periodo 2023Documento12 páginas11º-5 Guía Electronica Ciudadela Educativa Guìa de Trabajo en Clase y Extra Clase Ii Periodo 2023Gilberto AparicioAún no hay calificaciones

- La Caja NegraDocumento3 páginasLa Caja NegraSamuel Cortez100% (1)

- Mapa de KarnaughDocumento16 páginasMapa de KarnaughFernando JuhaszAún no hay calificaciones

- Ejercicios SEDDocumento29 páginasEjercicios SEDAlvaroBellidoGalan100% (1)

- Informe Circuitos CombinacionalesDocumento6 páginasInforme Circuitos CombinacionalesJorge Martinez GómezAún no hay calificaciones

- Flip Flop ContadorDocumento9 páginasFlip Flop ContadorAndrésCabreraSoriaAún no hay calificaciones

- Ejercicios 3 SolDocumento13 páginasEjercicios 3 SolJohan JDAún no hay calificaciones

- Reporte - Practica de Sumador-RestadorDocumento10 páginasReporte - Practica de Sumador-RestadorPorfirio Gonzalez DelgadoAún no hay calificaciones

- Práctica 3Documento15 páginasPráctica 3Angel OrochimaruAún no hay calificaciones

- Circuitos Logicos ExplicacionDocumento4 páginasCircuitos Logicos ExplicacionSamuel CortezAún no hay calificaciones

- Cap 02Documento36 páginasCap 02Jasser CahuiAún no hay calificaciones

- Control Con Compuertas Logicas PDFDocumento27 páginasControl Con Compuertas Logicas PDFAlison ReedAún no hay calificaciones

- Investigacion 3Documento9 páginasInvestigacion 3YONATAN DANIEL ARZOLA NAVARROAún no hay calificaciones

- Derivas de complejidad: Aplicaciones y medicionesDe EverandDerivas de complejidad: Aplicaciones y medicionesAún no hay calificaciones

- Aprende a Programar en MATLABDe EverandAprende a Programar en MATLABCalificación: 3.5 de 5 estrellas3.5/5 (11)

- Álgebra abstracta aplicada en ingeniería: casos de aplicación en sistemas difusos tipo 1 y tipo 2De EverandÁlgebra abstracta aplicada en ingeniería: casos de aplicación en sistemas difusos tipo 1 y tipo 2Aún no hay calificaciones

- Navegación Anónima en Internet Con TORDocumento1 páginaNavegación Anónima en Internet Con TORNikole YanezAún no hay calificaciones

- Informe de Evaluación de Dos Videoconferencias de La Universidad Estatal A Distancia.Documento10 páginasInforme de Evaluación de Dos Videoconferencias de La Universidad Estatal A Distancia.Nikole YanezAún no hay calificaciones

- Nikole Yanez Seguridad SQLDocumento3 páginasNikole Yanez Seguridad SQLNikole YanezAún no hay calificaciones

- Proyecto Parte III - Aplicaciones de La Informática A La Educación IIDocumento11 páginasProyecto Parte III - Aplicaciones de La Informática A La Educación IINikole YanezAún no hay calificaciones

- 43 Días Que Estremecieron A El Salvador-1Documento10 páginas43 Días Que Estremecieron A El Salvador-1Nikole YanezAún no hay calificaciones

- Proyecto Parte III Aplicaciones de La Informatica en La Educacion 2015Documento13 páginasProyecto Parte III Aplicaciones de La Informatica en La Educacion 2015Nikole YanezAún no hay calificaciones

- Utilizando Tres Flip-Flops JK, Diseñe Uncontador Síncrono, Cuyo Ciclo Vaya de 0 A 7, El Resultado Tiene Que Observarse en Undecodificador de 7 Segmentos.Documento6 páginasUtilizando Tres Flip-Flops JK, Diseñe Uncontador Síncrono, Cuyo Ciclo Vaya de 0 A 7, El Resultado Tiene Que Observarse en Undecodificador de 7 Segmentos.Nikole YanezAún no hay calificaciones

- VPN Con RiseUpDocumento1 páginaVPN Con RiseUpNikole YanezAún no hay calificaciones

- Normalización, Diagrama Entidad-Relación, Base de Datos: "Registro de Incidentes de Violaciones A Defensores y Defensoras de Derechos Humanos".Documento7 páginasNormalización, Diagrama Entidad-Relación, Base de Datos: "Registro de Incidentes de Violaciones A Defensores y Defensoras de Derechos Humanos".Nikole YanezAún no hay calificaciones

- Compuertas LógicasDocumento7 páginasCompuertas LógicasNikole YanezAún no hay calificaciones

- Segundo Curso Procesador de TextosDocumento28 páginasSegundo Curso Procesador de TextosNikole YanezAún no hay calificaciones

- Diagramas de Flujo, Lógica para Programar.Documento6 páginasDiagramas de Flujo, Lógica para Programar.Nikole YanezAún no hay calificaciones

- Programa "Calculadora Bancaria"Documento26 páginasPrograma "Calculadora Bancaria"Nikole YanezAún no hay calificaciones

- Presentaciones OpenOffice Primer ModuloDocumento29 páginasPresentaciones OpenOffice Primer ModuloNikole YanezAún no hay calificaciones

- Matematica para ComputaciónDocumento5 páginasMatematica para ComputaciónNikole YanezAún no hay calificaciones

- Calcular El Intéres Simple y Compuesto. Diagrama de Flujo.Documento4 páginasCalcular El Intéres Simple y Compuesto. Diagrama de Flujo.Nikole Yanez0% (1)

- OpenOffice-Presentaciones Tercer ModuloDocumento22 páginasOpenOffice-Presentaciones Tercer ModuloNikole YanezAún no hay calificaciones

- Instalacion y Configuracion Del KeepassxDocumento9 páginasInstalacion y Configuracion Del KeepassxNikole YanezAún no hay calificaciones

- Claves SegurasDocumento6 páginasClaves SegurasNikole YanezAún no hay calificaciones

- Curso Autoasistido, Modulo IntroductorioDocumento14 páginasCurso Autoasistido, Modulo IntroductorioNikole YanezAún no hay calificaciones

- Tercer Curso de OpenOfficeDocumento24 páginasTercer Curso de OpenOfficeNikole YanezAún no hay calificaciones

- OpenOffice-Presentaciones Segundo ModuloDocumento26 páginasOpenOffice-Presentaciones Segundo ModuloNikole YanezAún no hay calificaciones

- Investigación, Jugando Identidades: Irrupción de La Mujer en El FútbolDocumento9 páginasInvestigación, Jugando Identidades: Irrupción de La Mujer en El FútbolNikole YanezAún no hay calificaciones

- Primer Curso Autoasistido Procesador de TextoDocumento34 páginasPrimer Curso Autoasistido Procesador de TextoNikole YanezAún no hay calificaciones

- Curso Autoasistido, Modulo IntroductorioDocumento14 páginasCurso Autoasistido, Modulo IntroductorioNikole YanezAún no hay calificaciones

- Vida Laboral Edición 8Documento14 páginasVida Laboral Edición 8Nikole YanezAún no hay calificaciones

- Vida Laboral AbrilDocumento40 páginasVida Laboral AbrilNikole YanezAún no hay calificaciones

- Vida Laboral Edición Numero 7Documento12 páginasVida Laboral Edición Numero 7Nikole YanezAún no hay calificaciones

- Tarea 1 LÓGICA PROPOSICIONALDocumento18 páginasTarea 1 LÓGICA PROPOSICIONALYoel Antony Matos QuispeAún no hay calificaciones

- Logica InformaticaDocumento68 páginasLogica InformaticaAgustín SantiagoAún no hay calificaciones

- Laboratorio de Codificador y DecodificadorDocumento11 páginasLaboratorio de Codificador y DecodificadorRonald Martínez RiveraAún no hay calificaciones

- Aritmetica NP Unidad 11 1Documento14 páginasAritmetica NP Unidad 11 1JMmanuelitoPalaciosAún no hay calificaciones

- Logica Proposicional PDFDocumento66 páginasLogica Proposicional PDFKAISY YAMIRA HUARANCCA QUISPEAún no hay calificaciones

- 859 Tarea2 Luna OsorioDocumento12 páginas859 Tarea2 Luna OsorioYEINERAún no hay calificaciones

- Digitales 1Documento18 páginasDigitales 1Neil Druckmann100% (1)

- Tarea - 3 - Pensamiento Logico y MatematicoDocumento12 páginasTarea - 3 - Pensamiento Logico y Matematicoluzdary garciaAún no hay calificaciones

- Logica PDFDocumento4 páginasLogica PDFRodrigo BrandAún no hay calificaciones

- Compuertas Logicas OnceptoDocumento15 páginasCompuertas Logicas OnceptoChristian Jose ValdezAún no hay calificaciones

- Actividades Unidad 1Documento3 páginasActividades Unidad 1lot.pinedaAún no hay calificaciones

- Quiz 1Documento9 páginasQuiz 1Garcia Ingeniero EdwinAún no hay calificaciones

- Anual Uni-Semana 07 RMDocumento23 páginasAnual Uni-Semana 07 RMedward VladimirovichAún no hay calificaciones

- 2 AritmeticaDocumento26 páginas2 AritmeticaSergio CHAún no hay calificaciones

- Electronica 1 Completo PDFDocumento149 páginasElectronica 1 Completo PDFmotoruaAún no hay calificaciones

- 1964 Tarea 1 Duvan Andres Bonilla MunozDocumento9 páginas1964 Tarea 1 Duvan Andres Bonilla MunozDuvan BonillaAún no hay calificaciones

- 1° Parcial Taller de Lógica y Análisis-2020-3Documento2 páginas1° Parcial Taller de Lógica y Análisis-2020-3SantiagoCarbonellZamoraAún no hay calificaciones

- Semana1 PDFDocumento10 páginasSemana1 PDFdiavolo3000Aún no hay calificaciones

- Pract 1Documento15 páginasPract 1enricsgAún no hay calificaciones

- Sesión 2 - CalculoProposicionalDocumento44 páginasSesión 2 - CalculoProposicionalDavid MalaverAún no hay calificaciones

- Parcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICODocumento25 páginasParcial - Escenario 4 - PRIMER BLOQUE-TEORICO - PRACTICOJavier Andres GonzalezAún no hay calificaciones

- DemostracionesConjuntos AlgebraSuperiorDocumento10 páginasDemostracionesConjuntos AlgebraSuperiorLuis LoeraAún no hay calificaciones

- QCA 31 en Español ManualDocumento56 páginasQCA 31 en Español ManualJo ArtAún no hay calificaciones

- Borrador Logica 'ProposicionalDocumento13 páginasBorrador Logica 'ProposicionalCobranzas UdefaAún no hay calificaciones

- Lógica ComúnDocumento7 páginasLógica Comúnusuario PalmaAún no hay calificaciones

- Presentación Lógica ComputacionalDocumento9 páginasPresentación Lógica Computacionalandresbonilla079700Aún no hay calificaciones