Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Trate05 006

Cargado por

Dvd PerezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Trate05 006

Cargado por

Dvd PerezCopyright:

Formatos disponibles

Revista Argentina de Trabajos Estudiantiles

Diseo de un Circuito Integrado Contador de Pulsos

R. J. Giraudo, J. A. Allievi, M. Di Federico, P. Julian, P. S. Mandolesi Dto. Ing. Elctrica y Computadoras, Universidad Nacional del Sur, Av. Alem 1253, Baha Blanca

ResumenEn este trabajo se presenta el diseo de un contador sincrnico de 8 bits implementado en una tecnologa CMOS estndar de 1,5m. Se abarca la arquitectura, tablas lgicas e implementacin mediante FlipFlops D (DFF). Se comentan adems el diseo esquemtico y la generacin de las mscaras necesarias para la implementacin del chip. AbstractIn this paper, the design of a synchronous 8-bit counter implemented using standard 1,5m CMOS technology is presented. Its architecture, truth tables and implementation using D FlipFlops (DFF) is covered. Finally, the schematic design and the layout needed to implement the chip are explained.

l contador que se presenta a continuacin fue diseado bajo el marco de la materia Anlisis y Diseo de Circuitos Digitales dictada en la Universidad Nacional del Sur. En innumerables aplicaciones es necesario conocer la cantidad de pulsos recibidos, por lo que circuitos de este tipo son de gran utilidad. El contador aqu presentado es de 8 bits de salida paralelo, sincrnico al flanco ascendente del reloj, y con cuenta ascendente o descendente segn el valor del pin de entrada UP/DOWN. El circuito posee una entrada de RESET sincrnica -para poner la cuenta a cero- y una seal de ENABLE, que permite inhibir la cuenta de pulsos [1]. A lo largo del trabajo se describen las distintas etapas de diseo del circuito. Se presenta su arquitectura, tablas lgicas, e implementacin mediante DFF. Adems se comentan el diseo esquemtico y la generacin de las mscaras necesarias para construir el chip. II. TECNOLOGA El CI se dise en un proceso n-well CMOS estndar de 1,5m (=0,8 m), con 2 capas de metal, 2 capas de polisilicio, opcin a transistores NPN y condensadores Pip (polisilicio sobre polisilicio) de 600 af/m [2]. Todos los transistores implementados son de tamao mnimo, siendo los PMOS de 8 m x 1,6m (W=10 , L= 2 ) y los NMOS de 4,8 m x1,6 m (W =6 , L=2 ). III. ARQUITECTURA El circuito consta de dos grandes bloques. Ambos funcionan con un reloj de simple fase, y evolucionan con el flanco ascendente del mismo. El bloque principal es un contador de pulsos de reloj.

Docentes. P. Julin est afiliado con CONICET; P. S. Mandolesi est afiliado con CIC Pcia. Bs. As.

I. INTRODUCCIN

Cuando su entrada HABILITACIN est en nivel alto, en cada pulso de reloj recibido el contador incrementa en uno su cuenta. El signo del incremento depende del valor lgico presente en el pin de entrada UP/DOWN. El segundo bloque lo constituye una mquina secuencial. Su funcin es controlar la seal HABILITACIN del bloque Contador, habilitndolo solo durante el primer perodo de reloj donde haya un pulso presente en la entrada PULSO. De esta forma se asegura que cada pulso sea contado solo una vez, independientemente de su duracin, siempre y cuando ste permanezca en la entrada durante al menos un perodo de reloj. La separacin entre dos pulsos consecutivos tambin debe cumplir esta condicin para que el bloque los reconozca como tales. IV. TABLAS LGICAS A. Bloque Contador Por simplicidad se ilustra el diseo para un contador de 4 bits. Contadores con un nmero arbitrario de bits pueden lograrse poniendo en cascada bloques de 1 bit como los aqu mostrados, o con mayor esfuerzo, realizando las tablas lgicas para todos los bits de salida. En la tabla 1 se presenta la tabla de estados para un contador ascendente, junto con los diagramas de Karnaugh correspondientes a cada salida.

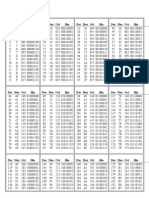

TABLA I TABLA DE ESTADOS PARA UN CONTADOR ASCENDENTE DE 4 BITS, Y MAPAS DE KARNAUGH DE LAS SALIDAS.

ESTADO Q3 Q2 Q1 Q0 Q3 ESTADO +1 Q2 Q1 Q0

Q1 Q0 Q3 Q2

Q0

00 1 1 1 1 01 0 0 0 0

+1

11 0 0 0 0 10 1 1 1 1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0

0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

00 01 11 10

Q1

Q1 Q0 Q3 Q2

+1

11 0 0 0 0 10 1 1 1 1

00 01 11 10

00 0 0 0 0

01 1 1 1 1

Q2

Q1 Q0 Q3 Q2

+1

11 1 0 0 1 10 0 1 1 0

00 01 11 10

00 0 1 1 0

01 0 1 1 0

Q3

Q1 Q0 Q3 Q2

+1

11 0 1 0 1 10 0 0 1 1

00 01 11 10

00 0 0 1 1

01 0 0 1 1

TRATE05-006

Vol. I - N 1 - Febrero 2006

27

Revista Argentina de Trabajos Estudiantiles

B.

Bloque Mquina de estados El diagrama de estados de la mquina secuencial que controla la seal HABILITACIN del contador puede verse en la Fig. 1, donde el estado A corresponde a la ausencia de un pulso en la entrada, y el estado B a su presencia.

ENABLE que permite suspender la cuenta de pulsos. Esta seal inhibe la evolucin de las salidas mediante el control de las compuertas negadoras (NOT y XOR). Ntese, comparando con la Fig. 2, el reemplazo de la compuerta NOT por una XOR (negador controlado), y la consideracin de la seal de ENABLE en las dems compuertas XOR del bloque.

Fig. 1. Diagrama de estados de la mquina secuencial. Las entradas corresponden a ENABLE y PULSO respectivamente.

V. FUNCIONES LGICAS E IMPLEMENTACIN Las reducciones de los mapas de Karnaugh presentados en la tabla 1 resultan en las siguientes funciones lgicas: Q0 +1 = QO Q1 +1 = Q1 + Q0 Q2 +1 = Q2 + (Q0.Q1) Q3 +1 = Q3 + (Q0.Q1.Q2) (1) (2) (3) (4)

Fig. 3. Lgica para una cuenta ascendente/descendente con habilitacin. En linea punteada se delimita el bloque contador de 1 bit a replicar.

La mquina de estados de la Fig. 1 se reduce a la funcin lgica HABILITACIN = ENABLE . PULSO . ESTADO +1 (9) donde ESTADO +1 = ENABLE . PULSO (10) Su implementacin con DFFC se muestra en la Fig. 4.

En la Fig. 2 se muestra la implementacin de estas funciones mediante DFF con clear (DFFC).

Fig. 4. Implementacin de la mquina de estados mediante DFFC.

VI. DISEO EN ESQUEMTICO Todas las compuertas usan lgica complementaria. El FlipFlop D contiene un reset sincrnico, y buffer interno para el reloj [3]. El diseo es modular, donde la mxima jerarqua la constituye el bloque contador de 1 bit. La conexin en cascada de este bloque permite la creacin de un contador de un nmero arbitrario de bits. VII. DISEO EN LAYOUT El bloque contador de 1 bit tiene el layout necesario para que al ser replicado y cascadeado haga conexin directa con su rplica. Adems, su ancho no excede los 194 (155,2 m). Ambas propiedades permiten colocar en el chip 8 bloques contiguos en sentido horizontal, minimizando el rea usada. En la fig. 5 se identifican, sobre su layout, los distintos componentes que constituyen el bloque contador de 1 bit. Igual ilustracin se da para la mquina de estados en la fig. 6. En el caso del bloque contador, se rotulan adems las seales para que se aprecie la inmediata conexin entre stas al momento de replicar los bloques hacia los costados.

Fig. 2. Implementacin de un contador de pulsos de reloj con cuenta ascendente usando DFFC.

Para una cuenta descendente, las funciones lgicas de cada salida se obtienen al invertir los estados con +1 en la Tabla 1. Q0 +1 = Q0 (5) Q1 +1 = Q1 + Q0 (6) Q2 +1 = Q2 + Q0.Q1 (7) Q3 +1 = Q3 + Q0.Q1.Q2 (8) Las compararaciones de (1), (2), (3) y (4) con (5), (6), (7) y (8) respectivamente muestran que, para cada salida, la lgica para una cuenta descendente y una ascendente es bastante similar. De hecho, sera idntica de no ser por la inversin del segundo operando de la funcin XOR. En la Fig. 3 se muestra la igualacin entre ambas funciones de cada salida mediante el uso de un multiplexor. Adems se incluye una seal de

TRATE05-006

Vol. I - N 1 - Febrero 2006

28

Revista Argentina de Trabajos Estudiantiles

VIII. PROTOTIPO FABRICADO El chip se mand a fabricar en un encapsulado DIP 40. Sobre el mismo chip tambin se fabricaron un conversor paralelo/serie serie/paralelo y un generador de nmeros aleatorios, con el cual se comparten algunas seales. Adems, se logr una importante reduccin en el nmero de pines utilizados mediante el multiplexado de las salidas de ambos circuitos habiendo agregado, para tal fin, un multiplexor de 16:8 y un pin de entrada CONT/GEN que lo comanda.

Fig 5. Layout de un bloque contador de 1 bit y sus componentes.

IX. CONCLUSIONES En este trabajo se presentaron los pasos involucrados en el diseo e implementacin de un contador sincrnico de 8 bits, usando tecnologa CMOS estndar de 1,5m. El proyecto fue desarrollado en la Universidad Nacional del Sur como parte de la materia Anlisis y Diseo de Circuitos Digitales. Circuitos de este tipo encuentran utilidad en innumerables aplicaciones, entre ellas divisin de frecuencias, clculo de velocidad y direccionamiento de memoria. REFERENCIAS

Fig 6. Layout de la mquina de estados y sus componentes.

El layout completo del circuito, donde se ven las rplicas del bloque contador de 1 bit, y la conexin de la mquina de estados para controlar su habilitacin, se muestra en la Fig. 7. El nmero de transistores y las dimensiones de cada bloque del layout se muestran en la Tabla II.

TABLA II NMERO DE TRANSISTORES Y DIMENSIONES PARA LOS BLOQUES DEL CIRCUITO.

[1] Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic, Digital Integrated Circuits, Second Edition, ISBN: 0-13-090996-3, Prentice Hall (1996). [2] Koyanagi, M. Kurino, H. Kang Wook, Lee Sakuma, K. Miyakawa, N. Itani, H. Tohoku, Sendai, Future system-on-silicon LSI chips Micro, IEEE, Jul/Aug 1998 Volume: 18, Issue 4. [3] Neil H. E. Weste and Kamran Eshraghian, Principles of CMOS VLSI design, Addison-Wesley EEUU (1993).

BLOQUE Not And (2 inputs) And (3 inputs) Xor Llave Mux FF D con CLR FF D sin CLR Contador 1 bit Mq. estados Completo

Trans. 2 6 8 10 2 6 25 20 47 54 430

W 17 47 63 67 17 65 194 175 194 175 1570 m 13,6 37,6 50,4 53,6 13,6 52 155,2 140 155,2 140 1256 63 60 60 60 63 60 79 79 178 243 455

H m 50,4 48 48 48 50,4 48 63,2 63,2 142,4 194,4 364

rea m2 685 1805 2419 2573 685 2496 9808 8848 22100 27216 457184

Fig 7. Layout final del circuito.

TRATE05-006

Vol. I - N 1 - Febrero 2006

29

También podría gustarte

- Distribuciones DiscretasDocumento1 páginaDistribuciones DiscretasDvd PerezAún no hay calificaciones

- Circuitos RectificadoresDocumento24 páginasCircuitos RectificadoresDvd PerezAún no hay calificaciones

- Rectificadores y Filtrospdf PDFDocumento20 páginasRectificadores y Filtrospdf PDFGlomile100% (1)

- El DiodoDocumento140 páginasEl DiodoNataliaCataldoLlanquitrufAún no hay calificaciones

- FiltrosDocumento8 páginasFiltrosMelvis MellAún no hay calificaciones

- Arduino DUE Marzo2014Documento63 páginasArduino DUE Marzo2014Sherma007100% (1)

- Marcos Perez - Máquinas Eléctricas ModernasDocumento22 páginasMarcos Perez - Máquinas Eléctricas ModernasituanguinosAún no hay calificaciones

- Control Por PWM Trifasico 2Documento16 páginasControl Por PWM Trifasico 2cindygpe100% (4)

- Caracteristicas de Motores TrifasicosDocumento33 páginasCaracteristicas de Motores TrifasicosDvd PerezAún no hay calificaciones

- Manual GalaxyDocumento16 páginasManual GalaxyfpalacioguzmanAún no hay calificaciones

- Arduino DUE Marzo2014Documento63 páginasArduino DUE Marzo2014Sherma007100% (1)

- Diseño de un inversor monofásico autónomo de baja frecuencia ajustable mediante bus DCDocumento142 páginasDiseño de un inversor monofásico autónomo de baja frecuencia ajustable mediante bus DCTitan GaboAún no hay calificaciones

- Practica 2Documento6 páginasPractica 2Dvd PerezAún no hay calificaciones

- Reporte 1 DiodosDocumento8 páginasReporte 1 DiodosDvd PerezAún no hay calificaciones

- Manual GalaxyDocumento16 páginasManual GalaxyfpalacioguzmanAún no hay calificaciones

- Diseño de Un Circuito de RelojDocumento3 páginasDiseño de Un Circuito de RelojDvd PerezAún no hay calificaciones

- Diseño de Un Circuito de RelojDocumento3 páginasDiseño de Un Circuito de RelojDvd PerezAún no hay calificaciones

- Presentacion 1Documento26 páginasPresentacion 1Dvd PerezAún no hay calificaciones

- Dec Hex Oct Bin Dec Hex Oct Bin Dec Hex Oct Bin Dec Hex Oct BinDocumento2 páginasDec Hex Oct Bin Dec Hex Oct Bin Dec Hex Oct Bin Dec Hex Oct BinDvd PerezAún no hay calificaciones

- Practica 6Documento7 páginasPractica 6Dvd PerezAún no hay calificaciones

- Manual GalaxyDocumento16 páginasManual GalaxyfpalacioguzmanAún no hay calificaciones

- TDR DCH 2023-2Documento7 páginasTDR DCH 2023-2Mariana Lizeth Junco MunozAún no hay calificaciones

- Mapa MentalDocumento2 páginasMapa Mentalcasillas1961100% (1)

- Practica 9 Lab de TermoDocumento5 páginasPractica 9 Lab de TermoToroAún no hay calificaciones

- Instrucciones Nivel Optico Leica Serie Na700Documento36 páginasInstrucciones Nivel Optico Leica Serie Na700Jose Rodriguez RosalesAún no hay calificaciones

- Challenger 2011Documento413 páginasChallenger 2011Punto de PruebasAún no hay calificaciones

- Boardingpass - 2021-09-17T164017.538Documento3 páginasBoardingpass - 2021-09-17T164017.538por colombia y el mundoAún no hay calificaciones

- Modulo NAC FLM420NACSignal - DataSheet - esES - T2831328267Documento4 páginasModulo NAC FLM420NACSignal - DataSheet - esES - T2831328267firenet colombiaAún no hay calificaciones

- Infome de Gestión 2019-2022Documento36 páginasInfome de Gestión 2019-2022Comunicaciones Ciencias Económicas Universidad de AntioquiaAún no hay calificaciones

- MC Donald'sDocumento33 páginasMC Donald'sJohan CarreñoAún no hay calificaciones

- Libro PNF Administracion PDFDocumento186 páginasLibro PNF Administracion PDFEmmanuel Peralta100% (1)

- Lina Cuadro Comparativo Tipos de PielDocumento7 páginasLina Cuadro Comparativo Tipos de Piellina marcela100% (1)

- Examen Parcial - Semana 4 - Ra - Primer Bloque - Virtual - Simulación Gerencial - (Grupo b02)Documento21 páginasExamen Parcial - Semana 4 - Ra - Primer Bloque - Virtual - Simulación Gerencial - (Grupo b02)LAURA DANIELA GARZON MARTINEZAún no hay calificaciones

- DinamitasDocumento10 páginasDinamitasVictor Ames Lara100% (1)

- HS G FlushDocumento11 páginasHS G FlushRaúl RodríguezAún no hay calificaciones

- Introducción a las máquinas herramientas: Torno, Fresadora y PlegadoraDocumento5 páginasIntroducción a las máquinas herramientas: Torno, Fresadora y PlegadoraVariverobaldiviezoAún no hay calificaciones

- Estructura Programa de Seguridad Del PacienteDocumento5 páginasEstructura Programa de Seguridad Del PacienteJackeline SuarezAún no hay calificaciones

- Los Recursos en La Ley Del Procedimiento Administrativo General y en Los Procedimientos Sectoriales - GACETADocumento342 páginasLos Recursos en La Ley Del Procedimiento Administrativo General y en Los Procedimientos Sectoriales - GACETAFiorella Alicia Ormeño100% (1)

- Leyes de Kirchhoff de circuitos eléctricos (38Documento17 páginasLeyes de Kirchhoff de circuitos eléctricos (38Nico AvalosAún no hay calificaciones

- Taller Flujos de Caja IV - ResueltoDocumento10 páginasTaller Flujos de Caja IV - Resueltosantiago otaloraAún no hay calificaciones

- Infografía - Actividad Incial - Jhon TrujilloDocumento2 páginasInfografía - Actividad Incial - Jhon Trujillomiguel100% (2)

- Según Los Criterios MicrobiológicosDocumento16 páginasSegún Los Criterios MicrobiológicosKenny Junior Mercedes RojasAún no hay calificaciones

- Diseñar Un Plan de Mantenimiento Preventivo A Una Máquina Compactadora de Bloques para Optimizar El Proceso Productivo (Página 2) - MonografiasDocumento9 páginasDiseñar Un Plan de Mantenimiento Preventivo A Una Máquina Compactadora de Bloques para Optimizar El Proceso Productivo (Página 2) - MonografiasMateo AndresAún no hay calificaciones

- Cotizacion 5833Documento1 páginaCotizacion 5833tiare pacaninsAún no hay calificaciones

- Discriminación de Precios - ResumenDocumento10 páginasDiscriminación de Precios - ResumenIomira Torre CandiaAún no hay calificaciones

- Mapeo de procesos: Guía concisa para optimizar flujosDocumento24 páginasMapeo de procesos: Guía concisa para optimizar flujosDiego Gabriel Calderón PintoAún no hay calificaciones

- Manual Plan de Saneamiento Basico Dimf 2024Documento62 páginasManual Plan de Saneamiento Basico Dimf 2024karolAún no hay calificaciones

- Manual Gestion y Facturación XLDocumento134 páginasManual Gestion y Facturación XLextradamesAún no hay calificaciones

- Obligación de Informar Enfermedades Infectocontagiosas Casarino y Cia Ltda.Documento6 páginasObligación de Informar Enfermedades Infectocontagiosas Casarino y Cia Ltda.Estefanía Manríquez RoblesAún no hay calificaciones

- Novedades Prescom - 2011Documento8 páginasNovedades Prescom - 2011Danny Quispe TapiaAún no hay calificaciones

- 4767-Texto Del Artículo-18284-1-10-20130305Documento14 páginas4767-Texto Del Artículo-18284-1-10-20130305Jean Carlos Jimenez HuillcaAún no hay calificaciones