Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Trabajo Final1 - VHDL

Cargado por

Elyel Surco MDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Trabajo Final1 - VHDL

Cargado por

Elyel Surco MCopyright:

Formatos disponibles

Trabajo encargado Diseo Electrnico 1. Describa los cinco tipos de unidades de diseo en VHDL. Entity declaration (declaracin de entidad).

Architecture (arquitectura). Configuration (configuracin). Package declaration (declaracin de paquete). Package body (cuerpo de paquete). 1. Determine cules son las unidades de diseo necesarias para realizar un programa en VHDL. Las ms necesarias son: declaracin de entidad, paquete y configuracin. 2. Mencione las unidades de diseo primarias y secundarias. Declaracin de entidad, paquete y configuracin son la unidades primarias, mientras que la arquitectura y el cuerpo del paquete son unidades de diseo secundario. Declaracin de entidades 3. Describa el significado de una entidad y cul es su palabra reservada. Una entidad es la abstraccin de un circuito, ya sea desde un complejo sistema electrnico o una simple puerta lgica. La entidad nicamente describe la forma externa del circuito, en ella se enumeran las entradas y las salidas del diseo. Una entidad es anloga a un smbolo esquemtico en los diagramas electrnicos, el cual describe las conexiones del dispositivo hacia el resto del diseo. Define externamente al circuito o subcircuito. Nombre y nmero de puertos, tipos de datos de entrada y salida. Tienes toda la informacin necesaria para conectar tu circuito a otros circuitos.

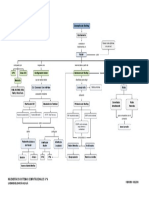

1. En la siguiente declaracin de entidad indique:

a) b) c) d)

El nombre de la entidad: seleccin. Los puertos de entrada: x. El puerto de salida: f. El tipo de dato:std_logic_vector.

6.- seale cuales de los siguientes identificadores son correctos o incorrectos, colocando en lneas de respuesta la letra C o T respectivamente. Llogico desp_lazac Con_trol n_ivel.....c Pagina architecture.c Registro s_uma#.............t 2suma res ta.t 7.- declare la entidad para el siguiente ciruito.

Library ieee; Use ieee.std_logic_1164.all; Entity DEMO is port ( A,B:in std_logic; D:out std_logic); end DEMO; 8.-declare la identidad para el siguiente circuito.

Library ieee; Use ieee.std_logic_1164.all; Entity PROMEDIO is port ( A,B:in std_logic_vector(0 to 2); C:out std_logic_vector(0 to 2) ); end PROMEDIO; 9,- Describa una libreria en vhdl. Una librera en VHDL es un lugar en donde se guarda la informacin relacionada con un diseo determinado. Al comienzo de cada diseo

el compilador crea automticamente una biblioteca llamada WORK con este objetivo. Adems de esta biblioteca particular existen otras bibliotecas de tipo general que contienen un conjunto de definiciones que pueden utilizarse en cualquier diseo. Un ejemplo de biblioteca general es la llamada Library IEEE, que contiene definiciones estndar para VHDL. Para utilizar una biblioteca general es necesario escribir su nombre al inicio del programa, por eso es muy comn que en la primera lnea de un diseo en VHDL aparezca escrito "Library IEEE", de sta forma dicha biblioteca se hace visible para el diseo. 10.-indique el significado de la siguiente expresin: Use ieee.std_logic_1164.all; 11.- declare la entidad del circuito multiplexor de 4:1 utilizando la lbreria Use ieee.std_logic_1164.all;

library ieee; use ieee.std_logic_1164.all; entity mux4x1 is port (E0,E1,E2,E3,S0,S1:in std_logic; F:out std_logic); end mux4x1; 12) Mediante un estilo funcional, programe en VHDL el funcionamiento de una lama para para cdigo morse que encienda la luz al presionar un botn y la apague al soltarlo a) library ieee; use ieee.std_logic_1164.all; entity codigo_morse is port(

a,b,c,d:in std_logic; f:out std_logic ); end codigo_morse; architecture funcional of codigo_morse is begin f<='1'when(a='0' and b='0' and c='1' and d='1')else '1'when(a='0' and b='1' and c='1' and d='0')else '1'when(a='0' and b='0' and c='1' and d='1')else '1'when(a='1' and b='1' and c='0' and d='0')else '0'when(a='0' and b='0' and c='0' and d='1')else '0'when(a='0' and b='0' and c='1' and d='0')else '0'when(a='0' and b='1' and c='0' and d='0')else '0'; end funcional; b)

c)

13) Con un estilo funcional, programe en VHDL el funcionamiento del motor de un ventilador en que el motor gire en un sentido al presionar el botn a en direccin contraria al oprimir b. a) library ieee;

use ieee.std_logic_1164.all; entity ventilador is port( a,b:in bit;selec1,selec2:in bit;salida:out bit); end ventilador; architecture funcional of ventilador is begin process(a,b,selec1,selec2) begin if(selec1='0')then salida<=a; else salida<=b; end if; if(selec2='0')then salida<=b; else salida<=a; end if; end process; end funcional; b)

c) c.1) Giro del Ventilador en una direccin

c.2) Giro del Ventilador en direccin Contraria

14.-con base a la tabla de verdad y mediante la declaracin when else describa el funcionamiento de las siguientes entradas nor, nor exclusivo. Nor library ieee; use ieee.std_logic_1164.all; entity com_nor is port( a,b:in std_logic; f:out std_logic); end com_nor; architecture funcion of com_nor is begin f<='1'when(a='0' and b='0')else '0'; end funcion;

Nor exclusivo library ieee; use ieee.std_logic_1164.all; entity com_xnor is port( a,b:in std_logic; f:out std_logic); end com_xnor; architecture funcion of com_xnor is begin f<='1'when(a='0' and b='0')else '1'when(a='1' and b='1')else

'0'; end funcion;

También podría gustarte

- Ruby On Rails-Completo - En.es PDFDocumento31 páginasRuby On Rails-Completo - En.es PDFbhugosAún no hay calificaciones

- Ejemplos Practicos VHDLDocumento18 páginasEjemplos Practicos VHDLEduardo Garcia Breijo84% (25)

- Manual Programacion ArduinoDocumento70 páginasManual Programacion Arduinofaasa83% (6)

- Practica Contador Del 0 Al 99Documento6 páginasPractica Contador Del 0 Al 99Richard EdwardAún no hay calificaciones

- Manejo de Imagenes Con C#Documento11 páginasManejo de Imagenes Con C#Alberto Moreno CuevaAún no hay calificaciones

- Ejercicios Unidad2Documento14 páginasEjercicios Unidad2Jhony Rojas100% (3)

- Implementación de funciones lógicas mediante PAL y VHDLDocumento12 páginasImplementación de funciones lógicas mediante PAL y VHDLgustavogomez4505Aún no hay calificaciones

- Fpga y PLD, VHDL y VerilogDocumento6 páginasFpga y PLD, VHDL y VerilogLuis PintadoAún no hay calificaciones

- VHDLDocumento24 páginasVHDLErik RomeroAún no hay calificaciones

- Portal CautivoDocumento23 páginasPortal CautivoOctavio Enrique Oropeza100% (1)

- Proyecto Final VHDLDocumento14 páginasProyecto Final VHDLFortino50% (2)

- Resolución de Problemas Mediante ComputadorasDocumento6 páginasResolución de Problemas Mediante Computadorasraquel121415Aún no hay calificaciones

- Maquinas de Estados Mealy VHDLDocumento20 páginasMaquinas de Estados Mealy VHDLFrancisco Javier Herrera Hernandez60% (5)

- Actividad 2 VHDLDocumento7 páginasActividad 2 VHDLLuisPugga100% (1)

- Alu VHDLDocumento21 páginasAlu VHDLFrodo AlejandroAún no hay calificaciones

- Curso - Introduccion Al PLC Micro 1Documento6 páginasCurso - Introduccion Al PLC Micro 1Manigoldo De la Cruz100% (2)

- Contador Gray VHDLDocumento5 páginasContador Gray VHDLIsraelDeLaRosaAún no hay calificaciones

- Teclado matricial: decodificación con circuitos TTL y 74C922Documento14 páginasTeclado matricial: decodificación con circuitos TTL y 74C922Edwin Gandhy Flores Gómez0% (1)

- Ejercicios de VHDL para ExamenDocumento16 páginasEjercicios de VHDL para ExamenLuisangelmtz Mtz57% (7)

- Circuitos aritméticos binariosDocumento76 páginasCircuitos aritméticos binariosChampa Jiménez de CostanillasAún no hay calificaciones

- Digitalizacion de SeñalesDocumento9 páginasDigitalizacion de SeñalesCamila Erazo FigueroaAún no hay calificaciones

- Diseno SecuencialDocumento28 páginasDiseno SecuencialJacqueline Ponce Pinos100% (4)

- Programación de Circuitos Lógicos en VHDLDocumento26 páginasProgramación de Circuitos Lógicos en VHDLCheynAún no hay calificaciones

- Diseño Logico Secuencial Con VHDLDocumento43 páginasDiseño Logico Secuencial Con VHDLENIC-AITCG100% (1)

- Aplicaciones Con VHDLDocumento6 páginasAplicaciones Con VHDLViny Pazmiño50% (2)

- Practica 2 PicoBlazeDocumento24 páginasPractica 2 PicoBlazeAntonio David EscobarAún no hay calificaciones

- Multimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásDocumento9 páginasMultimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásArmando Campos SalazarAún no hay calificaciones

- Tutorial para Programar en XilinxxDocumento23 páginasTutorial para Programar en XilinxxJuan Guillermo Medina PrietoAún no hay calificaciones

- Diseño sistemas combinacionales VHDLDocumento18 páginasDiseño sistemas combinacionales VHDLrevolver707Aún no hay calificaciones

- Ejercicios Resueltos VHDL2006Documento13 páginasEjercicios Resueltos VHDL2006elfrich50% (2)

- Practica 4de ErasmoDocumento8 páginasPractica 4de ErasmoSamantha GaliciaAún no hay calificaciones

- Unit 2 - Clasificacion Por Estructura PLCDocumento26 páginasUnit 2 - Clasificacion Por Estructura PLCJaret GarciaAún no hay calificaciones

- VHDL ProyectosDocumento92 páginasVHDL ProyectosLander Arturo Rubio JuarezAún no hay calificaciones

- Reporte de Practica 8 ALUDocumento9 páginasReporte de Practica 8 ALUDavid Hernández Osorio100% (1)

- Laboratorio Latch Flip Flops MAEFNDocumento28 páginasLaboratorio Latch Flip Flops MAEFNItaloCardenasAún no hay calificaciones

- Practica 6 Diseño DigitalDocumento7 páginasPractica 6 Diseño DigitalPandaAún no hay calificaciones

- Practica 1 VHDLDocumento15 páginasPractica 1 VHDLCARLOS MARTINEZ100% (1)

- Ejercicios de electrónica de potencia en microrred autónomaDocumento6 páginasEjercicios de electrónica de potencia en microrred autónomaRicardo BarrionuevoAún no hay calificaciones

- Informe 7Documento33 páginasInforme 7Jonathan RuizAún no hay calificaciones

- Ejercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialDocumento7 páginasEjercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialWilmer Villegas CodenaAún no hay calificaciones

- Diseño de Contador SíncronoDocumento9 páginasDiseño de Contador SíncronoPrograma Ingeniería de Sistemas100% (2)

- Divisor de 4 Bits en VHDLDocumento5 páginasDivisor de 4 Bits en VHDLJorge Almaguer100% (1)

- Cerradura ElectronicaDocumento7 páginasCerradura ElectronicazhinisimoAún no hay calificaciones

- Informe Programas Con With SelectDocumento13 páginasInforme Programas Con With SelectKathleen LeblancAún no hay calificaciones

- Manual Pic SimulatorDocumento59 páginasManual Pic Simulatorjaniro74Aún no hay calificaciones

- Programar PIC18F4550 para mostrar oración en LCD 16x2Documento10 páginasProgramar PIC18F4550 para mostrar oración en LCD 16x2Edward MedinaAún no hay calificaciones

- Informe 9Documento5 páginasInforme 9Johanna AverosAún no hay calificaciones

- Arquitectura de Computadoras Multiciclo 2015Documento56 páginasArquitectura de Computadoras Multiciclo 2015Bman100% (2)

- Convertidor de Digital Analogico DAC Red EscaleraDocumento2 páginasConvertidor de Digital Analogico DAC Red Escalerabrta29Aún no hay calificaciones

- VHDL diseño y síntesis de circuitos digitalesDocumento24 páginasVHDL diseño y síntesis de circuitos digitalesJorge RamirezAún no hay calificaciones

- Contador Ascendente y Descendente en VHDLDocumento12 páginasContador Ascendente y Descendente en VHDLStephany BradburyAún no hay calificaciones

- GalDocumento17 páginasGalMox HernandezAún no hay calificaciones

- Guía4 SDI-1 2018Documento6 páginasGuía4 SDI-1 2018Jesus SJAún no hay calificaciones

- Presentacion PLDsDocumento112 páginasPresentacion PLDsAlejandro BejaranoAún no hay calificaciones

- Tema 10 Multiplexores y DemultiplexoresDocumento23 páginasTema 10 Multiplexores y DemultiplexoresCarlos juan carlosAún no hay calificaciones

- Parte 12 VHDL Lenguaje de Descripcion de Hardware EnviarDocumento110 páginasParte 12 VHDL Lenguaje de Descripcion de Hardware Enviarhoola100% (2)

- Resolucion Examen FinalDocumento8 páginasResolucion Examen FinalGustavo Cadillo RamirezAún no hay calificaciones

- Microcontrolador 8051 interrupcionesDocumento23 páginasMicrocontrolador 8051 interrupcionesElvaroAún no hay calificaciones

- Coria Rodrigo PracticaOrganizacionyArquitecturaDocumento9 páginasCoria Rodrigo PracticaOrganizacionyArquitecturaRodrigo CoriaAún no hay calificaciones

- ED Lab01 Operaciones Con Bits v32Documento11 páginasED Lab01 Operaciones Con Bits v32Reynel De aguas avilesAún no hay calificaciones

- Informe VHDLDocumento14 páginasInforme VHDLIgnacio VeraAún no hay calificaciones

- 1.2 - Diseño VHDL ALUDocumento41 páginas1.2 - Diseño VHDL ALULeo MendezAún no hay calificaciones

- VHDL Exposición Secuenciales 2018Documento52 páginasVHDL Exposición Secuenciales 2018Alvaro HuanccoAún no hay calificaciones

- Lógica Programable - Parte - 1 - Intro y EntidadDocumento26 páginasLógica Programable - Parte - 1 - Intro y EntidadOliverth EnriqueAún no hay calificaciones

- Lógica Programable - Parte - 2 - ArquitecturaDocumento17 páginasLógica Programable - Parte - 2 - ArquitecturaOliverth EnriqueAún no hay calificaciones

- Diseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaDocumento37 páginasDiseño de Sistemas Electrónicos Digitales Avanzados: Ángel GrediagaHi HiutoAún no hay calificaciones

- G 463Documento178 páginasG 463Elyel Surco MAún no hay calificaciones

- Base Warbot "I CONCURSO DE ROBOTICA (Corcytec 2012) "Documento9 páginasBase Warbot "I CONCURSO DE ROBOTICA (Corcytec 2012) "Elyel Surco MAún no hay calificaciones

- Base Robot Soccer "I CONCURSO DE ROBOTICA (Corcytec 2012) "Documento8 páginasBase Robot Soccer "I CONCURSO DE ROBOTICA (Corcytec 2012) "Elyel Surco MAún no hay calificaciones

- Bases Robot Sumo "I CONCURSO DE ROBOTICA (Corcytec 2012) "Documento7 páginasBases Robot Sumo "I CONCURSO DE ROBOTICA (Corcytec 2012) "Elyel Surco M100% (1)

- A Pen Dice ADocumento2 páginasA Pen Dice AElyel Surco MAún no hay calificaciones

- Base Robot Seguidor Superior "I CONCURSO DE ROBOTICA (Corcytec 2012) "Documento7 páginasBase Robot Seguidor Superior "I CONCURSO DE ROBOTICA (Corcytec 2012) "Elyel Surco MAún no hay calificaciones

- Base Robot Seguidor Colegio " I CONCURSO DE ROBOTICA (Corcytec 2012) "Documento7 páginasBase Robot Seguidor Colegio " I CONCURSO DE ROBOTICA (Corcytec 2012) "Elyel Surco MAún no hay calificaciones

- Temporizador Ton en PLC s7-200Documento3 páginasTemporizador Ton en PLC s7-200Elyel Surco MAún no hay calificaciones

- Registro Consejos EscolaresDocumento36 páginasRegistro Consejos EscolaresRingo Montero50% (2)

- Plan Global ProgramacionDocumento7 páginasPlan Global ProgramacionCristian Gustavo VillcaAún no hay calificaciones

- Software para La Programación en AssemblerDocumento2 páginasSoftware para La Programación en AssemblerGary Candia NinaAún no hay calificaciones

- ResumenDocumento16 páginasResumendarrell huamaniAún no hay calificaciones

- CCNA II: Conceptos de RoutingDocumento1 páginaCCNA II: Conceptos de RoutingMiguel García AlcaláAún no hay calificaciones

- Rubrica para Evaluar Visual Basic NETDocumento1 páginaRubrica para Evaluar Visual Basic NETJohanna Beatriz RosalesAún no hay calificaciones

- Delphi - OpenOffice Calc Desde DelphiDocumento16 páginasDelphi - OpenOffice Calc Desde DelphiYasser N.Aún no hay calificaciones

- Taller Geovisor FinalDocumento31 páginasTaller Geovisor Finalser_altesco100% (1)

- Evolución de Las Bases de DatosDocumento6 páginasEvolución de Las Bases de DatosVictor Alonso Hernandez Flores100% (1)

- Vacantes MayoDocumento3 páginasVacantes MayoUlisesRdzAún no hay calificaciones

- Análisis taller sitio web 40Documento2 páginasAnálisis taller sitio web 40Pablo Damian CotoiaAún no hay calificaciones

- RECURSIVIDADDocumento44 páginasRECURSIVIDADGabriela OyervidesAún no hay calificaciones

- Informe Servicio SambaDocumento14 páginasInforme Servicio SambaJeff G. MaqueraAún no hay calificaciones

- 6 - 6.7 ArqDocumento22 páginas6 - 6.7 Arqbyron guerreroAún no hay calificaciones

- Proyecto MahjongDocumento2 páginasProyecto MahjongGustavo Rojas ValdiviaAún no hay calificaciones

- Registros de CorrimientoDocumento7 páginasRegistros de CorrimientoRoberto RobaldinoAún no hay calificaciones

- Guia No 6 Apache2 v3Documento25 páginasGuia No 6 Apache2 v3Llova HernandezAún no hay calificaciones

- Ordenar El Mayor de 3 Numeros en C++Documento1 páginaOrdenar El Mayor de 3 Numeros en C++Israel LaRaAún no hay calificaciones

- Introducción Sobre MicrocontroladoresDocumento23 páginasIntroducción Sobre MicrocontroladoresJose RamonAún no hay calificaciones

- Diferencia Entre Windwows y LinuxDocumento4 páginasDiferencia Entre Windwows y LinuxNormary camacho100% (1)

- Las 2 hojas de cálculo más utilizadas: Excel y Lotus 1-2-3Documento2 páginasLas 2 hojas de cálculo más utilizadas: Excel y Lotus 1-2-3oscar neiraAún no hay calificaciones

- Pseudocodigos PseintDocumento30 páginasPseudocodigos PseintCarlos Picasso0% (1)

- Introducción a la importancia del lenguaje ensambladorDocumento29 páginasIntroducción a la importancia del lenguaje ensambladormraleroAún no hay calificaciones

- Propuesta Técnica y FuncionalDocumento3 páginasPropuesta Técnica y FuncionalurielkuAún no hay calificaciones

- Practicas 11g Arquitectura Tema1Documento21 páginasPracticas 11g Arquitectura Tema1Rene Marcelo CayoAún no hay calificaciones