Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Arquitectura Del Computador Entrega Previa 2

Cargado por

Brayan TarquinoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Arquitectura Del Computador Entrega Previa 2

Cargado por

Brayan TarquinoCopyright:

Formatos disponibles

lOMoARcPSD|5636817

Arquitectura del computador - entrega previa 2

Arquitectura del Computador (Politécnico Grancolombiano)

StuDocu no está patrocinado ni avalado por ningún colegio o universidad.

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

lOMoARcPSD|5636817

Entrega 2 Semana 5 1

ARQUITECTURA DEL COMPUTADOR

Cogaria Boada Dayana Marcela, Herrera Moreno Oscar Arbey, Ortega Tabares Julio Cesar, Pinzón

Rodríguez Emiro Esneider

I. DEFINICIÓN DE LA CANTIDAD DE REGISTROS QUE SE II. DESCRIPCIÓN BREVE DE LOS MODOS DE

USARÁN Y EL TAMAÑO DE CADA REGISTRO DIRECCIONAMIENTO QUE SERÁN POSIBLES.

Los registros de memoria son una pequeña cantidad de

memoria muy rápida en donde almacena y accedes a datos de Es el conjunto de reglas que especifican una localización

mayor frecuencia lo que permite incrementar la velocidad del (posición) del dato usado durante la ejecución de una

un programa en ejecución instrucción.

La mayoría de las arquitecturas de computadora emplean El microprocesador desempeña una función con facilidad

registros, moviendo datos desde la memoria principal hacia los debido a que usa un modo de direccionamiento el cual

registros, se opera sobre éstos, y el resultado es movido especifica la forma en que se interpreta la información.

nuevamente a la memoria principal.[1]

• Directo a registro

Registro Descripcion

X Registro acumulador,usandolo se El registro definido por la instrucción que contiene el

operando.

produce una instrucción que ocupa un

byte menos que si se utilizaran otros

registros de uso general. Código de Registro de

operación Procesos

SP Registro de uso general,debe utilizarse

solo como puntero de pila, la cual sirve

procesador

para almacenar las direcciones de

retorno subrutinas y datos temporarios.

BX Registro base de proposito similar (se

usa para direccionamiento indirecto) Ejecución

CX Registro contador, se utilixa como

contador en bucle, en operaciones con

cadenas Figura 1 (Elaboración propia)

DX Registro de datos, se utiliza junto con el

registro AX en multiplicaciones y

• Inmediato

divisiones en la instrucción CWD(el

registro DX indica el numero de puerto Se proporciona en el byte o bytes el operando que siguen el

de entrada/salida) código de operación de la instrucción.

BP Puntero base, generalmente se utiliza

para realizar direccionamiento indirecto Código de

dentro de la pila operación Ejecución

DI Puntero destino(no se puede subdividir)

Figura 2 (Elaboración propia)

SI Puntero indice, sirve como punterp

fuente para las operaciones con • Directo

cadenas, tambien sirve para realizar

direccionamiento indirecto El byte o par de bytes que siguen al código OP de

Tabla 1 (Elaboración propia) la instrucción da el desplazamiento de 8 ó 16 bits,

que, sumado al contenido del registro DS,

determina la dirección efectiva en la que se

encuentra el dato a transferir.

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

lOMoARcPSD|5636817

Entrega 2 Semana 5 2

je L2

Código de Dirección mov eax, DWORD PTR [esp+20]

Operación de memoria test eax, eax

jle L2

mov DWORD PTR [esp+24], 0

mov DWORD PTR [esp+28], 2

Memoria jmp L3

L6:

mov eax, DWORD PTR [esp+20]

cdq

idiv DWORD PTR [esp+28]

Ejecución mov eax, edx

test eax, eax

Figura 3 (Elaboración propia) jne L4

mov DWORD PTR [esp+24], 1

L4:

add DWORD PTR [esp+28], 1

III. TRADUCCIÓN DEL PROGRAMA DE ALTO NIVEL (ENTREGA

L3:

1) AL LENGUAJE ENSAMBLADOR QUE HAN CONSTRUIDO,

mov eax, DWORD PTR [esp+20]

USANDO SU PROPIO CONJUNTO DE INSTRUCCIONES

cmp DWORD PTR [esp+28], eax

file "primo.c" jge L5

.intel_syntax noprefix cmp DWORD PTR [esp+24], 1

.text jne L6

.def ___main; .scl 2; .type 32; .endef L5:

.section .rdata,"dr" cmp DWORD PTR [esp+24], 0

LC0: jne L7

.ascii "\12Numero.....: \0" mov eax, DWORD PTR [esp+20]

LC1: mov DWORD PTR [esp+4], eax

.ascii " %d\0" mov DWORD PTR [esp], OFFSET FLAT:LC2

LC2: call _printf

.ascii "\12El numero %d es primo\0" jmp L2

LC3: L7:

.ascii "\12El numero %d no es primo\0" mov eax, DWORD PTR [esp+20]

.text mov DWORD PTR [esp+4], eax

.globl _main mov DWORD PTR [esp], OFFSET FLAT:LC3

.def _main; .scl 2; .type 32; .endef call _printf

_main: L2:

LFB17: mov eax, DWORD PTR [esp+20]

.cfi_startproc cmp eax, -1

push ebp jne L8

.cfi_def_cfa_offset 8 mov eax, 0

.cfi_offset 5, -8 leave

mov ebp, esp .cfi_restore 5

.cfi_def_cfa_register 5 .cfi_def_cfa 4, 4

and esp, -16 ret

sub esp, 32 .cfi_endproc

call ___main LFE17:

mov DWORD PTR [esp+20], 0 .ident "GCC: (MinGW.org GCC-8.2.0- 3) 8.2.0"

mov DWORD PTR [esp+28], 0 .def _printf; .scl 2; .type 32; .endef

mov DWORD PTR [esp+24], 0 .def _scanf; .scl 2; .type 32; .endef

L8:

mov DWORD PTR [esp], OFFSET FLAT:LC0

call _printf

lea eax, [esp+20]

mov DWORD PTR [esp+4], eax

mov DWORD PTR [esp], OFFSET FLAT:LC1

call _scanf

mov eax, DWORD PTR [esp+20]

cmp eax, -1

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

lOMoARcPSD|5636817

Entrega 2 Semana 5 3

IV. LISTADO EN HEXA DEL BINARIO QUE REPRESENTA EL

PROGRAMA REALIZADO EN EL PUNTO 4 DE ESTA ENTREGA.

BINARIO HEXADECIMAL

10110100 B4

Figura 4 (Elaboración propia) 1 1

11001101 CD

00100001 21

10001010 8A

11111000 F8

11011000 D8

0010 2

11011111 DF

01110101 75

0011 3

11101001 E9

11100011 E3

0 0

10111011 BB

10111000 B8

0110 6

10110111 B7

0111 7

10111010 BA

10111001 B9

Figura 5 (Elaboración propia) 01001111 4F

00011000 18

01010111 57

00010000 10

10110110 B6

10111010 BA

0101 5

11101000 E8

11111101 FD

01111100 7C

11000111 C7

11111001 F9

00111001 39

01111111 7F

11000010 C2

10000000 80

11111011 FB

10011100 9C

01110100 74

1000 8

10011101 9D

10001000 88

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

lOMoARcPSD|5636817

Entrega 2 Semana 5 4

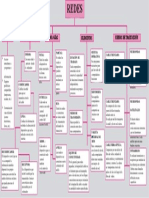

00101110 2E La entrada de 3 bits la cual se llama código de operación es

01010101 55 la encargada de manejar las 3 operaciones básicas (suma, resta

1110 0E y división) parametrizadas de acuerdo ala siguiente tabla:

01010110 56

00110000 30 Operación Código operación Decimal

10110000 B0 Suma 0 0

1010 0A Resta 1 1

10001001 89 División 10 2

10110101 B5 Tabla 3 (Elaboración propia)

01110100 74

00011110 1E

00111011 3B

11101011 EB

11101010 EA

11110111 F7

11110011 F3

01110100 74

Tabla 2 (elaboración propia)

V. ALU EN LOGISIM, QUE PUEDA EJECUTAR LAS

INSTRUCCIONES REQUERIDAS POR EL PROGRAMA.

Son dos entradas de datos de 4 bits que son los números para

operar, los cuales aparecen como valor 1 y valor 2 y el

resultado es de 5 Bits una salida de 1 bit para la referencia del

residuo.

FIGURA 5 (ELABORACIÓN PROPIA)

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

lOMoARcPSD|5636817

Entrega 2 Semana 5 5

BIBLIOGRAFIA

[1] Alegsa.com.ar (2016). Definición de Registro de memoria

Obtenido de http://www.alegsa.com.ar/Dic/registro_de_procesador.phP

[2] Creación y funcionamiento de una ALU con logisim. (2020). Retrieved 21

April 2020, obtenido de https://www.youtube.com/watch?v=xp6aXno6nac

[3] Lectura de Caracteres en Lenguaje Ensamblador. (2020). Retrieved 21

April 2020, obtenido de https://www.youtube.com/watch?v=vFnEN4s-zEw

[4] (2020). Retrieved 21 April 2020, Obtenido de

https://techlandia.com/tipos-modos-direccionamiento-computadoras-

lista_548496/

Descargado por Brayan Tarquino (brayanftm5245@hotmail.com)

También podría gustarte

- Actividad Semana 3 Lecture Notes 7Documento5 páginasActividad Semana 3 Lecture Notes 7Brayan TarquinoAún no hay calificaciones

- Gerencia de Proyectos Entrega 2Documento49 páginasGerencia de Proyectos Entrega 2Brayan TarquinoAún no hay calificaciones

- Segunda Entrega Investigacion de OperacionesDocumento14 páginasSegunda Entrega Investigacion de OperacionesBrayan TarquinoAún no hay calificaciones

- Segunda Entrega Investigacion de OperacionesDocumento14 páginasSegunda Entrega Investigacion de OperacionesBrayan TarquinoAún no hay calificaciones

- Trabajo Colaborativo Probabilidad..Documento13 páginasTrabajo Colaborativo Probabilidad..jeyson33% (3)

- Entrega Semana 3 Persistencia y Datos TransaccionalesDocumento18 páginasEntrega Semana 3 Persistencia y Datos TransaccionalesBrayan TarquinoAún no hay calificaciones

- Formato de Carta de Recomendación FamiliarDocumento1 páginaFormato de Carta de Recomendación FamiliarMaria Fernanda FajardoAún no hay calificaciones

- TC ProbabilidadDocumento4 páginasTC ProbabilidadAlexander JoyaAún no hay calificaciones

- Trabajo Colaborativo ProbabilidadDocumento16 páginasTrabajo Colaborativo ProbabilidadBrayan TarquinoAún no hay calificaciones

- In Genie Rade Software VirtualDocumento1 páginaIn Genie Rade Software VirtualyiyiAún no hay calificaciones

- Res 0060 17 (Dian) PDFDocumento63 páginasRes 0060 17 (Dian) PDFlibiaAún no hay calificaciones

- 00 Escenario 2 Metodos Numericos 2 PDFDocumento3 páginas00 Escenario 2 Metodos Numericos 2 PDFBrayan TarquinoAún no hay calificaciones

- Arquitectura de Computador Entrega 2Documento13 páginasArquitectura de Computador Entrega 2Rafael Polo75% (4)

- Encuentro Sincronico Relacion Recurrencia Sugerencias para Desarrollar Las ActividadesDocumento4 páginasEncuentro Sincronico Relacion Recurrencia Sugerencias para Desarrollar Las ActividadesJulian Gonzalez CastilloAún no hay calificaciones

- Tipos de DemocraciaDocumento1 páginaTipos de DemocraciaBrayan TarquinoAún no hay calificaciones

- IntroducciónDocumento1 páginaIntroducciónBrayan TarquinoAún no hay calificaciones

- ENSAYODocumento3 páginasENSAYOBrayan TarquinoAún no hay calificaciones

- Aporte Civica2Documento2 páginasAporte Civica2Brayan TarquinoAún no hay calificaciones

- Estructura de Datos Punto 2 B CDocumento1 páginaEstructura de Datos Punto 2 B CBrayan TarquinoAún no hay calificaciones

- Analisis PoliticoDocumento2 páginasAnalisis PoliticoBrayan TarquinoAún no hay calificaciones

- Examen PRACTICO ESTRUCTURAS DE DATOS GRUPO1 PDFDocumento16 páginasExamen PRACTICO ESTRUCTURAS DE DATOS GRUPO1 PDFBrayan TarquinoAún no hay calificaciones

- 00 Escenario 2 METODOS NUMERICOS 2 PDFDocumento3 páginas00 Escenario 2 METODOS NUMERICOS 2 PDFBrayan TarquinoAún no hay calificaciones

- 10 Modelo Carta Solicitud de Traslado EpsDocumento1 página10 Modelo Carta Solicitud de Traslado EpsMarcelo TafurAún no hay calificaciones

- Entrega N 3. Semana 7. Estructura de DatosDocumento12 páginasEntrega N 3. Semana 7. Estructura de DatosBrayan TarquinoAún no hay calificaciones

- Parcial - Escenario 4 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores)Documento27 páginasParcial - Escenario 4 - Primer Bloque-Teorico - Practico - Sistemas Digitales y Ensambladores)kuartas juanAún no hay calificaciones

- Parcial 4 Sistemas Digitales y EnsambladoresDocumento25 páginasParcial 4 Sistemas Digitales y EnsambladoresEdwinErleyQuevedoSierraAún no hay calificaciones

- 3eFjwl9wJCzZC6kW - leFdu5ZP4Cq2xvED Conceptos 20 Iniciales 20 y 20 Relaci C 3 B 3 N 20 de 20 Recurrencia PDFDocumento3 páginas3eFjwl9wJCzZC6kW - leFdu5ZP4Cq2xvED Conceptos 20 Iniciales 20 y 20 Relaci C 3 B 3 N 20 de 20 Recurrencia PDFalexisAún no hay calificaciones

- Entrega Semana 7Documento1 páginaEntrega Semana 7Brayan TarquinoAún no hay calificaciones

- Entrega 1Documento1 páginaEntrega 1Brayan TarquinoAún no hay calificaciones

- Ejercicio 2Documento6 páginasEjercicio 2Jose BernaolaAún no hay calificaciones

- Estructura de La Dirección MACDocumento1 páginaEstructura de La Dirección MACelmiguel890% (1)

- Mapa FísicoDocumento2 páginasMapa FísicojmarhbAún no hay calificaciones

- Sistemas Operativos V1Documento26 páginasSistemas Operativos V1Oscar GuerraAún no hay calificaciones

- EV2 Informe Planeacion Del Soporte TecnicoDocumento5 páginasEV2 Informe Planeacion Del Soporte TecnicoCristian Fabian Garcia Palechor100% (1)

- Principios de Comunicaciones Sistemas, Modulacion y Ruido - Rodger E. Ziemer, William H. Tranter - 7ma Ed PDFDocumento192 páginasPrincipios de Comunicaciones Sistemas, Modulacion y Ruido - Rodger E. Ziemer, William H. Tranter - 7ma Ed PDFMario100% (3)

- MC 65Documento6 páginasMC 65GNVAún no hay calificaciones

- Recursos Didacticos e Innovacion Tecnologica de Educacion Fisica y El Deporte EscolarDocumento9 páginasRecursos Didacticos e Innovacion Tecnologica de Educacion Fisica y El Deporte EscolarPetilu BelenAún no hay calificaciones

- Mapa Conceptual en Powerpoint Plantilla 14Documento1 páginaMapa Conceptual en Powerpoint Plantilla 14shioky coomerAún no hay calificaciones

- Pierre Lévy. Cibercultura y EducaciónDocumento10 páginasPierre Lévy. Cibercultura y EducaciónHernandez RigoAún no hay calificaciones

- Tic, Tac, Tep.Documento8 páginasTic, Tac, Tep.SilviaAún no hay calificaciones

- Cargador Portatil TripticoDocumento2 páginasCargador Portatil TripticoRozha Re-al0% (3)

- Puertos y SocketsDocumento25 páginasPuertos y Socketscabronico100% (2)

- Informe Comunicacion SerialDocumento21 páginasInforme Comunicacion Serialdavicho47100% (3)

- Catalogo BYTEK 2018Documento69 páginasCatalogo BYTEK 2018Hugo Moreno100% (1)

- Prueba Tecnica RMC (I - Ii - Iii)Documento11 páginasPrueba Tecnica RMC (I - Ii - Iii)DEFACRUZAún no hay calificaciones

- Curso Centralitas Telefonicas PDFDocumento11 páginasCurso Centralitas Telefonicas PDFhernan asenAún no hay calificaciones

- Tu Teléfono No Reconoce La SIM Luego de Flashear Una ROM - Te Explico Cómo Arreglarlo Cambiando El BasebandDocumento85 páginasTu Teléfono No Reconoce La SIM Luego de Flashear Una ROM - Te Explico Cómo Arreglarlo Cambiando El BasebandColo SawallischAún no hay calificaciones

- S03.s1 - MaterialDocumento43 páginasS03.s1 - Materialcesar lopezAún no hay calificaciones

- Comandera MA5600T MODDocumento32 páginasComandera MA5600T MODVlablaAún no hay calificaciones

- Rúbrica para Evaluar Una Secuencia DidácticaDocumento10 páginasRúbrica para Evaluar Una Secuencia DidácticaFernandez RoMinitaAún no hay calificaciones

- GA1 - 220501092-AA3-EV03 Diseño Del Instrumento de Recolección de InformaciónDocumento3 páginasGA1 - 220501092-AA3-EV03 Diseño Del Instrumento de Recolección de InformaciónCarolina AlzateAún no hay calificaciones

- Deber VLSIDocumento7 páginasDeber VLSIAlex LamiñoAún no hay calificaciones

- Introducción A Los MicrocontroladoresDocumento21 páginasIntroducción A Los MicrocontroladoresAndy SalidoAún no hay calificaciones

- Reglamento Estudiantil Foro PDFDocumento72 páginasReglamento Estudiantil Foro PDFfundamento generalAún no hay calificaciones

- TEMA N. 1 Red LANDocumento16 páginasTEMA N. 1 Red LANMauricio manuel Barrientos lazcanoAún no hay calificaciones

- LX20B Instrucciones ES-1.9Documento64 páginasLX20B Instrucciones ES-1.9CarlosAún no hay calificaciones

- Este Microcontrolador Está Incorporado Al Sistema EVOLUPIC Bootloader 16F88Documento3 páginasEste Microcontrolador Está Incorporado Al Sistema EVOLUPIC Bootloader 16F88terranoveAún no hay calificaciones

- Dirección de Tecnologías de La InformaciónDocumento1 páginaDirección de Tecnologías de La InformaciónHussain JadurAún no hay calificaciones