Documentos de Académico

Documentos de Profesional

Documentos de Cultura

IE-612 Compuertas 02 (Parcial I) PDF

Cargado por

nadie nadaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

IE-612 Compuertas 02 (Parcial I) PDF

Cargado por

nadie nadaCopyright:

Formatos disponibles

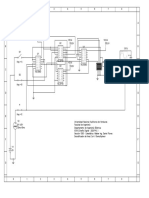

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

A VDC1 A

VDC1

2.5V

2.5V

NOT NAND

QP QP1 QP2

100u 100u 100u

B 100u 100u 100u B

S1

S6 S7

Key = A Vo

Key = A Key = B Vo

QN QN1

100u Re 100u

C V1 100u 10kΩ 100u C

V5 V6

2.5V

2.5V 2.5V

QN2

100u

100u

D D

VDC1

2.5V VDC1

E E

2.5V

NOR BUFFER

QP3

100u QP5 QP6

100u 100u 100u

100u 100u

F F

S8 S9

S10

Key = A Key = B QP4 Key = A

100u

100u QN5 QN6 Vo

V7 V8 100u 100u

V9

2.5V 2.5V 100u 100u

G 2.5V G

Vo

QN3 QN4

100u 100u Universidad Nacional Autónoma de Honduras

100u 100u Facultad de Ingeniería

Departamento de Ingeniería Eléctrica

IE-612 Diseño Digital - 2020 PAC I

H Sección 1300 - Catedrático: Máster Ing. Daniel Flores H

Compuertas 02

I I

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

También podría gustarte

- 4.2.4.4 ResueltoDocumento5 páginas4.2.4.4 ResueltoCarlos A.100% (1)

- IE-612 Guía de Ejercicios 1b (Parcial I)Documento2 páginasIE-612 Guía de Ejercicios 1b (Parcial I)Marjo RiveAún no hay calificaciones

- IE-612 Flip Flops (Parcial II) PDFDocumento16 páginasIE-612 Flip Flops (Parcial II) PDFnadie nadaAún no hay calificaciones

- IE-612 Guía de Ejercicios 1a (Parcial I) 2020 PAC I PDFDocumento2 páginasIE-612 Guía de Ejercicios 1a (Parcial I) 2020 PAC I PDFnadie nadaAún no hay calificaciones

- IE-612 Flip Flops y Latches 01 (Parcial II) PDFDocumento1 páginaIE-612 Flip Flops y Latches 01 (Parcial II) PDFnadie nadaAún no hay calificaciones

- Tarea de Teoria de La Estabilidad o Sistemas de ControlDocumento5 páginasTarea de Teoria de La Estabilidad o Sistemas de Controlnadie nadaAún no hay calificaciones

- IE-612 Guía de Repaso Online 1 (Página 1 de 2)Documento2 páginasIE-612 Guía de Repaso Online 1 (Página 1 de 2)nadie nadaAún no hay calificaciones

- Práctica #1 - Compuertas and y orDocumento4 páginasPráctica #1 - Compuertas and y ornadie nadaAún no hay calificaciones

- IE-612 Decodificador de Línea 2 A 4 - Demultiplexor (Parcial I) PDFDocumento1 páginaIE-612 Decodificador de Línea 2 A 4 - Demultiplexor (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Decodificador BDC A Decimal (Parcial I) PDFDocumento1 páginaIE-612 Decodificador BDC A Decimal (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Ejemplo de Diseño 02 (Parcial II) PDFDocumento5 páginasIE-612 Ejemplo de Diseño 02 (Parcial II) PDFJosé Enrique LozanoAún no hay calificaciones

- Ie-415 Tarea 2, Ejercicios 1.32, 1.34,1.35.Documento2 páginasIe-415 Tarea 2, Ejercicios 1.32, 1.34,1.35.nadie nadaAún no hay calificaciones

- IE-612 Decodificador en Línea de 3 A 8 (Parcial I) PDFDocumento1 páginaIE-612 Decodificador en Línea de 3 A 8 (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Compuertas y Familias Lógicas (Parcial I) PDFDocumento3 páginasIE-612 Compuertas y Familias Lógicas (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Convertidor AD 01 (Parcial I) PDFDocumento1 páginaIE-612 Convertidor AD 01 (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Compuertas 01 (Parcial I) PDFDocumento1 páginaIE-612 Compuertas 01 (Parcial I) PDFnadie nadaAún no hay calificaciones

- Problema 4 Transformadores PDFDocumento6 páginasProblema 4 Transformadores PDFRafael CollanteAún no hay calificaciones

- IE-425 Examen Parcial IIDocumento2 páginasIE-425 Examen Parcial IInadie nadaAún no hay calificaciones

- Guía de Trabajo III.2 PDFDocumento6 páginasGuía de Trabajo III.2 PDFnadie nadaAún no hay calificaciones

- Informe Terminado Radio MobileDocumento8 páginasInforme Terminado Radio Mobilenadie nadaAún no hay calificaciones

- IE-612 Sumador Binario de 4 Bits v01Documento2 páginasIE-612 Sumador Binario de 4 Bits v01Fran Eduardo AmayaAún no hay calificaciones

- Tarea 3, Maq1 Ie421Documento19 páginasTarea 3, Maq1 Ie421nadie nadaAún no hay calificaciones

- Tarea 3 GrupoN° 3 PropagacionDocumento2 páginasTarea 3 GrupoN° 3 Propagacionnadie nadaAún no hay calificaciones

- Guía de Trabajo III.1Documento1 páginaGuía de Trabajo III.1nadie nadaAún no hay calificaciones

- Circuitor 61000-3-4Documento7 páginasCircuitor 61000-3-4FredyAún no hay calificaciones

- Guía de Trabajo III.2 PDFDocumento6 páginasGuía de Trabajo III.2 PDFnadie nadaAún no hay calificaciones

- Presentacion Grupo #1Documento19 páginasPresentacion Grupo #1nadie nadaAún no hay calificaciones

- Propagacion en Espacio LibreDocumento33 páginasPropagacion en Espacio Librenadie nadaAún no hay calificaciones

- Guía de Trabajo III.1Documento1 páginaGuía de Trabajo III.1nadie nadaAún no hay calificaciones

- Raz. Matematico 2Documento8 páginasRaz. Matematico 2Alexander Zuriel Antaurco AlvaradoAún no hay calificaciones

- PDF SIstemas Operativos ResueltoDocumento3 páginasPDF SIstemas Operativos ResueltoanthonyAún no hay calificaciones

- Ocnos Revista de Estudios Sobre Lectura 21Documento144 páginasOcnos Revista de Estudios Sobre Lectura 21lorenzo_ramisAún no hay calificaciones

- Pilares Del TMPDocumento42 páginasPilares Del TMPAngie MacazanaAún no hay calificaciones

- Irracionalismo de NietzscheDocumento9 páginasIrracionalismo de NietzscheSalma Al IssaouiAún no hay calificaciones

- TEMA 1 - Primer Parcial ModelajeDocumento8 páginasTEMA 1 - Primer Parcial ModelajeAngela Silva PatiñoAún no hay calificaciones

- AlohaDocumento15 páginasAlohaGastón GaleanoAún no hay calificaciones

- DIP - II Taller Cooperación Económico-Financiera y Los Acuerdos de Bretton Woods Pais Argentina Grupo 1Documento15 páginasDIP - II Taller Cooperación Económico-Financiera y Los Acuerdos de Bretton Woods Pais Argentina Grupo 1Sandra CruzAún no hay calificaciones

- Diccionario de EmocionesDocumento2 páginasDiccionario de EmocionesMariana100% (1)

- 1 Actividad de PresuestoDocumento8 páginas1 Actividad de Presuestomayi082003Aún no hay calificaciones

- 2022-4-21 Plan Lector 2022Documento18 páginas2022-4-21 Plan Lector 2022Gregorio Guevara EstelaAún no hay calificaciones

- Nicolas Bautista Romero - 2 FInalDocumento4 páginasNicolas Bautista Romero - 2 FInalNicolás BautistaAún no hay calificaciones

- Actividad de Puntos Evaluables - Escenario 5 - PRIMER BLOQUE-TEORICO - VIRTUAL - MEDICINA PREVENTIVADocumento6 páginasActividad de Puntos Evaluables - Escenario 5 - PRIMER BLOQUE-TEORICO - VIRTUAL - MEDICINA PREVENTIVATito JavierAún no hay calificaciones

- Cultura, Paradigma e IdiosincrasiaDocumento2 páginasCultura, Paradigma e Idiosincrasia18 Lizardi Escobar Jorge IssacAún no hay calificaciones

- Mantenimiento de LuminariasDocumento10 páginasMantenimiento de LuminariasMelanie Chico SalasAún no hay calificaciones

- La Lexica y La SemanticaDocumento10 páginasLa Lexica y La SemanticaKati SkyAún no hay calificaciones

- Control de Lectura 1 - 33E Intro A La Economia 2022-IIDocumento2 páginasControl de Lectura 1 - 33E Intro A La Economia 2022-IICarlos AmayaAún no hay calificaciones

- BCMV U3 EaDocumento6 páginasBCMV U3 Eagaddielolivera23Aún no hay calificaciones

- Accion Geologica de Los GlaciaresDocumento19 páginasAccion Geologica de Los GlaciaresHarold AlexanderAún no hay calificaciones

- Diagnóstico Situacional Del Manejo Del Ganado Vacuno Lechero en El Centro Poblado de Huayre Provincia de JunínDocumento27 páginasDiagnóstico Situacional Del Manejo Del Ganado Vacuno Lechero en El Centro Poblado de Huayre Provincia de JunínRuth LCAún no hay calificaciones

- Presentacion (Lalo) AdministraciónDocumento16 páginasPresentacion (Lalo) AdministraciónCarlos CamachoAún no hay calificaciones

- Inspeccion de RodamientosDocumento2 páginasInspeccion de RodamientosElementos IndustrialesAún no hay calificaciones

- La Autoestima Cuarto PeriodoDocumento4 páginasLa Autoestima Cuarto PeriodoamandaAún no hay calificaciones

- Cartilla RCADocumento12 páginasCartilla RCAcarlosgomeznoriegaAún no hay calificaciones

- Analisis Del Reglamento 06-04 de Aplicación de La Ley 10-04Documento20 páginasAnalisis Del Reglamento 06-04 de Aplicación de La Ley 10-04Hubert PermarAún no hay calificaciones

- Cuadernillo Etica II Bim Ver 2Documento3 páginasCuadernillo Etica II Bim Ver 2mahamunidas_96710333Aún no hay calificaciones

- Trazo Planta - MergedDocumento9 páginasTrazo Planta - MergedErick De Jesus PalemonAún no hay calificaciones

- 5 Años - Mayo Unidad DidacticaDocumento13 páginas5 Años - Mayo Unidad DidacticaLuis GarnicaAún no hay calificaciones

- Testimonios Guerra Del PacificoDocumento24 páginasTestimonios Guerra Del PacificoIsidora FuentesAún no hay calificaciones

- Lógica AlgorítmicaDocumento28 páginasLógica AlgorítmicaJuan Carlos Niños Torres0% (1)