Documentos de Académico

Documentos de Profesional

Documentos de Cultura

IE-612 Flip Flops y Latches 01 (Parcial II) PDF

Cargado por

nadie nadaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

IE-612 Flip Flops y Latches 01 (Parcial II) PDF

Cargado por

nadie nadaCopyright:

Formatos disponibles

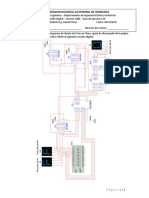

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

A A

V1signal V2signal

U1

V1signal Q1

U7 S4

S Q

V2signal

0 R ~Q

Vclock

Key = 1

SR_FF XLA1

B V1signal B

Key = A V2signal 1

Q1

U6 Vset

S1

Q2

0 U2 Q3

Key = 2 Q4

V1signal SET Q2 Q5

S Q

Key = B Vclock

CLK

C Vset C

V1 V2 V2signal R ~Q

Vreset

0V 5V 0V 5V RESET F

0.5ms 1ms 0.5ms 1ms C Q T

SR_FF_NEGSR

Vreset

D Vclock Vset D

U3

V3 Q1 Q2 Q3 Q4 Q5

V1signal SET Q3

5kHz S Q

5V Vclock

CLK

V2signal R ~Q R1 R2 R3 R4 R5

E RESET 100Ω 100Ω 100Ω 100Ω 100Ω E

SR_FF_POSSR

Vreset

LED1 LED2 LED3 LED4 LED5

S2

Vset

Vset

F Key = S F

U4

V4 V1signal SET Q4

5V Vclock S Q

EN

V2signal R ~Q

RESET

G SR_LATCH G

Vreset

S3

Vreset

Key = R

Vset

H V5 U5 H

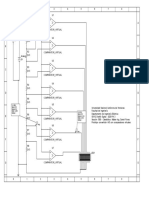

5V Universidad Nacional Autónoma de Honduras

V1signal SET Q5

S Q Facultad de Ingeniería

Vclock

EN

Departamento de Ingeniería Eléctrica

V2signal IE-612 Diseño Digital - 2020 PAC I

R ~Q

Sección 1300 - Catedrático: Máster Ing. Daniel Flores

RESET

Flip Flops y latches 01

SR_LATCH_NEGSR

I Vreset I

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

También podría gustarte

- FICHASDocumento11 páginasFICHASGretty Santisteban BarrientosAún no hay calificaciones

- Trabajo Fin de Curso Detective PrivadoDocumento3 páginasTrabajo Fin de Curso Detective PrivadoAlvaro Badia Romero0% (1)

- 4.2.4.4 ResueltoDocumento5 páginas4.2.4.4 ResueltoCarlos A.100% (1)

- IE-612 Guía de Ejercicios 1b (Parcial I)Documento2 páginasIE-612 Guía de Ejercicios 1b (Parcial I)Marjo RiveAún no hay calificaciones

- IE-612 Ejemplo de Diseño 02 (Parcial II) PDFDocumento5 páginasIE-612 Ejemplo de Diseño 02 (Parcial II) PDFJosé Enrique LozanoAún no hay calificaciones

- IE-612 Guía de Ejercicios 1a (Parcial I) 2020 PAC I PDFDocumento2 páginasIE-612 Guía de Ejercicios 1a (Parcial I) 2020 PAC I PDFnadie nadaAún no hay calificaciones

- IE-612 Flip Flops (Parcial II) PDFDocumento16 páginasIE-612 Flip Flops (Parcial II) PDFnadie nadaAún no hay calificaciones

- Tarea de Teoria de La Estabilidad o Sistemas de ControlDocumento5 páginasTarea de Teoria de La Estabilidad o Sistemas de Controlnadie nadaAún no hay calificaciones

- IE-612 Guía de Repaso Online 1 (Página 1 de 2)Documento2 páginasIE-612 Guía de Repaso Online 1 (Página 1 de 2)nadie nadaAún no hay calificaciones

- Práctica #1 - Compuertas and y orDocumento4 páginasPráctica #1 - Compuertas and y ornadie nadaAún no hay calificaciones

- IE-612 Decodificador en Línea de 3 A 8 (Parcial I) PDFDocumento1 páginaIE-612 Decodificador en Línea de 3 A 8 (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Convertidor AD 01 (Parcial I) PDFDocumento1 páginaIE-612 Convertidor AD 01 (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Decodificador de Línea 2 A 4 - Demultiplexor (Parcial I) PDFDocumento1 páginaIE-612 Decodificador de Línea 2 A 4 - Demultiplexor (Parcial I) PDFnadie nadaAún no hay calificaciones

- Ie-415 Tarea 2, Ejercicios 1.32, 1.34,1.35.Documento2 páginasIe-415 Tarea 2, Ejercicios 1.32, 1.34,1.35.nadie nadaAún no hay calificaciones

- IE-612 Decodificador BDC A Decimal (Parcial I) PDFDocumento1 páginaIE-612 Decodificador BDC A Decimal (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Compuertas 02 (Parcial I) PDFDocumento1 páginaIE-612 Compuertas 02 (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Compuertas y Familias Lógicas (Parcial I) PDFDocumento3 páginasIE-612 Compuertas y Familias Lógicas (Parcial I) PDFnadie nadaAún no hay calificaciones

- IE-612 Compuertas 01 (Parcial I) PDFDocumento1 páginaIE-612 Compuertas 01 (Parcial I) PDFnadie nadaAún no hay calificaciones

- Problema 4 Transformadores PDFDocumento6 páginasProblema 4 Transformadores PDFRafael CollanteAún no hay calificaciones

- IE-425 Examen Parcial IIDocumento2 páginasIE-425 Examen Parcial IInadie nadaAún no hay calificaciones

- Guía de Trabajo III.2 PDFDocumento6 páginasGuía de Trabajo III.2 PDFnadie nadaAún no hay calificaciones

- Informe Terminado Radio MobileDocumento8 páginasInforme Terminado Radio Mobilenadie nadaAún no hay calificaciones

- IE-612 Sumador Binario de 4 Bits v01Documento2 páginasIE-612 Sumador Binario de 4 Bits v01Fran Eduardo AmayaAún no hay calificaciones

- Tarea 3, Maq1 Ie421Documento19 páginasTarea 3, Maq1 Ie421nadie nadaAún no hay calificaciones

- Tarea 3 GrupoN° 3 PropagacionDocumento2 páginasTarea 3 GrupoN° 3 Propagacionnadie nadaAún no hay calificaciones

- Guía de Trabajo III.1Documento1 páginaGuía de Trabajo III.1nadie nadaAún no hay calificaciones

- Circuitor 61000-3-4Documento7 páginasCircuitor 61000-3-4FredyAún no hay calificaciones

- Guía de Trabajo III.2 PDFDocumento6 páginasGuía de Trabajo III.2 PDFnadie nadaAún no hay calificaciones

- Presentacion Grupo #1Documento19 páginasPresentacion Grupo #1nadie nadaAún no hay calificaciones

- Propagacion en Espacio LibreDocumento33 páginasPropagacion en Espacio Librenadie nadaAún no hay calificaciones

- Guía de Trabajo III.1Documento1 páginaGuía de Trabajo III.1nadie nadaAún no hay calificaciones

- Tarea Academica - Franz Pozo - Herramientas de La CalidadDocumento31 páginasTarea Academica - Franz Pozo - Herramientas de La CalidadCJ HerreraAún no hay calificaciones

- IVU Actividad16 NiltonHuamanBernabeDocumento13 páginasIVU Actividad16 NiltonHuamanBernabeNilton Cesar Huaman BernabeAún no hay calificaciones

- Informe SeminarioDocumento8 páginasInforme SeminarioAguijess Jessi MatelunaAún no hay calificaciones

- Trabajo IO II. 2 CorteDocumento17 páginasTrabajo IO II. 2 CorteEstefania Salazar ArenasAún no hay calificaciones

- W 26-180 MVT 606473260 Amoladora Angular EspagnolDocumento2 páginasW 26-180 MVT 606473260 Amoladora Angular EspagnolEduardo Antonio Duran SepulvedaAún no hay calificaciones

- Manual de Normas y Procedimientos Que Rigen Las Bases Legales de La MMCVDocumento56 páginasManual de Normas y Procedimientos Que Rigen Las Bases Legales de La MMCVDailiana QuintAFAún no hay calificaciones

- CASIO Lw200-7avDocumento2 páginasCASIO Lw200-7avusuarioncilloAún no hay calificaciones

- Guia y Pauta N°2Documento3 páginasGuia y Pauta N°2Guillermo Córdova CastilloAún no hay calificaciones

- Conceptos Básicos de La Ciencia Económica y Su Clasificación o SubdivisiónDocumento17 páginasConceptos Básicos de La Ciencia Económica y Su Clasificación o SubdivisiónKory CusmeAún no hay calificaciones

- PSV Nacional - CompletoDocumento32 páginasPSV Nacional - Completodownload02Aún no hay calificaciones

- Fase 4 - Grupo 41 - PrototipoDocumento24 páginasFase 4 - Grupo 41 - PrototipomauriciocAún no hay calificaciones

- SP Datasheet TK-EX4 (v2.0R)Documento3 páginasSP Datasheet TK-EX4 (v2.0R)Antenor MirandaAún no hay calificaciones

- Estructuración Del Proyecto Del Sistema en DesarrolloDocumento11 páginasEstructuración Del Proyecto Del Sistema en Desarrollojunior 1026Aún no hay calificaciones

- RESPUESTASDocumento1 páginaRESPUESTASCesar TAún no hay calificaciones

- Tesis de Seguridad OracleDocumento98 páginasTesis de Seguridad OraclegaryiiAún no hay calificaciones

- Los Video Juego Como Recurso para El AprendizajeDocumento15 páginasLos Video Juego Como Recurso para El Aprendizajelicda.rosanna altagracia gutierrez peraltaAún no hay calificaciones

- Zonas Ex y Instrumentos ExDocumento30 páginasZonas Ex y Instrumentos ExGonzalo NievasAún no hay calificaciones

- Como Hacer Un MiniLibroDocumento1 páginaComo Hacer Un MiniLibroPhilip PasmanickAún no hay calificaciones

- QML BS1901 Cilindro, Freno Delantero Izquierdo HD65 - 78 QMLDocumento2 páginasQML BS1901 Cilindro, Freno Delantero Izquierdo HD65 - 78 QMLvictor victorAún no hay calificaciones

- CV Carlos Saavedra - OkDocumento11 páginasCV Carlos Saavedra - OkCarlos Raúl Saavedra FerrerAún no hay calificaciones

- Estadistica I, Tarea 5Documento6 páginasEstadistica I, Tarea 5yokairaAún no hay calificaciones

- Actividad 2 - Informe Técnico Matriz LegalDocumento8 páginasActividad 2 - Informe Técnico Matriz LegalDayana TimanaAún no hay calificaciones

- 5 Movimiento Parabólico 1Documento6 páginas5 Movimiento Parabólico 1Carmen PárragaAún no hay calificaciones

- Comprension Lectora Cuaderno de Trabajo Secundaria 5Documento26 páginasComprension Lectora Cuaderno de Trabajo Secundaria 5jenny ivonne silupu lazoAún no hay calificaciones

- Calidad y No CalidadDocumento14 páginasCalidad y No CalidadjontueAún no hay calificaciones

- Control. Cruz Morales GuillermoDocumento3 páginasControl. Cruz Morales GuillermoGUILLERMO CRUZ MORALESAún no hay calificaciones

- Proyecto Auto Mecánica CarWashDocumento12 páginasProyecto Auto Mecánica CarWashJulio Noerlin Estherlin Aquino LeybaAún no hay calificaciones

- Técnica de Recolección de DatosDocumento5 páginasTécnica de Recolección de DatosNelly Edith Castillo MoralesAún no hay calificaciones