Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tutorial de Quartus II Web Edition Aar 44689

Tutorial de Quartus II Web Edition Aar 44689

Cargado por

Beyker Quispe AguirreDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tutorial de Quartus II Web Edition Aar 44689

Tutorial de Quartus II Web Edition Aar 44689

Cargado por

Beyker Quispe AguirreCopyright:

Formatos disponibles

TUTORIAL

Tutorial de QUARTUS II WEB EDITION (FREE) versión 14.1 DE ALTERA

Este pequeño tutorial en el uso del Quartus II de ALTERA pretende:

Que el alumno se inicie en el diseño y simulación de circuitos digitales.

Que el alumno tenga una herramienta con la cual trabajar los dispositivos lógicos

programables como los FPGAs.

Que el alumno tenga acceso a un software que puede descargar e instalar debido a su acceso

libre.

Este material va a describir el procedimiento para realizar una simulación de circuitos digitales usando

este programa.

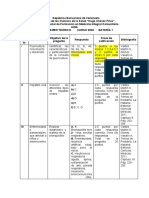

Ejemplo 1: Simulación de una compuerta XNOR.

En este ejemplo vamos a verificar el comportamiento de la compuerta XNOR según su tabla 1.

A B XNOR

0 0 1

0 1 0

1 0 0

Figura 1 1 1 1

Tabla 1 XNOR

Procedimiento:

1. Iniciar el software Quartus II.

2. Ingrese a File -> New Project Wizard, apreciaremos que se nos presenta un cuadro de dialogo,

presionar “Next”

3. Aparecerá el siguiente cuadro de dialogo de la

Figura 2 donde debemos ingresar los siguientes datos:

Ruta de trabajo ejemplo:

C:\Temp\ZE00\Ejemplo1

Nombre del Proyecto ejemplo:

CompuertaXNOR

Nombre de la entidad top del

proyecto(archivo principal del proyecto) ejemplo:

CompuertaXNOR

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

4. Seleccionamos “NEXT”, luego nos preguntará si deseamos crear un nuevo proyecto de cero o si

deseamos partir de un proyecto ya existente, seleccionar “Empty Project” luego” Next”

ura 2 5. Solicita si deseamos agregar archivos al proyecto, no modificamos nada aquí y seleccionamos

otra vez “Next”.

6. Aparecerá una venta para seleccionar el

dispositivo lógico programable con el que

vamos a trabajar. Seleccionamos en familia

“Cyclone V” y en dispositivo

“5CSEMA5F31C6”; luego hacemos clic en

Next.

7. Seleccionamos otra vez Next. Finalmente se

nos presenta un resumen de la

configuración de nuestro proyecto,

seleccionamos Finish.

Ya creamos el proyecto, ahora vamos a crear

el archivo de trabajo.

8. Ingresamos a File -> New y aparecerá el

menú de selección de la Figura 3. Seleccionamos allí la

opción “Block Diagram/Schematic File” y luego OK.

De inmediato se abre una ventana de trabajo de la

Figura 4 donde dibujaremos el diagrama esquemático

de nuestro circuito.

Figura 3

Figura 2

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

9. Hacemos clic en el botón de Symbol Tool de las herramientas ubicadas a la izquierda de

la hoja de trabajo, y se abrirá una serie de carpetas donde se muestran las diversas librerías de

elementos lógicos (Fig. 5). Abrimos la carpeta “primitives”, y luego dentro de ella la carpeta

“logic”. En esta última encontraremos todas las compuertas que necesitamos para

implementar el circuito de comprobación de la compuerta XNOR.

Figura 4

Figura 5

Figura 2

10. Una vez extraída la compuerta, es necesario definir los nodos de entrada y los nodos de salida.

Para ello agregaremos pines de entrada y de salida. Dentro de la carpeta de librerías

“primitives” seleccionamos la carpeta “pin”, donde encontramos pines de entrada, de salida y

bidireccionales.

11. Para trazar los conductores usamos el botón Orthogonal Node Tool

Al finalizar la descripción, el circuito podría quedar como se muestra en la Figura 6, debes guardarlo, se

recomienda que tenga el nombre del ejercicio “CompuertaXNOR” .

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

Figura 6

Figura 2

12. Concluido el circuito, ejecutamos Processing - > Start Compilation que se encuentra en la parte

superior de la ventana del Quartus. La PC realiza algunos cálculos al cabo de los cuales presenta

un aviso indicando si hay errores o precauciones que tomar en nuestro diseño (warnings).

Hallaremos entonces en la parte inferior una ventana (Messages) donde se listan y se detallan

los posibles errores y avisos de precaución.

Simulación del circuito:

Mediante la simulación comprobaremos el correcto funcionamiento del circuito. Una vez que

realicemos la compilación del circuito, deberemos crear un “archivo de entrada de simulación”.

Éste tiene por objeto dar valores lógicos a las entradas, creando diagramas de tiempo, para así

después apreciar las variaciones de las salidas. Entonces procedamos:

13. Ingresamos a File - > New y aparecerá el menú New, dentro del cual seleccionamos la opción

University Program VWF (Fig. 7). Se generará entonces una ventana como la de la Fig. 8.

Guardamos el archivo de extensión .vwf con el nombre sugerido “CompuertaXNOR”.

Figura 7 Figura 8

Figura 2 Figura 2

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

14. Hecho esto, presionamos el botón derecho del mouse y aparecerá una ventana donde

debemos seleccionar “Insert Node or Bus”. Aparecerá entonces la ventana donde debemos

seleccionar Node Finder. Pulsamos el botón List de ésta, aparecerá el listado de todas las

señales (o nodos) definidos en nuestro diseño (Fig. 9), para poder ser usados como puntos de

análisis en nuestra simulación, para ello presiona el >>. Dar OK y OK.

Figura 9

Figura 2

15. Podemos ahora arrastrar con el ratón y hacia la ventana de simulación (.vwf) los nodos que

queramos incluir en el análisis. Podría quedar como se muestra en la Fig. 10.

Figura 10

Figura 2

Como la simulación estará en el dominio del tiempo, es decir que se observará el

comportamiento en el tiempo de las funciones de salida, a medida que varían las señales de

entrada, entonces definiremos ahora algunos parámetros de tiempo, como el End Time y el

Grid Size. El End Time define el tiempo total de la simulación y el Grid Size define el tiempo

parcial de la simulación (tiempo para cada simulación).

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

16. Ingresamos a Edit - > Set end Time. Se muestra el cuadro de diálogo de la Fig. 11. Ingresamos

0.8 us (0.8 microsegundos) y aceptamos con “OK”.

Figura 11

Figura 2

17. Ingresamos a Edit -> Grid Size. Se muestra el cuadro de diálogo de la Fig. 12. Ingresamos el

valor de 100 ns (100 nanosegundos), y aceptamos con “OK”.

Figura 12

Figura 2

Nótese que las señales o nodos de entrada por defecto aparecen inicialmente con una línea

horizontal baja, indicando estado lógico cero. Esto no variará hasta que les asignemos valores. Las

señales de salida, en cambio, muestran una especie de trama de líneas cruzadas, lo que indica que

todavía no tienen valores definidos, ya que la simulación todavía no ha tenido lugar.

Recuerde que debe guardar el archivo con el nombre que hemos venido trabajando

“CompuertaXNOR”.

18. Volvemos a la ventana del archivos de ondas y con ayuda de la herramienta de edición de

ondas cambiamos los estados lógicos de las entradas (ver Fig. 13). Se dan valores a A y B de tal

manera que se cubran todas las variaciones de éstas.

Figura 13

Figura 2

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

TUTORIAL

19. En la parte superior ingresamos a Run Functional Simulation , observe que la maquina

realiza el proceso de simulación y presenta el resultado en pantalla

Figura 14

Figura 2

Con ello obtendremos una ventana con el diagrama de tiempos de las señales de entrada que

construimos, y también con las señales de salida que nos perite corroborar la tabla de verdad

de nuestra compuerta, como se aprecia en la Fig. 14.

LABORATORIO DE CIRCUITOS LÓGICOS COMBINACIONALES CICLO 2017-1 /ZE00

También podría gustarte

- Manual Conexion Matlab Labview DatosDocumento22 páginasManual Conexion Matlab Labview DatosDiego Frias ParedesAún no hay calificaciones

- Ensayo Sobre Las Competencias ProfesionaDocumento4 páginasEnsayo Sobre Las Competencias ProfesionaCamilo LiñanAún no hay calificaciones

- Tutorial ISE EsquDocumento20 páginasTutorial ISE EsquMarcos JimenezAún no hay calificaciones

- Tutorial+Quartus+II Parte1Documento33 páginasTutorial+Quartus+II Parte1nico_15_91Aún no hay calificaciones

- Guia-Laboratorio Calificado 01 45874Documento16 páginasGuia-Laboratorio Calificado 01 45874Richard vega marceloAún no hay calificaciones

- Automatizacion-Practica1 CorregidaDocumento21 páginasAutomatizacion-Practica1 CorregidaanakraziAún no hay calificaciones

- Guion p2Documento4 páginasGuion p2estelaAún no hay calificaciones

- Tutorial de MAX Plus 2Documento12 páginasTutorial de MAX Plus 2Tim Robles MartínezAún no hay calificaciones

- Tutorial de Diseño Con VivadoDocumento27 páginasTutorial de Diseño Con VivadoLorena NgongangAún no hay calificaciones

- SD - Informe 3Documento5 páginasSD - Informe 3Oscar FierroAún no hay calificaciones

- Práctica # 2 Conversión Analógico-Digital y Digital-AnalógicoDocumento18 páginasPráctica # 2 Conversión Analógico-Digital y Digital-AnalógicoMichelle martinez rAún no hay calificaciones

- Contador Ascendente y Descendente en VHDLDocumento12 páginasContador Ascendente y Descendente en VHDLStephany BradburyAún no hay calificaciones

- Laboratorio LOGISIMDocumento17 páginasLaboratorio LOGISIMPabloValenciaAún no hay calificaciones

- Tarea 1 SDI-SDUDocumento18 páginasTarea 1 SDI-SDUEdwin Rafael Quintanilla GuillénAún no hay calificaciones

- Apuntes Sobre SimulinkDocumento68 páginasApuntes Sobre SimulinkGaston VilchesAún no hay calificaciones

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAún no hay calificaciones

- Tutorial LTspice - EditadoDocumento15 páginasTutorial LTspice - EditadoPablo ReinadoAún no hay calificaciones

- P0 - SimulinkDocumento13 páginasP0 - SimulinkBryan SalvadorAún no hay calificaciones

- Help DocumentationDocumento45 páginasHelp DocumentationJose Antonio López FernándezAún no hay calificaciones

- MultisimDocumento13 páginasMultisimjosersAún no hay calificaciones

- SCILABDocumento15 páginasSCILABJimmy Cervantes LivonAún no hay calificaciones

- Lab ConvDocumento11 páginasLab ConvAngela CorderoAún no hay calificaciones

- L1b Simulink Control DigitalDocumento12 páginasL1b Simulink Control DigitalDiego Fernando Ramirez MuñozAún no hay calificaciones

- Reporte Practica1 Asanza - de La CruzDocumento14 páginasReporte Practica1 Asanza - de La CruzWilson De La Cruz Jr.Aún no hay calificaciones

- Tutorial Cupl UnDocumento26 páginasTutorial Cupl UnHenry Takahashi GonzalezAún no hay calificaciones

- Informe Xilinx Laboratorio Sistemas DigitalesDocumento18 páginasInforme Xilinx Laboratorio Sistemas DigitalesJosset Aldridge AguilaAún no hay calificaciones

- Practica 3Documento5 páginasPractica 3Javier Alejandro AndradeAún no hay calificaciones

- Guia Siprotec 5Documento19 páginasGuia Siprotec 5cristhian alexander hurtado melgar100% (1)

- Introducción A La Simulación de Circuito Analógico QucsDocumento5 páginasIntroducción A La Simulación de Circuito Analógico QucsCristian ValenzuelaAún no hay calificaciones

- Practica 7 - LCA1-MlbDocumento14 páginasPractica 7 - LCA1-MlbMarcus FigueroaAún no hay calificaciones

- Práctica 1Documento9 páginasPráctica 1Adair TéllezAún no hay calificaciones

- Comunicación SIEMENS LabviewDocumento20 páginasComunicación SIEMENS LabviewArmando Vázquez Ramírez100% (1)

- Investigacion de Automatizacion 9Documento12 páginasInvestigacion de Automatizacion 9Carlos BautistaAún no hay calificaciones

- Practica7 LCA1 ScilabDocumento16 páginasPractica7 LCA1 ScilabPuig123Aún no hay calificaciones

- Uso Del Software Eagle 7Documento8 páginasUso Del Software Eagle 7RoxanaLisbethAún no hay calificaciones

- Lab1 Introduccion Verilog XilinxDocumento13 páginasLab1 Introduccion Verilog XilinxRoberto Perez NezaAún no hay calificaciones

- Practicas RealizadasDocumento28 páginasPracticas RealizadasRaysha Ross Enciso RaveloAún no hay calificaciones

- Guía Básica de Laboratorio Virtual en LabviewDocumento58 páginasGuía Básica de Laboratorio Virtual en LabviewEvale Emivane ValeAún no hay calificaciones

- Manual PspiceDocumento5 páginasManual PspiceEnrique LopezAún no hay calificaciones

- Tutorial Simulador AllegroDocumento44 páginasTutorial Simulador Allegroynot666Aún no hay calificaciones

- Programacion S7-314Documento137 páginasProgramacion S7-314Luis Alberto Zapata OjedaAún no hay calificaciones

- Micro SimDocumento40 páginasMicro SimorlandorgrAún no hay calificaciones

- S05-Manual Quartus2 de Altera-Parte1Documento14 páginasS05-Manual Quartus2 de Altera-Parte1Franz Martín VILLANUEVA COCHACHINAún no hay calificaciones

- P01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaDocumento15 páginasP01 IDE MikroC Edicion Compilacion Simulacion y Depuracion de Un ProgramaaLciLAún no hay calificaciones

- Presentación Primer Programa CoDeSys 3 PDFDocumento56 páginasPresentación Primer Programa CoDeSys 3 PDFJudas Ramirez AmavizcaAún no hay calificaciones

- Ejercicio Ho Mydaq 2011Documento33 páginasEjercicio Ho Mydaq 2011Diego FabricioAún no hay calificaciones

- 3.1.señal Anlogica LabVIEW EquipoDocumento14 páginas3.1.señal Anlogica LabVIEW EquipoMaría Belén García ÁlvarezAún no hay calificaciones

- Sistemas de Control Uso Del .MatDocumento22 páginasSistemas de Control Uso Del .Matabel isaac huaytalla cotrinaAún no hay calificaciones

- Graficar Con Arduino y MatlabDocumento14 páginasGraficar Con Arduino y Matlabssdewer100% (1)

- PspiceDocumento40 páginasPspicegiancarlos1979Aún no hay calificaciones

- Practica 1 GalaxyDocumento12 páginasPractica 1 GalaxyFabian Oswaldo Abarca FloresAún no hay calificaciones

- 10 Mas 10Documento10 páginas10 Mas 10Jesús Juan Briceño AnicamaAún no hay calificaciones

- Guia Simulacion Digital en ProteusDocumento101 páginasGuia Simulacion Digital en ProteusAnonymous iAnBhvdeAún no hay calificaciones

- SD Gr10 Dylan Toapanta Informe#2Documento8 páginasSD Gr10 Dylan Toapanta Informe#2Dylan ToapantaAún no hay calificaciones

- prac2XilinxISEsumrest PDFDocumento19 páginasprac2XilinxISEsumrest PDFOliver Cruz AranibarAún no hay calificaciones

- Compilador C CCS y Simulador Proteus para Microcontroladores PICDe EverandCompilador C CCS y Simulador Proteus para Microcontroladores PICCalificación: 2.5 de 5 estrellas2.5/5 (5)

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Sistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208De EverandSistemas de control integrados en bienes de equipo y maquinaria industrial y elaboración de la documentación técnica. FMEE0208Aún no hay calificaciones

- Aprender Autocad 2012 Avanzado con 100 ejercicios prácticosDe EverandAprender Autocad 2012 Avanzado con 100 ejercicios prácticosAún no hay calificaciones

- ListaProblemas01 29939Documento3 páginasListaProblemas01 29939Cesar Danny Romero Hernandez100% (1)

- PielDocumento2 páginasPielCesar Danny Romero HernandezAún no hay calificaciones

- Guia de Practica-N-07 24413Documento8 páginasGuia de Practica-N-07 24413Cesar Danny Romero HernandezAún no hay calificaciones

- PielDocumento2 páginasPielCesar Danny Romero HernandezAún no hay calificaciones

- Técnicas de AprendizajesDocumento9 páginasTécnicas de AprendizajesHeidy María Macario MacarioAún no hay calificaciones

- Contenido de Aire Por Metodo VolumetricoDocumento5 páginasContenido de Aire Por Metodo VolumetricoElii GtAún no hay calificaciones

- Sindrome Bernard SoulierDocumento35 páginasSindrome Bernard SoulierJorge Luis Vera TrujilloAún no hay calificaciones

- Evaluación Interna y Extrerna de Los Sistemas Tecnológicos.Documento4 páginasEvaluación Interna y Extrerna de Los Sistemas Tecnológicos.americanazaret09Aún no hay calificaciones

- RE OPT62-2020 Primer Examen ParcialDocumento1 páginaRE OPT62-2020 Primer Examen ParcialHUGO SERGIO MEDINA DE LA CRUZAún no hay calificaciones

- Texto Residuos SolidosDocumento13 páginasTexto Residuos SolidosAlejandra ValenciaAún no hay calificaciones

- La Contaminacion Acústica Submarina Fuentes e Impacto Biologico SAES - WebDocumento6 páginasLa Contaminacion Acústica Submarina Fuentes e Impacto Biologico SAES - WebCamila AzuaraAún no hay calificaciones

- Trabajo Final Calculo Multivariado - CompressDocumento4 páginasTrabajo Final Calculo Multivariado - CompressNatalia Orjuela AraqueAún no hay calificaciones

- Danny - Iglesias, Tarea Semana 2 Gestiónde Remuneraciones y CompensacionesDocumento6 páginasDanny - Iglesias, Tarea Semana 2 Gestiónde Remuneraciones y Compensacionesdanny iglesiasAún no hay calificaciones

- Documentos Legales y AdministrativosDocumento3 páginasDocumentos Legales y Administrativoslili rodriguezAún no hay calificaciones

- El Sistema Circulatorio Posee Como Función El Distribuir Los NutrientesDocumento7 páginasEl Sistema Circulatorio Posee Como Función El Distribuir Los NutrientesTania ChambiAún no hay calificaciones

- Ensayo El OrdenadorDocumento2 páginasEnsayo El OrdenadorErika MayaAún no hay calificaciones

- Carlos Trujillo - Primera AntologíaDocumento15 páginasCarlos Trujillo - Primera AntologíaDomínguezCicchettiMartínAún no hay calificaciones

- Crianza de PollosDocumento62 páginasCrianza de PollosYamir Rios100% (1)

- Guía de Prácticas: Aprendizaje Práctico ExperimentalDocumento4 páginasGuía de Prácticas: Aprendizaje Práctico ExperimentalEdward RamirezAún no hay calificaciones

- 6-Bronquiolitis y AsmaDocumento5 páginas6-Bronquiolitis y AsmaJoel Bruno100% (1)

- Antecedentes y Definición Del Problema.Documento5 páginasAntecedentes y Definición Del Problema.Juan FranciscoAún no hay calificaciones

- Ptos.: El Costo Del Capital Promedio Ponderado, También Se Conoce Como ElDocumento3 páginasPtos.: El Costo Del Capital Promedio Ponderado, También Se Conoce Como Elreporte kilometrajesAún no hay calificaciones

- Propuestos Grupo 5Documento3 páginasPropuestos Grupo 5ruth karina aguirre mendietaAún no hay calificaciones

- Cadena de Abastecimiento de Aceite de Palma PDFDocumento145 páginasCadena de Abastecimiento de Aceite de Palma PDFKaren GarcesAún no hay calificaciones

- Clave Calific - AINADocumento3 páginasClave Calific - AINAPatricia DelgadoAún no hay calificaciones

- annotated-BASE DE DATOS PARA ANÁLISIS DE FUENTES (1) - 31 DE OCTUBREDocumento1 páginaannotated-BASE DE DATOS PARA ANÁLISIS DE FUENTES (1) - 31 DE OCTUBRELucKyAún no hay calificaciones

- Universidad Nacional Autónoma de Honduras (CU) : ClaseDocumento23 páginasUniversidad Nacional Autónoma de Honduras (CU) : ClasemdAún no hay calificaciones

- Cuándo Tomar Bcaa Y Cómo Hacerlo - Fivestars Fitness PDFDocumento1 páginaCuándo Tomar Bcaa Y Cómo Hacerlo - Fivestars Fitness PDFLuis MiguelAún no hay calificaciones

- MERCANTILDocumento1 páginaMERCANTILluzAún no hay calificaciones

- HidrocarburosDocumento10 páginasHidrocarburosGabriela Torres Marin100% (1)

- Sikalastic - 560Documento5 páginasSikalastic - 560Mario Magaña VargasAún no hay calificaciones

- Formulario Denuncio Tattersall-Reale 2017Documento1 páginaFormulario Denuncio Tattersall-Reale 2017ldea123456Aún no hay calificaciones

- Transferencia de BeneficiosDocumento1 páginaTransferencia de BeneficiosErick LópezAún no hay calificaciones