100% encontró este documento útil (2 votos)

460 vistas11 páginasCodigos Ejemplos Verilog

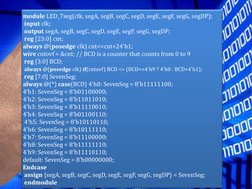

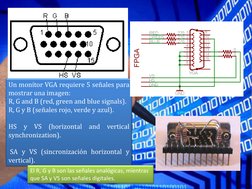

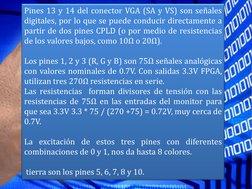

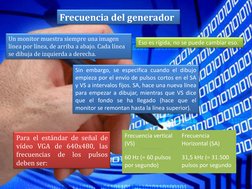

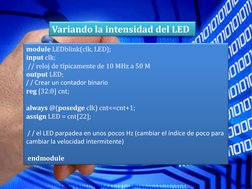

Este documento presenta varios ejemplos de código Verilog para controlar LEDs, incluyendo controlar el brillo de un LED usando PWM, hacer que un LED parpadee, mostrar números en un display de 7 segmentos usando contadores, y generar señales para un monitor VGA. También explica brevemente los conceptos de sincronización horizontal y vertical para la generación de señales de video.

Cargado por

Jorgito XdDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PDF, TXT o lee en línea desde Scribd

100% encontró este documento útil (2 votos)

460 vistas11 páginasCodigos Ejemplos Verilog

Este documento presenta varios ejemplos de código Verilog para controlar LEDs, incluyendo controlar el brillo de un LED usando PWM, hacer que un LED parpadee, mostrar números en un display de 7 segmentos usando contadores, y generar señales para un monitor VGA. También explica brevemente los conceptos de sincronización horizontal y vertical para la generación de señales de video.

Cargado por

Jorgito XdDerechos de autor

© © All Rights Reserved

Nos tomamos en serio los derechos de los contenidos. Si sospechas que se trata de tu contenido, reclámalo aquí.

Formatos disponibles

Descarga como PDF, TXT o lee en línea desde Scribd

![BRILLO DE UN LED

module LED(clk, LED1);

input clk;

output LED1;

reg [23:0] cnt;

always @(posedge clk) cnt<=cnt+1;

wire [3:0]](https://screenshots.scribd.com/Scribd/252_100_85/189/366225342/2.jpeg)

![module LED_PWM(clk, PWM_input, LED);

input clk;

input [3:0] PWM_input; / / 16 niveles de intensidad

output LED; reg [4:0] PW](https://screenshots.scribd.com/Scribd/252_100_85/189/366225342/4.jpeg)