Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Trabajo MIPS

Cargado por

Carlos Eduardo Paiva Mariátegui0 calificaciones0% encontró este documento útil (0 votos)

20 vistas5 páginasDerechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

20 vistas5 páginasTrabajo MIPS

Cargado por

Carlos Eduardo Paiva MariáteguiCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 5

SEGMENTACIN

Existen dos maneras de acelerar un circuito combinacional: Paralelismo espacial

(replicacin de hardware) y Pipelines (Caeras) . Nos concentraremos en esta

ltima.

Comenzaremos con una definicin muy general: la implementacin de un pipeline

a un circuito combinacional ocurre al segmentar o dividir dicho circuito en N etapas

de procesamiento.

Dnde los resultados procesados por una etapa son la entrada de la siguiente. Los

resultados finales debern ser los mismos que en el circuito original, pero stos se

arrojarn a una mayor velocidad.

La velocidad de procesamiento, V = cantidad de datos procesados por unidad de

tiempo (*otros nombres: Throghput, Ancho de banda, Produccin.)

En base a esto definiremos: Perodo de un circuito, P = 1 / V

I. PIPELINE.

El proceso en pipeline (o segmentado) es similar al utilizado en cualquier

cadena de montaje, y el nombre pipeline (tubera) se debe al hecho de que,

como en una tubera, en la entrada se aceptan nuevos elementos

(instrucciones) antes de que los previamente aceptados salgan por la

salida.

Empecemos con el ejemplo de una cadena de montaje. Supongamos una

gran pastelera en la que las tartas primero se hacen en el horno y despus

se empaquetan para la venta. El proceso de empaquetar una tarta consiste

en:

1. Poner una caja vaca en la mesa.

2. Meter una tarta en la caja.

3. Cerrar y precintar la caja.

4. Poner una etiqueta en la caja.

5. Llevar la caja a un gran contenedor.

Si cada una de estas operaciones la realiza un operario en 10 segundos,

parece claro que se tarda 50 s en empaquetar una tarta y, por lo tanto, en

empaquetar 10 tartas se tardara 500 s.

Ahora supongamos que se dispone de una cadena de empaquetado de

tartas con una cinta transportadora sobre la que trabajan cinco operarios

especializados en tareas distintas. El primer operario pone la caja-1 en la

cinta transportadora, y sta avanza hasta que la caja-1 est donde el

segundo operario, que introduce una tarta dentro de la caja-1, al mismo

tiempo que el primer operario pone otra caja-2 en la cinta. La caja-1 sigue

avanzando hasta el tercer operario, que la cierra y la precinta, al mismo

tiempo que el segundo operario mete otra tarta en la caja-2 y el primer

operario pone otra caja-3 en la cinta. La caja-1 sigue su camino en la cinta

pasando por el cuarto operario, que pone una etiqueta, hasta llegar al

quinto operario, que la retira de la cinta.

En el momento que el quinto operario retira la caja de la cinta, hay cuatro

cajas ms en la cinta. Si cada una de estas fases de empaquetado se

realiza en 10 s, a partir de ahora, cada 10 s saldr una nueva tarta

empaquetada, en lugar de hacerlo cada 50 s que se tardaba cuando no

haba cadena de empaquetado. A partir de ahora, en tener 10 tartas

empaquetadas se tardar solamente 100 segundos, mientras que en el

caso de cuando se tena un solo operario se tardaba 500 segundos.

Debe quedar claro que aunque ahora sale una nueva tarta

empaquetada cada 10 s, la preparacin completa de cada tarta sigue

requiriendo 50 s (igual que cuando haba una sola persona preparando las

tartas).

Ha aumentado el rendimiento, pero se mantiene el tiempo de empaquetado

de cada tarta.

A. COPCEPTOS BASICOS.

La ejecucin de una instruccin podra descomponerse en las siguientes 5 etapas:

1. F: Alimentacin de la instruccin (fetch)

2. D: Decodificacin de la instruccin / Lectura de registros

3. E: Ejecucin (en la ALU) / Clculo de la direccin efectiva

4. M: Acceso a memoria

5. W: Escritura del resultado en registros de la CPU

Con la tcnica de la segmentacin (o pipelining) se consigue que a cada ciclo de

reloj finalice una instruccin, o lo que es lo mismo, una velocidad de instruccin

por ciclo.

Debemos tener en cuenta que:

1. Cada etapa dispone de los recursos hardware necesarios para realizar

su cometido.

2. Las ejecuciones de las instrucciones se solapan.

3. Todas las etapas tienen la misma duracin (ciclo de reloj).

4. La duracin del ciclo de reloj lo fija la etapa ms lenta.

II. RIESGOS DE SEGMENTACIN.

A. Riesgos Estructurales

Conflictos en el uso de los recursos del cauce segmentado por parte de las

multiples instrucciones cuya ejecucin se solapa (recursos

insuficientemente replicados o UF no segmentadas).

Causas:

Recursos insuficientes: los recursos no se han replicado lo

suficiente como para permitir la ejecucin solapada de todas las

combinaciones de instrucciones sin dar lugar a prdida de ciclos

Unidades Funcionales no segmentadas: no es posible iniciar una

secuencia de instrucciones en la que varias consecutivas utilicen

esa unidad funcional sin esperas y por tanto prdida de ciclos

B. Riesgos por Dependencias de Datos

Problemas derivados de dependencias entre instrucciones cuya ejecucin

se solapa.

Las Lecturas/Escrituras sobre una misma variable (registro) deben

efectuarse en el orden que especifica el programa secuencial

Problema de la Dependencia de Datos

Dominio de una Instruccin (D[I]):

Conjunto de variables (registros) sobre las que la instruccin

realiza lecturas.

Rango de una Instruccin (R[I]):

Conjunto de variables (registros) sobre las que la instruccin

realiza escrituras.

C. Riesgos de Control

Problemas derivados de las instrucciones de control de flujo, debido al

desconocimiento temporal de la siguiente instruccin a ejecutar.

Soluciones de los riesgos.

También podría gustarte

- Técnicas de EncriptamientoDocumento3 páginasTécnicas de EncriptamientoMark Griffiths EchalarAún no hay calificaciones

- El Proceso Unificado de Desarrollo de Software - Jacobson - Booch - RumbaughDocumento458 páginasEl Proceso Unificado de Desarrollo de Software - Jacobson - Booch - RumbaughEfrain Cortez86% (43)

- Guide 12thedition Castellano WEBDocumento269 páginasGuide 12thedition Castellano WEBRoberto CRAún no hay calificaciones

- Metrica de Estimación COCOMODocumento15 páginasMetrica de Estimación COCOMOCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Trabajo MIPSDocumento5 páginasTrabajo MIPSCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Arquitectura SPARC - Micro2Documento6 páginasArquitectura SPARC - Micro2Carlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Diseño Al Nivel de ComponentesDocumento4 páginasDiseño Al Nivel de ComponentesCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Ejercicios Pruebas No ParametricasDocumento5 páginasEjercicios Pruebas No ParametricasMarco Antonio Damian Laura100% (1)

- 11 Cauca-PatiaDocumento6 páginas11 Cauca-PatiaCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Optimizacion - Newton - Raphson PDFDocumento12 páginasOptimizacion - Newton - Raphson PDFCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Perfil de Proyecto de InvestigaciónDocumento19 páginasPerfil de Proyecto de InvestigaciónCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Clase 2. - Visual Basic El LenguajeDocumento58 páginasClase 2. - Visual Basic El LenguajeCarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Nuevo Reglamento de Tesis Unp 10 de Agosto 2012 PDFDocumento40 páginasNuevo Reglamento de Tesis Unp 10 de Agosto 2012 PDFJunnior Espinoza JuarezAún no hay calificaciones

- Proyecto BibliotecaDocumento127 páginasProyecto BibliotecaMayra Perez SalazarAún no hay calificaciones

- Proyecto de Biblioteca Virtual - FF - HH Univ. Santa Cruz - BoliviaDocumento12 páginasProyecto de Biblioteca Virtual - FF - HH Univ. Santa Cruz - BoliviaEdgar GamboaAún no hay calificaciones

- Trabajo Diseño de Sistemas - PEEDocumento3 páginasTrabajo Diseño de Sistemas - PEECarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Trabajo Diseño de Sistemas - PEEDocumento3 páginasTrabajo Diseño de Sistemas - PEECarlos Eduardo Paiva MariáteguiAún no hay calificaciones

- Casos de Estudio de Cpu RealesDocumento40 páginasCasos de Estudio de Cpu RealesMiguel AlejandroAún no hay calificaciones

- Arquit-Compu - S5Documento25 páginasArquit-Compu - S5Luis AprAún no hay calificaciones

- ComputadoresDocumento72 páginasComputadoresAyanny Bastidas RodriguezAún no hay calificaciones

- Modulo Expancion PLCDocumento12 páginasModulo Expancion PLCJosé Martín Martínez V.100% (1)

- Act 12Documento5 páginasAct 12Paola AmadoAún no hay calificaciones

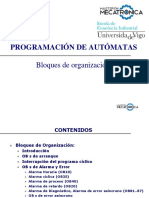

- MM Paa - Bloques OrganizacionDocumento13 páginasMM Paa - Bloques OrganizacionRubén Pérez GarcíaAún no hay calificaciones

- Tercera Generacion de La Computadora EnsayoDocumento6 páginasTercera Generacion de La Computadora EnsayoKevin Geovanny Martinez BanegasAún no hay calificaciones

- Apuntes de Mantenimiento de Equipo de Cómputo PDFDocumento226 páginasApuntes de Mantenimiento de Equipo de Cómputo PDFBerenice RojasAún no hay calificaciones

- 1 Principios de Arquitectura ComputacionalDocumento2 páginas1 Principios de Arquitectura ComputacionaleduardogzzAún no hay calificaciones

- 01 Control System Fault Tracing Manual SpanishDocumento33 páginas01 Control System Fault Tracing Manual SpanishAlberto LeyvaAún no hay calificaciones

- 01 Manual Introducción A La TecnologíaDocumento146 páginas01 Manual Introducción A La TecnologíaQueTeDenPolCulooAún no hay calificaciones

- Linux Unidad4Documento41 páginasLinux Unidad4Yurii VelazquezAún no hay calificaciones

- Conjunto de InstruccionesDocumento8 páginasConjunto de InstruccionesERamosAún no hay calificaciones

- Generalidades de PC SDocumento9 páginasGeneralidades de PC SElvis WilliamsAún no hay calificaciones

- Semana 01 - Mantenimiento de Equipo de ComputoDocumento30 páginasSemana 01 - Mantenimiento de Equipo de ComputoEdgardo SatoAún no hay calificaciones

- Haward y SofwardDocumento19 páginasHaward y SofwardLazaro Paez RuizAún no hay calificaciones

- UF0319Documento45 páginasUF0319Mercedes GuancheAún no hay calificaciones

- Sistemas Operativos Por La Forma de Ofrecer Sus ServiciosDocumento20 páginasSistemas Operativos Por La Forma de Ofrecer Sus Serviciosgermania sanchez villaAún no hay calificaciones

- Micro Pic 18F45K50Documento13 páginasMicro Pic 18F45K50Anthony Chavez GarroAún no hay calificaciones

- Foro 2 Participación Arquitectura ComputadoresDocumento4 páginasForo 2 Participación Arquitectura ComputadoresLuchoAún no hay calificaciones

- Cuerpo Del TrabajoDocumento17 páginasCuerpo Del TrabajoEmil SanchezAún no hay calificaciones

- Ofimatica BasicaDocumento70 páginasOfimatica BasicaJuan Rivera100% (1)

- Cuestionario Del Documental Maravillas ModernasDocumento6 páginasCuestionario Del Documental Maravillas ModernasJiménez Garcia GerardoAún no hay calificaciones

- Estructura de ArchivoDocumento49 páginasEstructura de ArchivoCOKE20082008100% (5)

- GB-AEBN Espanol 1001 PDFDocumento32 páginasGB-AEBN Espanol 1001 PDFJean GarciaAún no hay calificaciones

- Tema de Investigación:: Pic (Microcontrolador)Documento15 páginasTema de Investigación:: Pic (Microcontrolador)CRISTHIAN ALEXANDER DEL CASTILLO MURILLOAún no hay calificaciones

- Glosario TICSDocumento175 páginasGlosario TICSMarlon ChenAún no hay calificaciones

- Saber Electronica 123Documento64 páginasSaber Electronica 123Sebastian Lewitan100% (1)

- Semana 6 - TecnologiaDocumento2 páginasSemana 6 - TecnologiaFREDY LEMUS100% (1)

- Gestión de Memoria RAMDocumento11 páginasGestión de Memoria RAMJavier VillanuevaAún no hay calificaciones