Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Guía 1 SDI 115 2013

Cargado por

Beatriz SerranoDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Guía 1 SDI 115 2013

Cargado por

Beatriz SerranoCopyright:

Formatos disponibles

Universidad de El Salvador Sistemas Digitales I

Universidad de El Salvador Facultad de Ingeniera y Arquitectura Gua 1: Introduccin a los Lenguajes HDL

Eddys Elas Lacayo Lpez elacayo77@hotmail.com Juan Ramn Albiana Alfaro aa09120gnu@ yahoo.es

RESUMEN: Esta gua pretende ser una introduccin a los lenguajes HDL (Hardware Description Language), especficamente para trabajar con AHDL (Altera Hardware Description Language) de Altera y VHDL (Very high speed integrated circuit Hardware Description Language) del estndar IEEE (Institute of Electrical and Electronics Engineers) std 1076-1987, se explicar con mayor detalle VHDL, para minimizar el contenido de la gua, pero el estudiante puede trabajar en el lenguaje que prefiera, adems usar el sistema operativo de su preferencia, para Windows existen muchos IDEs (Integrated Development Environment o Ambiente de Trabajo Integrado) y compiladores como lo son Max Plus de Altera (este es el que se utilizar en la gua), Active HDL y muchos otros, estos software son pagados y por tanto se recomienda trabajar con software libre para lo cual se tiene GHDL para LINUX, y para visualizar resultados GTKWave. INTRODUCCIN: Los lenguajes HDL son muy variados estn desde los Netlist como Ada (lenguaje de programacin nombrado en honor a Ada Lovelace, conocida popularmente como la

primera programadora computacional) (en este fue basado VHDL) hasta lenguajes tan potentes en los que muchas veces el circuito ya no se ve claramente y ms bien es un lenguaje de programacin, esto tiene sus grandes ventajas aunque tambin existen desventajas, la ms notable desventaja es que a la hora de implementar el circuito no es fcil pasar del programa de descripcin al Hardware que lo implementa, este proceso es conocido como sntesis. VENTAJAS DEL USO DE VHDL: VHDL permite disear, modelar, y comprobar un sistema desde un alto nivel de abstraccin bajando hasta el nivel de definicin estructural de puertas. Circuitos descritos utilizando VHDL, siguiendo unas guas para sntesis, pueden ser utilizados por herramientas de sntesis para crear implementaciones de diseos a nivel de puertas. Al estar basado en un estndar (IEEE Std 10761987) los ingenieros de toda la industria de diseo pueden usar este lenguaje para minimizar errores de comunicacin y problemas de compatibilidad.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

Modularidad: VHDL permite dividir o descomponer un diseo hardware y su descripcin VHDL en unidades ms pequeas.

Instalacin de las herramientas de programacin y Simulacin VHDL: Para Windows: Descargar un IDE, uno muy bueno se encuentra en www.altera.com, instalarlo al igual que se instalan todos los programas en Windows. Para Linux: Descargar dos archivos GHDL y GTKWave, hay diferentes versiones para cada sistema operativo, se utilizar Ubuntu, una forma muy sencilla de instalarlos es desde el synaptic pero en esta ocasin se har con los comandos aptget o dpkg, abra una consola y escriba: apt-get install ghdl Si en cambio, los instaladores se encuentran en una carpeta, se debe utilizar el comando dpkg i *.deb Que instalar todos los archivos que estn en la carpeta actual. Para escribir el cdigo se puede utilizar cualquier editor de texto plano como Vi, Vim, Geany, Gedit, etc. Creacin del primer programa: En Windows: Se utilizar el software de Altera. 1.0. Cree nuevo proyecto file -> Name como se muestra en la imagen 1 (flecha 1), se le dar el nombre de comp_and como se muestra en la imagen 2. 2.0. Luego seleccione la opcin nuevo archivo como lo indica la flecha 2 en la imagen 1.

Imagen 1

Imagen 2 3.0. Aparecer una nueva ventana, seleccione Text Editor File como se muestra en la imagen

Imagen 3. 4.0. Luego aparecer una ventana donde podr editar texto, gurdela con el mismo nombre del proyecto, en este caso comp_and.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

5.0. Escriba el siguiente cdigo en el editor y gurdelo.

Imagen 5.

6.0.

Luego compile el cdigo, la opcin Max + Plus II -> compiler se muestra en la imagen 4, aparecer una ventana, vaya a la opcin Processing ->Funtional SNF Stractor, esto se muestra en la imagen 5 y por ltimo en la ventana que apareci presione Start y luego ok.

Imagen 6. 7.0. Para ver si funciona correctamente se har una simulacin, para esto vaya al men Max + Plus II -> Wave Form Editor, como se muestra en la imagen 7, aparecer otra imagen solo pulse ok.

Imagen 4.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

Imagen 7 8.0. Guarde el editor de forma de onda con el nombre de comp_and.scf. Luego vaya al men Node -> Enter Nodes from SNF, como se muestra en la imagen 8.

9.0.

Imagen 9. 11.0. Luego se hacen los ajustes de el archivo de simulacin File -> End Time.., coloque 2.0 us como se muestra en la imagen 10, luego en el men Options -> Grid size, dele un valor de 100 ns como se muestra en la imagen 11, por ltimo seleccione el men view -> Fit in windows, con eso ya est configurada la ventana.

Imagen 10.

Imagen 11. Imagen 8. 10.0. Agregue las seales como se muestra en la imagen 9, presionando List y la flecha que indica hacia la derecha. 12.0. Con los Botones del lado izquierdo se modifican las seales de entrada (solo se pueden modificar las entradas) de forma que queden como se muestra en la imagen 12.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

Explicacin del cdigo.

Imagen 12. 13.0. Luego vaya al men Max Plus II -> Simulator, en la ventana que aparece presione start, luego ok, el resultado y todo lo anterior se muestra en la imagen 12. Como se puede observar la salida obedece el comportamiento de una compuerta and, esto se muestra con mayor detalle en la imagen 13. Lneas 1, 7, 12: El compilador ignora todo lo que sigue despus de dos guiones -- se le conoce como comentario, es muy buena prctica comentar los cdigo, para que otros lo puedan entender. Lneas 2 y 6: En primer lugar, sea el tipo de descripcin que sea, hay que definir el smbolo o entidad del circuito. En efecto, lo primero es definir las entradas y salidas del circuito, es decir, la caja negra que lo define. Se le llama entidad se declara con la palabra clave ENTITY nombre_asignado se finaliza este bloque con la palabra clave END nombre_asignado. Lnea 3: En esta se define el puerto PORT() que son las entradas y salidas que tendr, en este caso dos entradas a y b, y una salida y. Lneas 4 y 5: El lenguaje VHDL tiene varios tipos de variables un tipo es BIT, estas lneas declaran a las variables a y b como entradas tipo BIT IN/OUT BIT y y como salida del mismo tipo. Lneas 8 y 11: Se declara la arquitectura designndole un nombre como sigue, ARCHITECTURE nombre_arch luego le sigue la palabra clave OF

Imagen 13.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

nombre_asignado (nombre_asignado es el nombre que se le dio a la entidad), esto quiere decir que la arquitectura pertenece a la entidad dada. Se finaliza la arquitectura con la palabra clave END nombre_arch Lnea 9: Despus de la lnea 9 BEGIN y antes de la 11 END se declaran las operaciones a realizar, estas operaciones se ejecutan de manera concurrente, esto quiere decir que no importa el orden en que se coloquen las instrucciones, en este caso solo hay una y <= a AND b, la entrada a y b se operan con la instruccin AND, el resultado se le asigna a la salida y, con el operador <=. Tambin se puede ingresar en esta lnea procesos secuenciales, sea operaciones que se ejecutan una despus de la otra con la palabra clave PROCESS. Nota: las palabras clave se han escrito con maysculas para diferenciarlas, pero esto no es una regla. En Linux: Una vez instalados los dos programas mencionados anteriormente, la creacin de programas VHDL se resume a trabajar en el editor de texto de su preferencia. Para ejemplificar esto a continuacin se muestra el mismo programa creado para Windows con el cual se ejemplificar el mtodo para comprobar, compilar, ejecutar y simular los resultados utilizando un editor de texto y principalmente la consola de Linux, as como tambin el GTKWave para ver resultados. Se comenzar escribiendo el cdigo:

ENTITY comp_and IS PORT( a,b :IN BIT; y :OUT BIT); END comp_and; ARCHITECTURE arch_and OF comp_and IS BEGIN y <= a AND b; END arch_and;

Luego se guarda con el nombre de comp_and.vhd. El cdigo es exactamente igual al que se utiliz en Windows por lo tanto la explicacin es la misma expuesta en la seccin anterior. A continuacin se escribir el testbench, el cual es un archivo en el cual funciona como generador de estmulos, es decir, en el se definirn las seales de entrada necesarias para conseguir la tabla de verdad del circuito y saber si ste funciona correctamente. El cdigo es el siguiente:

ENTITY tb_comp_and IS END tb_comp_and; ARCHITECTURE arch_and OF tb_comp_and IS COMPONENT comp_and IS PORT( a,b :IN BIT; y :OUT BIT); END COMPONENT comp_and; SIGNAL ent1:bit:='0'; SIGNAL ent2:bit:='0'; SIGNAL sal:bit; BEGIN ckt1:comp_and PORT MAP ( a => ent1, b => ent2, y => sal ); PROCESS BEGIN WAIT FOR 20 ns; ent1 <= '1'; WAIT FOR 20 ns; ent1 <= '0'; ent2 <= '1'; WAIT FOR 20 ns;

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

ent1 <= '1'; WAIT FOR 20 ns; ent1 <= '0'; ent2 <= '0'; END PROCESS; END ARCHITECTURE arch_and;

Este cdigo ser guardado con el nombre de tb_comp_and.vhd. Explicacin del cdigo testbench. Como se explic en el cdigo anterior la palabra clave ENTITY define la caja negra que contiene el circuito. ARCHITECTURE define las acciones que realizar el testbench. COMPONENT relaciona el testbench con las variables y las acciones del circuito en s, el cual ha sido guardado con el nombre de arch_and y como se puede observar dentro de COMPONENT se definen nuevamente las entradas y salidas del circuito utilizando la funcin PORT. SIGNAL se utiliza para definir las seales que se utilizarn para estimular el circuito, tambin se les da valores iniciales a las seales de entrada, como se puede observar, en este caso se le da valor inicial de 0 lgico a las seales de entrada. BEGIN es una palabra clave que se utiliza dentro del bloque ARCHITECTURE para indicar el inicio de la descripcin de la arquitectura. ckt1:comp_and define la iniciacin del componente que relaciona el testbench con el circuito creado. PORT MAP define en bloque que une las seales que se utilizarn durante la simulacin a las variables de entrada y salida del circuito.

PROCESS contiene el bloque de sealizacin, en este bloque como se puede ver se utilizan las palabras clave WAIT FOR de modo que los cambios de 0 a 1 lgico en las seales de entrada nombradas ent1 y ent2 son controlados definiendo el tiempo que debe esperar cada variable antes de hacer el siguiente cambio. Finalmente END PROCESS y END ARCHITECTURE definen el final de los bloques de proceso y arquitectura. Siguiendo la estructura bsica del ejemplo anterior es posible definir y simular circuitos con muchas entradas y salidas y con diferentes niveles de complejidad. Luego de haber guardado ambos archivos en una carpeta se puede proceder a su compilacin y ejecucin en la consola, este proceso se muestra paso a paso en la figura 14:

En la primera lnea por medio del comando ls se puede ver que en la carpeta solo estn los dos archivos creados, se procede a utilizar el siguiente comando para realizar un anlisis en ambos los cdigos:

ghdl a comp_and.hdl tb_comp_and.hdl

Si hay algn error, este ser mostrado luego de la ejecucin de los comandos anteriores. Ahora se

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

utilizar el comando ls y se ver hay 3 archivos ms. Luego se crear el ejecutable con el siguiente comando:

ghdl e tb_comp_and

ejecucin del programa. Para ver e interpretar estos resultados se utilizar el gtkwave por medio del siguiente comando:

gtkwave tb_comp_and.vcd

Es importante notar que para crear el ejecutable se utiliza solo el nombre de tb_comp_and sin su extensin. Si utiliza una vez ms el comando ls ver que se ha creado el archivo tb_div (letras color verde). Para ejecutarlo se utilizar la siguiente lnea de comando:

./tb_comp_and --vcd=tb_comp_and.vcd -stoptime=100ns

Y como resultado el gtkwave se abrir, se debern seleccionar las entradas y salidas que se desean ver y, es importante mencionar que para ver correctamente los resultados es necesario utilizar los botones de zoom in o zoom out. Se puede apreciar el resultado en la figura 15:

Como se puede observar al ejecutar el programa se definen como parmetros el nombre del archivo en el cual se guardarn los resultados de la ejecucin del programa:

--vcd=tb_comp_and.vcd

As como tambin el tiempo de ejecucin, en este caso es de 100ns:

-stop-time=100ns

Ntese la importancia de que el tiempo de ejecucin sea suficiente para que todas las combinaciones definidas en las seales de entrada se ejecuten, si se duplica el tiempo de ejecucin, las indicaciones se repetirn una vez ms de modo que si se ampla el tiempo de ejecucin de forma considerada o se disminuye el tiempo que debe durar cada cambio de variable se pueden obtener seales peridicas. Si se utiliza el comando ls se ver que un archivo nuevo ha sido creado como resultado de la

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I ASIGNACIN

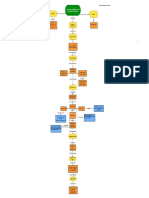

1. Realizar el cdigo VHDL para las compuertas: AND, NAND, OR, NOR, EXOR, EXNOR y NOT, simular en TINA y VHDL. 1.1 Explicar paso a paso como es el proceso de instalacin de VHDL y TINA. 1.2 Realizar el cdigo VHDL para el ejemplo 2.35 del libro. 1.2 Realizar el cdigo VHDL para el problema 2.35 del final del captulo. 1.3 Circuito 3: Un automvil a prueba de choques. Descripcin: Se trata de un automvil con tres sensores, uno al frente y dos a los costados, al arrancar se dirige hacia adelante, al encontrar un obstculo gira, a uno de los costados, esquivando el obstculo. La posicin de los sensores se muestra en la siguiente figura. Para girar a los lados, se hace que las llantas giren en distintas direcciones, por ejemplo para girar a la izquierda, las llantas X rotaran hacia atrs mientras las llantas Y hacia adelante, para hacer que el par de llantas X giren hacia adelante se deber poner en una variable de control llamada X el bit 0, para que giren hacia atrs X=1, igual para el par de llantas Y, con su respectiva variable de control Y, la lgica de control de las llantas es la siguiente. X 0 0 1 1 Y 0 1 0 1 Descripcin Hacia adelante Hacia la derecha Hacia la izquierda Hacia atrs

Si los tres sensores A, B y C estn en 1, es decir, detecta obstculo en las tres direcciones, empezara a retroceder, de lo contrario girara en la direccin que est libre de obstculos, si existe la posibilidad de girar hacia la derecha o hacia la izquierda se girar a la derecha. 1.3.1 Encontrar la tabla de verdad que representa la lgica de control. 1.3.2. Implementar el circuito con cdigo VHDL. 1.3.3. Obtener graficas de simulacin, en las que se muestren las entradas (A, B y C) y las salidas (X y Y), con todas las posibilidades de entrada.

2.

Preguntas de Investigacin.

2.1 Uso y sintaxis de las instrucciones IF THEN. 2.2 Uso y sintaxis de la instrucciones CASE WHEN.

Introduccin a Lenguajes HDL

Universidad de El Salvador Sistemas Digitales I

2.3 Uso de las instrucciones anteriores para implementar el cdigo VHDL directamente desde las tablas de verdad. 2.4 Tipos de datos de entrada y salida que soporta VHDL. 2.5 Cmo se crean arreglos en VHDL? 2.6 Cmo declarar un componente en VHDL? Mostrar un ejemplo. 2.7 Cules son los operadores en VHDL? 2.8 Explique con sus palabras la funcin del circuito 1 y 2, en qu aplicacin se imagina usted que podra utilizarlos? Imgenes de los resultados. NOTA: El contenido del CD deber ir ordenado, con carpetas individuales para cada tem mencionado ejemplo: IMGENES, CIRCUITO1, etc. Fecha de entrega: Viernes 05 de abril de 2013, primer viernes despus de Semana Santa. Hora mxima 10:00 am, despus de las 10 se calificara en base 9, despus del viernes la base de calificacin bajara 2 puntos por da de atraso.

3. Acerca de la tarea:

3.1 Un reporte impreso 3.1.1 Contenido del reporte Portada Objetivos Introduccin Marco terico Obtencin del software de simulacin VHDL Direccin de descarga Pasos para la instalacin Desarrollo de los circuitos Descripcin de los pasos seguidos para la solucin Cdigo VHDL Grficos obtenidos para cada circuito Observaciones Conclusiones Respuesta a las preguntas e investigacin. Bibliografa 3.2 Un CD 3.2.1 Contenido del CD. Software utilizado Reporte en formato PDF y WORD Cdigos utilizados (*.vhd) y todos los que genera el proceso de compilacin y ejecucin.

Bibliografa:

VHDL Lenguaje para descripcin y modelado de circuitos, Fernando Pardo Carpio, Universidad de Valencia 1997. DIGLENSY SAC Primera Empresa del Per Dedicada al Desarrollo Electrnico, tutorial VHDL, http://www.diglensy.com/ Simulando VHDL con herramientas GNU: GHDL+GTKWAVE, Roberto Aragn. http://www.iearobotics.com/personal/juan/p ublicaciones/art6/html/ghdl.html

Cualquier consulta puede tambin utilizar los correos en el ttulo de la prctica.

Introduccin a Lenguajes HDL

También podría gustarte

- Tarea 1 SDI 115 2015Documento11 páginasTarea 1 SDI 115 2015Javiier UmañaAún no hay calificaciones

- Guía 1 SDI-SDU-115-2014Documento10 páginasGuía 1 SDI-SDU-115-2014Patho CortzAún no hay calificaciones

- Practica 101 Compuertas Logicas BasicasDocumento4 páginasPractica 101 Compuertas Logicas BasicasPaola VazquezAún no hay calificaciones

- Actividad6 Pérez Padrón Edgar AbrahamDocumento18 páginasActividad6 Pérez Padrón Edgar AbrahamEdgar Perez Padron100% (1)

- Assembler Visual C++Documento12 páginasAssembler Visual C++Francisco Martin VazquezAún no hay calificaciones

- VHDL ProyectosDocumento92 páginasVHDL ProyectosLander Arturo Rubio JuarezAún no hay calificaciones

- Programación de Circuitos Lógicos en VHDLDocumento26 páginasProgramación de Circuitos Lógicos en VHDLCheynAún no hay calificaciones

- Convertidor de códigos 8421 a 7 segmentosDocumento9 páginasConvertidor de códigos 8421 a 7 segmentosFredy Balmore BonillaAún no hay calificaciones

- Practica 1 Compuertas Multiplexor VHDLDocumento10 páginasPractica 1 Compuertas Multiplexor VHDLshujidanAún no hay calificaciones

- 1 Pract IntroDocumento26 páginas1 Pract IntroNorman CubillaAún no hay calificaciones

- Programación de Microcontroladores en CDocumento58 páginasProgramación de Microcontroladores en CDaniel Andres Segura TamayoAún no hay calificaciones

- Introduccion A Lenguaje de Programacion C#Documento7 páginasIntroduccion A Lenguaje de Programacion C#Carlos Sabe100% (1)

- Introducción Al TASMDocumento4 páginasIntroducción Al TASMedgarnoelr100% (1)

- PROGRAMACIÓN I EN C++ BorlandDocumento54 páginasPROGRAMACIÓN I EN C++ BorlandCristian F FingerAún no hay calificaciones

- Manual Teclado PantallaDocumento10 páginasManual Teclado PantallaLuis AlbertoAún no hay calificaciones

- Programación I en C++Documento70 páginasProgramación I en C++Anibal pradoAún no hay calificaciones

- Practica Con VHDLDocumento9 páginasPractica Con VHDLAle KeyAún no hay calificaciones

- 1 Intro C SharpDocumento17 páginas1 Intro C SharpAlberto RodríguezAún no hay calificaciones

- Manual de Uso de DEV-C++Documento10 páginasManual de Uso de DEV-C++Matiasignacio Urquieta ReyesAún no hay calificaciones

- Ensamblador ClaseDocumento55 páginasEnsamblador ClaseAnonymous PAbgQYbAún no hay calificaciones

- Winedt MinitutorialDocumento4 páginasWinedt Minitutorialescobedo12345Aún no hay calificaciones

- Programación de microcontroladoresDocumento45 páginasProgramación de microcontroladoresCarla SanchezAún no hay calificaciones

- DevC++ Manual Con Interpretacion de ErroresDocumento17 páginasDevC++ Manual Con Interpretacion de ErroresFelipe Aun100% (1)

- Quartus Compuerta XnorDocumento24 páginasQuartus Compuerta XnorDavid Gamboa GuzmánAún no hay calificaciones

- Tutorial FPGA EspanolDocumento12 páginasTutorial FPGA EspanolJose Ignacio Gonzalez BeltramoAún no hay calificaciones

- Como Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Documento26 páginasComo Programar y Cargar Un Programa en Una Nexys 2 (FPGA)Josue BustamanteAún no hay calificaciones

- Manual de Ayuda para El Dibujo Simulacion y Diseno de Una PCB Con Orcad 9Documento27 páginasManual de Ayuda para El Dibujo Simulacion y Diseno de Una PCB Con Orcad 9Maria MarAún no hay calificaciones

- Contador BCD a 7 segmentos en XilinxDocumento18 páginasContador BCD a 7 segmentos en XilinxJosset Aldridge AguilaAún no hay calificaciones

- Características Del Lenguaje de ProgramaciónDocumento10 páginasCaracterísticas Del Lenguaje de ProgramaciónSandra MadaiiAún no hay calificaciones

- Introducción a CDocumento5 páginasIntroducción a CJancarlos Prado MayorgaAún no hay calificaciones

- 030 - Introduccion A C# V11Documento40 páginas030 - Introduccion A C# V11Mauro CortesAún no hay calificaciones

- Introduccion Programacion de Psoc (Cap1)Documento15 páginasIntroduccion Programacion de Psoc (Cap1)Diego Leyton100% (2)

- Indice Curso de Programacion Pic en C Con CcsDocumento112 páginasIndice Curso de Programacion Pic en C Con CcsCHUCIAún no hay calificaciones

- NET - Guia 2Documento6 páginasNET - Guia 2Andy BrehmeAún no hay calificaciones

- Atmega AvrDocumento20 páginasAtmega AvrDeyber J. Rojas RodasAún no hay calificaciones

- Diseño DigitalDocumento16 páginasDiseño DigitalOmar PMAún no hay calificaciones

- Estructura de Un Programa en CDocumento11 páginasEstructura de Un Programa en CnahumlaneganAún no hay calificaciones

- Tutorial CodeWarrior v10 MicrocontroladoresDocumento15 páginasTutorial CodeWarrior v10 MicrocontroladoresCarlos OcampoAún no hay calificaciones

- MSDOS comandos y batchDocumento68 páginasMSDOS comandos y batchKelmer Ashley Comas CardonaAún no hay calificaciones

- Creación y uso de archivos batch en WindowsDocumento13 páginasCreación y uso de archivos batch en WindowscahecazAún no hay calificaciones

- GUIA1Documento24 páginasGUIA1Christian SánchezAún no hay calificaciones

- Curso C#Documento87 páginasCurso C#Iván CampuzanoAún no hay calificaciones

- Guia XilinxDocumento20 páginasGuia XilinxEdgar ArredondoAún no hay calificaciones

- Sistemas EmbebidosDocumento11 páginasSistemas EmbebidoscarmoralitoAún no hay calificaciones

- Microprocesadores - Guia de Laboratorio 04Documento9 páginasMicroprocesadores - Guia de Laboratorio 04David YHAún no hay calificaciones

- FPGA Cyclone II guíaDocumento28 páginasFPGA Cyclone II guíaPedro LandaetaAún no hay calificaciones

- Taller de Cracking Desde Cero Por Karmany y ShaddyDocumento22 páginasTaller de Cracking Desde Cero Por Karmany y ShaddyAristides RengelAún no hay calificaciones

- Qué Es CDocumento13 páginasQué Es CmiguelAún no hay calificaciones

- Practica - 1 en Dev C para Puerto Paralelo (Directo Al HW Desde Windows)Documento11 páginasPractica - 1 en Dev C para Puerto Paralelo (Directo Al HW Desde Windows)Hector BazarteAún no hay calificaciones

- Fundamentos de C#Documento90 páginasFundamentos de C#Construccion3s ContratasAún no hay calificaciones

- Uso Decode Warrior para Desarrollo en AssemblyDocumento12 páginasUso Decode Warrior para Desarrollo en AssemblyCesar VillamizarAún no hay calificaciones

- LDMicroDocumento25 páginasLDMicroLeandro SienraAún no hay calificaciones

- Trucos Útiles Al Crear Nuestros Archivos BatchDocumento6 páginasTrucos Útiles Al Crear Nuestros Archivos BatchmanumelenasAún no hay calificaciones

- Analizador Lexico - ProyectoDocumento11 páginasAnalizador Lexico - ProyectoXtian Castro Del CarpioAún no hay calificaciones

- Guia1 MCPDocumento7 páginasGuia1 MCPFreddy JironAún no hay calificaciones

- ISE XilinxDocumento4 páginasISE XilinxWilliam Chávez0% (1)

- Practica 1Documento18 páginasPractica 1Javier IzquierdoAún no hay calificaciones

- Programacion ScriptsDocumento28 páginasProgramacion ScriptsXeXu MarleyAún no hay calificaciones

- DLT115 Examen3 2015 SoluciónDocumento5 páginasDLT115 Examen3 2015 SoluciónEstevis MongeAún no hay calificaciones

- Evaluación de diseño de líneas de transmisiónDocumento5 páginasEvaluación de diseño de líneas de transmisiónEstevis MongeAún no hay calificaciones

- DLT115 Examen3 2017 SoluciónDocumento3 páginasDLT115 Examen3 2017 SoluciónEstevis MongeAún no hay calificaciones

- Control de Giro de Un Motor TrifasicoDocumento10 páginasControl de Giro de Un Motor TrifasicoEstevis MongeAún no hay calificaciones

- Codigo de Colores ResistenciasDocumento1 páginaCodigo de Colores ResistenciasEstevis MongeAún no hay calificaciones

- Revista Temas 74Documento136 páginasRevista Temas 74Cristian Alejandro Venegas AhumadaAún no hay calificaciones

- Diseño de curso virtual de Química 11Documento116 páginasDiseño de curso virtual de Química 11Miguel FloresAún no hay calificaciones

- Evidencia 1.2 Mapa MentalDocumento5 páginasEvidencia 1.2 Mapa MentalDanyel ZavalaAún no hay calificaciones

- Sesion de Aprendizaje de Ciencia y Tecnologia Viernes 31 de MarzoDocumento10 páginasSesion de Aprendizaje de Ciencia y Tecnologia Viernes 31 de MarzoGabriela Alemán Monzon100% (1)

- Desarrollo y Uso Didáctico de GeogebraDocumento478 páginasDesarrollo y Uso Didáctico de GeogebraMarlon Gama Quintero100% (13)

- Planeando El ProyectoDocumento78 páginasPlaneando El Proyectosergio pinchaoAún no hay calificaciones

- Prueba 1-1Documento6 páginasPrueba 1-1StiveenAún no hay calificaciones

- Microondas Cálculos RaleighDocumento4 páginasMicroondas Cálculos RaleighMetalKaiser PolancoAún no hay calificaciones

- Actividad 2 - Nadia Zuleta, Deisreth Ramos y Milagros VillarrealDocumento15 páginasActividad 2 - Nadia Zuleta, Deisreth Ramos y Milagros VillarrealNadia Gisela Zuleta TejadaAún no hay calificaciones

- Mantenimiento y Montaje de Equipos Informáticos - Tema 9 - Texto Completo - WikilibrosDocumento3 páginasMantenimiento y Montaje de Equipos Informáticos - Tema 9 - Texto Completo - WikilibrosLuis Enrique Ramírez LópezAún no hay calificaciones

- Clase No 3 2do Parcial Prog2 08092020Documento11 páginasClase No 3 2do Parcial Prog2 08092020luisAún no hay calificaciones

- Administración comunicaciones oficiales Acuerdo 060Documento8 páginasAdministración comunicaciones oficiales Acuerdo 060sandra patricia cuero montañoAún no hay calificaciones

- Unfv Castillo Neyra Alberto Edgardo Doctorado 2019Documento126 páginasUnfv Castillo Neyra Alberto Edgardo Doctorado 2019Thomas SilvaAún no hay calificaciones

- Como Usar El Tester para Fuentes de Poder de ComputadoraDocumento3 páginasComo Usar El Tester para Fuentes de Poder de ComputadoracasiguanaAún no hay calificaciones

- Guía para El Estudiante 2022-ADocumento90 páginasGuía para El Estudiante 2022-AHermel ChicaizaAún no hay calificaciones

- Alta Presión Bomba LinealDocumento4 páginasAlta Presión Bomba LinealAlex HernandezAún no hay calificaciones

- Gestão Electronica Diesel-Funcionamento 2Documento6 páginasGestão Electronica Diesel-Funcionamento 2Pedro GuedesAún no hay calificaciones

- El Metodo Cientifico en El Desarollo de Protesis.: Una Extencion Artificial para Remplazar La RealDocumento1 páginaEl Metodo Cientifico en El Desarollo de Protesis.: Una Extencion Artificial para Remplazar La RealCynthia Herrera OchoaAún no hay calificaciones

- Caso Práctico - Busexc - Aplicación de Amfe - LaqDocumento7 páginasCaso Práctico - Busexc - Aplicación de Amfe - Laqluis alberto quispe vasquezAún no hay calificaciones

- Acta de Reunion de Desarrollo de Tienda Virtual Reunion 2Documento3 páginasActa de Reunion de Desarrollo de Tienda Virtual Reunion 2Fabian AcostaAún no hay calificaciones

- 1GD InyectorDocumento7 páginas1GD InyectorKevin TtitoAún no hay calificaciones

- Scada Holcim Ecuador PDFDocumento12 páginasScada Holcim Ecuador PDFAnonymous PDEpTC4Aún no hay calificaciones

- Creación de Módulo Instruccional Utilizando PowerPoint 2010Documento13 páginasCreación de Módulo Instruccional Utilizando PowerPoint 2010Edwin E. González CarrilAún no hay calificaciones

- Practicas AliceDocumento33 páginasPracticas Alicecindy mesenAún no hay calificaciones

- Edumatica Plan de Aula EdumaticaDocumento8 páginasEdumatica Plan de Aula Edumaticamariangelica7Aún no hay calificaciones

- C2 P5Documento9 páginasC2 P5Olmos Beyuma Luz NadiaAún no hay calificaciones

- El Riesgo en El Desarrollo de SoftwareDocumento47 páginasEl Riesgo en El Desarrollo de SoftwareMagnoliushkaMandarinishkovaAún no hay calificaciones

- Traductor - Buscar Con GoogleDocumento1 páginaTraductor - Buscar Con GoogleKaren Mariel Cisneros AvilaAún no hay calificaciones

- Guía para Validación de Métodos Analíticos-CNQFB 2002Documento132 páginasGuía para Validación de Métodos Analíticos-CNQFB 2002yaguzman1288% (17)

- Circuito IntegradoDocumento5 páginasCircuito IntegradoJesusAún no hay calificaciones