Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Iee 233 PLL Cap5

Iee 233 PLL Cap5

Cargado por

irosenofTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Iee 233 PLL Cap5

Iee 233 PLL Cap5

Cargado por

irosenofCopyright:

Formatos disponibles

04/06/2014

Qu es un PLL?

Lazos de Enganche por Fase

PLL: Phase-locked loop

Ing. Hugo Pratt

Estado sincronizado

Tambin denominado:

Aplicaciones

En aparatos de televisin

Estado enganchado

Locked state

El error de fase es cero o constante.

Error de =

Fase de

fase

seal de salida

Un circuito que hace que una seal se

salida, generada por un oscilador, siga a

una seal de entrada.

A esto se denomina "sincronizacin".

Dicho de otra manera, el PLL hace que la

seal de salida de un oscilador se

sincronice con una seal de entrada.

La sincronizacin es tanto en frecuencia

como en fase.

Fase de

seal de entrada

aseguran que el color verde se vea como

verde en la imagen de la pantalla.

Para que en la pantalla las cabezas se vean

arriba y los pies abajo.

En aparatos de radio comunicacin

Seleccionar canales de comunicacin

Cada canal tiene una banda de frecuencias

diferente.

Falla de sincronismo vertical

http://yesteryearremembered.com/wpcontent/uploads/2011/06/televisi

on-vertical-hold.jpg

12706/2013

Falla sincronismo horizontal

http://antiqueradio.org/art/Sony8-301WFirstPicture.jpg

12/06/2013

04/06/2014

PLL en uP y uC

Receptor superheterodino GSM

En

comunic

aciones

Aplicaciones

En comunicaciones:

para demodular seales con modulacin FSK

Como parte del circuito para identificacin de

llamadas.

Demodulador FM

Modulacin digital

Software

radio

BSK, QPSK, FSK, QAM

Cualquier otra que se les ocurra.

04/06/2014

Historia

Tipos de PLL

1920: PLL discreto

En base a componentes discretos.

1965: PLL lineal (linear PLL)

Circuito integrado.

Dispositivo lineal (todos sus bloques constitutivos lineales)

Denominado PLL lineal o LPLL.

1970's: PLL Digital

Dispositivo con partes analgicas y partes digitales.

Ms correcto llamarlo PLL de seal mixta.

Denominado DPLL (digital PLL)

1980's PLL totalmente digital

Todas sus partes son digitales.

Denominado ADPLL (all digital PLL)

Slo un chip: 74HC297

LPLL

DPLL

ADPLL

PLL por software (software PLL)

Los ms utilizados actualmente:

LPLL

DPLL

En el curso slo veremos LPLL y DPLL.

Tipo de sistema

PLL lineal y de seal mixta (LPPL, DPLL)

Sistemas de tiempo continuo

PLL totalmente digital (ADPLL)

Sistema de tiempo discreto

Inconveniente:

Elevado rizado (phase jitter)

Por eso se emplea donde es tolerable:

Ejm. demoduladores FSK.

Ref.: http://moodle.insa-toulouse.fr/file.php/60/content/rfc_phase_lock.html

acceso: 14/11/2011

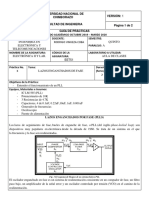

PLL principio funcionamiento

Ref.: http://moodle.insa-toulouse.fr/file.php/60/content/rfc_phase_lock.html

acceso: 14/11/2011

PLL principio de funcionamiento

Ref.: http://moodle.insa-toulouse.fr/file.php/60/content/rfc_phase_lock.html

acceso: 14/11/2011

04/06/2014

PLL

PLL

salida de

voltaje

Seal de

entrada

Detector

de Fase

(phase detector)

u1(t)

1, 1

u2(t)

2, 2

ud(t)

1 2,

e= 1 -2

salida FM

Seal de

entrada

uf

Filtro

de lazo

(loop filter)

Oscilador

Controlado

por voltaje

VCO

u1(t)

1, 1

A veces denominado comparador de fase

(phase comparator)

Genera a su salida una seal aproximadamente

proporcional a la diferencia de fase de sus dos

entradas.

Filtro

de lazo

(loop filter)

u2(t)

2, 2

u2(t)

2, 2

Filtro

de lazo

(loop filter)

Detector de Fase

phase detector

salida de

voltaje o

corriente

ud(t)

1 2,

e= 1 -2

Detector

de Fase

(phase detector)

Detector

de Fase

(phase detector)

salida FM

Oscilador

Controlado

por corriente

CCO

PLL de seal mixta

Seal de

entrada

salida de

corriente

Al menos en un rango pequeo.

Oscilador

Controlado

por voltaje

VCO

En los PLL lineales es un circuito denominado:

oscilador

controlado por

corriente

CCO

Oscilador Controlado por Voltaje

voltage controlled oscilator

Genera una seal peridica, cuya

frecuencia angular es una funcin de su

voltaje de entrada.

En los PLL lineales la salida del VCO es

una onda rectangular.

multiplicador de cuatro cuadrantes

(quadrant multiplier)

Filtro de Lazo

loop filter

la seal a la salida del detector de fase

consta de:

Una componente continua

Una componente alterna.

El filtro permite eliminar la componente

alterna.

04/06/2014

Ref.: R. Best, "Phase-Locked loop", 5th. Ed., 2003, McGraw-Hill

Ref.: R. Best,

"Phase-Locked loop",

5th. Ed., 2003,

McGraw-Hill

Frecuencia central (f0)

central frequency

Terminologa de PLL's

Frecuencia en la mitad del rango de

oscilacin del VCO.

fo= (fmin+fmax)/2

fmin , fmax :frecuencia mnima y mxima que genera

el VCO.

Frecuencia angular central: 0

Rango de enganche

lock range

Rango de frecuencias en las cuales el PLL, si

estaba enganchado, permanece enganchado.

Puede seguir a la seal de entrada.

La desviacin con respecto a la frecuencia

central se denomina en ingls:

hold-in range

tracking range

Rango de enganche

lock range

Limitado por:

El rango de error de voltaje que se puede

generar.

La ganancia del VCO (desviacin de

frecuencia por unidad de voltaje).

Es un parmetro DC o esttico.

Pues la seal de error ser un voltaje DC una

vez enganchado.

No depende del ancho de banda del filtro.

04/06/2014

Rango de captura

capture range

Rango de frecuencias en las que el PLL, si no

est enganchado, o pierde la sincrona, llega a

engancharse.

Tambin denominado:

Rango de adquisicin (acquisition range).

La desviacin con respecto a la frecuencia

central se denomina:

Pull-in range

Lock-in range

Rango de captura

capture range

Puede ser cualquier intervalo dentro del

rango de enganche (centrado en 0).

Depende principalmente de:

La selectividad del filtro

Ancho de banda y pendiente en banda de

transicin y de rechazo.

Tipo de detector de fase.

La ganancia en lazo cerrado del PLL.

Tiempo de enganche

lock-up time

El tiempo transitorio requerido por un PLL que

est oscilando a su frecuencia central f0 para

engancharse.

Depende principalmente de la selectividad del

filtro (ancho de banda):

Es inversamente proporcional a la selectividad del

filtro.

Presenta algo de incertidumbre debido a la

aleatoriedad de la diferencia de fase inicial entre

la seal de entrada y la salida del oscilador.

Lock-in time, Pull-in time

R. Best da dos definiciones diferentes para el

tiempo de enganche:

Lock-in time:

El tiempo transitorio requerido por un PLL que est

oscilando a su frecuencia central f0 para

engancharse, cuando el proceso de adquisicin es

rpido.

Pull-in time:

El tiempo transitorio requerido por un PLL que est

oscilando a su frecuencia central f0 para

engancharse, cuando el proceso de adquisicin es

lento.

Relacin entre rangos

hold-in range

hold-in range

rango de enganche

pull-in range

pull-in range

PLL de seal mixta

rango de captura

04/06/2014

LPLL vs DPLL

LPLL

Detector de fase, filtro de

lazo y VCO son lineales

(analgicos)

Su analoga es el

OPAMP

Diseado para tener una

relacin E/S lineal.

Utilizado normalmente con

realimentacin negativa

para mejorar la linealidad.

DPLL

El detector de fase es

digital. Filtro de lazo y

VCO lineales.

Su analoga es el

comparador.

Diseado para tener dos

estados a la salida (no

lineal). Aplicaciones

digitales.

Utilizado normalmente en

lazo abierto. Rara vez se

intenta mejorar linealidad.

DPLL: Diagrama de bloques

LPLL & DPLL: Usos

LPLL

En sistemas de comunicaciones analgicas

Pues mantienen relaciones lineales entre las

seales de salida y las entradas.

DPLL

Sincronizacin de seales digitales

Recuperacin de seales de reloj

A partir de la trama de datos digital codificada.

Otras aplicaciones digitales.

Detector de Fase

La parte ms importante del PLL.

Pues aqu se comparan las fases de la seal

de entrada y del VCO.

Ref.: R. Best, "Phase-Locked loop", 5th. Ed., 2003, McGraw-Hill

Detector de Fase: Tipos

Detector de Fase: Seales

LPLL

Multiplicador lineal (linear multiplier)

DPLL

Compuerta O exclusivo (exclusive or)

Denominado EXOR o XOR

Flip-flop JK

Detector de fase y frecuencia (phase and

frequency detector)

Denominado PFD

En los detectores de fase:

Compuerta O exclusivo (EXOR)

Flip-flop J-K

Detector de fase y frecuencia (PFD)

Las seales de entrada son seales

digitales binarias.

Tanto de la seal de referencia como la

proveniente del VCO o contador.

04/06/2014

Detector de fase EXOR

Hay inherentemente una diferencia de

fase de 90entre la seal de entrada y la

del VCO (o salida del contador, de

usarse).

Sus salidas requieren mayor filtraje debido

a la gran variacin de voltaje de nivel bajo

a nivel alto en la salida.

Tambin denominado XOR (exclusive or)

Detector de fase EXOR

En estado enganchado (f1=f2'):

Si las seales de entrada son cuadradas:

Cuando e=0, la salida es una onda cuadrada

del doble de frecuencia.

Ciclo de trabajo de ud: 50%

Detector de fase EXOR

Como hay inherentemente una diferencia de

fase de 90entre la seal de entrada y la del

VCO o contador:

Se define el error de fase como:

error de fase e = diferencia de fase - 90

Diferencia de

fase: 90

e=0

Detector de fase EXOR

En estado enganchado (f1=f2'):

Si las seales de entrada son cuadradas:

Cuando e>0, la salida en ud es una onda

rectangular con ciclo de trabajo mayor a 50%.

e > 0

e=0

ud: onda cuadrada

con f=2f1

e > 0

ud: onda rectangular

con f = 2f1

y ciclo de trabajo > 50%

Obtencin de KD

La zona

sombreada es el

tiempo extra que

est ud en nivel

alto, respecto a

e=0

e >0

T

e, TH

T = 2 = TH + TL

TH = + 2 e

TL = 2 e

04/06/2014

Si:

VOH voltaje de salida en nivel alto

VOL voltaje de salida en nivel bajo

ud =

ud =

Entonces:

ud =

TH VOH + TL VOL

TH + TL

( + 2 e ) VOH + ( 2 e ) VOL

VOH + VOL e (VOH VOL )

+

2

Detector de fase EXOR

La salida digital tiene dos niveles: alto y

bajo.

Si VOH = VCC y VOL = 0V

Entonces:

V

V

ud = CC + CC e

Bajo: VOL 0V

Alto: VOH VCC

El filtro de lazo rechazar la componente

alterna, quedando slo la componente

continua.

Este es el promedio de la seal de salida.

0.5*(VOH+VOL)

Detector de fase EXOR

El promedio de ud:

Diferencia de

fase: 90

e=0

Es mximo cuando e = 90

Es mnimo cuando e = -90

Se define la funcin d como el promedio

de ud respecto al promedio cuando e = 0

d es exactamente proporcional a e.

d = Kde -/2 < e < /2

con Kd = (VOH-VOL)/

Ref.: Fig. 2.6,

R. Best, "PhaseLocked loop" , 5th.

Ed., 2003, McGrawHill

04/06/2014

Detector de Fase EXOR

EXOR

Limitaciones

Si una o ambas seales de entrada no tienen

forma de onda cuadrada:

El rango de variacin de ud disminuye.

Ocurre enclavamiento en los lmites superior e

inferior.

Curva de transferencia tiene forma triangular recortada.

Detector de fase y frecuencia

Ref.: Fig. 2.7,

R. Best, "PhaseLocked loop" , 5th.

Ed., 2003, McGrawHill

Detector de fase y frecuencia

"1"

u1

u'2

"1"

Ref.: Fig. 2.11, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Ref.: Fig. 2.12, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Detector de fase y frecuencia

Detector de fase y frecuencia

Ref.: Fig. 2.13a, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Ref.: Fig. 2.13b, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

10

04/06/2014

Detector de fase y frecuencia

Ref.: Phase-Locked Loops Engineering

Handbook for Integrated Circuits

Goldman, Stanley . Artech House, 2007

Ref.: Fig. 2.13, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

PFD con fuentes de corriente

Detector de fase y frecuencia

Ref.: Fig. 2.14, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Ref. MT-086 Fundamentals of Phase Locked Loops (PLLs) , Analog Devices

VREF

R2

VCOIN

I2 =

R1

I1 =

Detector de fase y frecuencia

I3

VCO

Ref.: Fig. 2.15, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Inicialmente:

C1 descargado

Q1, Q4 conducen

Q2, Q3 abiertos

VCO habilitado

(INH = 0)

Q1

Q3

Q2

Q4

11

04/06/2014

mientras V67 < VREF

Funcin de transferencia

Salida VCO

I3

Detector de fase

1

Q1

Q3

0

Q2

ud(t)=Kde

Ud(s)=Kd

Vlido slo para:

Q4

Multiplicador de 4 cuadrantes

XOR

J-K

Filtro:

F(s)=UF(s)/Ud(s)

Diagrama de Bloques

Funcin de transferencia

Detector de

Fase

VCO:

u2(t)=rect(2t)

Pero: 2t = 0t+2= (0+K0uf)t

Entonces: 2=K0uft , => d(2)/dt=K0uf

2(s)/UF(s)=K0/s

Filtro

entrada

1(s)

+

UF(s)

UD(s)

Kd

VCO

F(s)

2(s)

K0

s

2(s)

Funcin de Transferencia

K

K d F ( s) 0

2

s

H (s) =

=

1 1 + K F ( s ) K 0

d

s

Funcin de error

e = 1 2

He =

e (s)

s

=

1 ( s ) s + K 0 K d F ( s)

H e = 1 H (s)

12

04/06/2014

Modelando el PLL con varios filtros

pasabajos

A este Filtro se le conoce

como FPB Tipo A

F ( s) =

R1

Vs

Ve

F ( s) =

1 / 1

A este Filtro se le

conoce como filtro

adelanto-atraso

(lead-lag filter)

R2

1

1 + s 1

1 + s 2

1 + s( 1 + 2 )

El denominador tiene la forma:

1

1 + 2

Cortesa: Prof. Miguel Catao

1 / 1

Funcin de transferencia del PLL con el

Filtro tipo adelanto-atraso

H ( s) =

Kd K0

1 + s 2

*

1 + 2 s 2 + 2 n s + n2

K K

1 + s 2

H ( s) = d 0

1 + 2 2s 2 + n + 2

n

Q

n2

Entonces tenemos:

Kd Ko

1 + 2

(Ec. 5)

n

2

( 2 +

s 2 + 2 n s + n2

(Ec. 2)

(Ec. 3)

Donde:

Funcin de transferencia en

funcin de n y

PLL con filtro atraso-adelanto

Reemplazando Ec.5, Ec.6 en Ec. 2

2s 2 +

n

Q

+ n

Haciendo 2 = 0

n =

1

)

Kd Ko

tambin:

Para el Filtro tipo A

n =

Funcin de transferencia del PLL con el

Filtro tipo adelanto-atraso

1 + s 2

K

K

Kd

0

K d F (s) 0

2

1

+

s

(

+

)

s

s =

1

2

H (s) =

=

K

K

1

+

s

1 1 + K F ( s ) 0 1 + K

2

0

d

d

s

1 + s( 1 + 2 ) s

K K

1 + s 2

H ( s) = d o *

1 + 2 s 2 + s 1 + K d K o 2 + K d K o (Ec. 1)

1 + 2

1 + 2

Kd Ko

1

1

2 1K d K o

2 = R2C

1 = R1C

(Ec. 6)

Cortesa: Prof. Miguel Catao

Funcin de transferencia para lazo

de alta ganancia (KdKo>>wn)

En ese caso la funcin se aproxima a:

2n s + n

H (s) = 2

2

s + 2n s + n

2

n

+ n 2

sn 2

K 0 K d

H ( s) =

2

s 2 + 2 n s + n

Si K0Kd >> n

Se dice que el PLL es de alta ganancia de

lazo (lo ms comn)

y He a:

H e (s)

s2

s 2 + 2 n s + n

13

04/06/2014

Funcin de error para =0.707

Ref.: Fig. 2.14, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Respuesta a un escaln de fase

Ref.: Fig. 2.14, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Respuesta a un escaln de fase

1 (t ) = u (t )

1 ( s ) =

2 ( s) = H (s)

2 (t ) = L1 H ( s)

2 (t ) = L1 H ( s)

Donde: u(t) es la funcin escaln.

El error: e(t)= 1(t)- 2(t)

Donde: u(t) es la funcin escaln.

El error: e(t)= 1(t)- 2(t)

Respuesta a un escaln de

frecuencia

1 (t ) = u (t ) t

1 ( s) =

s2

s2

2 (t ) = L1 H ( s ) 2

s

2 ( s) = H ( s )

Eje horizontal: nt (rad)

Ref.: Fig. 2.14, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Donde: u(t) es la funcin escaln.

El error: e(t)= 1(t)- 2(t)

14

04/06/2014

Ejemplos de PLL ideal

VCC

Circuito PLL con detector PFD

S1

VSWITCH

U1(CLK)

R1

U1

VDD

CLK

SET

RESET

D

U1(Q)

C1

10nF

!Q

U3

DTFF

S2

VSWITCH

B

U2(CLK)

VDD

AND

U2

CLK

SET

RESET

D

C1(1)

10k

U2(Q)

!Q

DTFF

VCC

U4

Q

EN

VIN

DVCO

Ref.: Fig. 2.14, R. Best, "Phase-Locked loop" , 5th. Ed., 2003, McGraw-Hill

Proceso de enganche. Psi = 0.707

Proceso de enganche. Psi = 1.0

VCO: [0, 10KHz], 0V-5V

Filtro: = 0.7, n=7070rad/s C=10nF, R=10K

Escaln de frecuencia: 0Hz a 9KHz

Escala horizontal (ambas grficas): 0 a 2ms

VCO: [0, 10KHz], 0V-5V

Filtro: = 1.0, n=10000 rad/s C=10nF, R=50K

Escaln de frecuencia: 0Hz a 9KHz

Escala horizontal (ambas grficas): 0 a 5ms

PLL Lineal

Proceso de enganche. Psi = 0.6

VCO: [0, 10KHz], 0V-5V

Filtro: = 0.6, n=6000 rad/s C=10nF, R=13.9K

Escaln de frecuencia: 0Hz a 9KHz

Escala horizontal (ambas grficas): 0 a 5ms

15

04/06/2014

Consideremos una seal de entrada que tiene dos

componentes vi(t) y vk(t):

u1 (t ) = vi (t ) + vk (t ) = Vi sen(i t + i ) + Vk sen(k t + k ) (1)

Donde i y k son las fases respecto a la fase de la seal del

VCO.

La onda rectangular, de amplitud pico V2, generada por

el VCO en base a la seal de error es:

u 2 (t ) =

n =0

4 V2

( 2n + 1)

cos[(2n + 1)0t ]

Ref.: R. Best, "Phase-Locked loop", 5th. Ed., 2003, McGraw-Hill

La salida del

multiplicador

sera:

2 KV2 Vi

sen[( 2n + 1)0t i t i ]

n = 0 2n + 1

V

i sen[(2n + 1)0t + i t + i ]

n = 0 2n + 1

+

n =0

n =0

Vk

sen[(2n + 1)0t k t k ]

2n + 1

Vk

sen[(2n + 1)0t + k t + i ]

2n + 1

Si 0 est cercano a i:

ud (t ) = K u1 (t ) u2 (t ) =

2 K V2 Vi

sen[( 2n + 1)0t it i ]

n=0 2n + 1

Si slo existiera la componente vi(t) (vk(t)=0) la

salida del multiplicador sera:

ud (t ) = K u1 (t ) u2 (t ) =

Vi

sen[( 2n + 1)0t + it + i ]

n =0 2 n + 1

Para n>0:

Todas las armnicas

estn alejadas ms

de 20 de i

Para n>0, todas

las armnicas

estn alejadas

ms de 40 de i

ud (t ) = K u1 (t ) u2 (t ) =

2 K V2 Vi

sen[( 2n + 1)0t it i ]

n=0 2n + 1

n =0

Vi

sen[( 2n + 1)0t + it + i ]

2n + 1

En la primera sumatoria:

Se obtiene un valor constante si:

i = 0

i = (2n+1)0

En la segunda sumatoria:

Nunca hay una componente continua.

16

04/06/2014

En estado de enganche

La componente continua a la salida del

detector de fase es:

Cuando i = 0:

Habr una componente continua y una

alterna (C.A.):

ud (t ) =

2 K V2 Vi

ud =

ud =

sen[ i ]

Proporcional a la amplitud de la seal de

entrada.

Proporcional al seno de la diferencia de

fase.

ud debe tener el valor suficiente para lograr

que el VCO llegue a la frecuencia i.

sen[ i ] + C. A.

2 K V2 Vi

2 K V2 Vi

sen[ i ]

Ganancia detector de fase

Si se cumple:

Haciendo: K d =

diferencia de fase e<<1

Entonces:

ud

2 K V2 Vi

Entonces:

2 K V2 Vi

ud = K d e

Donde:

e Error de fase

Vi Amplitud pico de la componente espectral de inters

de la seal de entrada.

V2 Amplitud pico de la onda cuadrada generada por el

VCO.

PLL Lineal

Multiplicador

de 4

cuadrantes

Seal de

entrada

u1(t)

1, 1

Detector

de Fase

(phase detector)

u2(t)

2, 2

Filtro

de lazo

(loop filter)

salida FM

uf

Oscilador

Controlado

por voltaje

VCO

2 = 0 + K 0 u f

e Error de fase

Kd ganancia del detector de fase (V/rad), cuando el

PLL est enganchado.

Precisiones

ud = K d e

ud(t)

Donde:

K0: Ganancia del VCO (rad/s/V)

Si el PLL est enganchado:

Slo hay componente continua a la salida del

filtro.

Por tanto, el rango de enganche es

independiente del ancho de banda del filtro

de lazo.

Pero si hay ruido u otras componentes de

la seal de entrada, el ancho de banda s

determina cun probable es que se

desenganche.

17

04/06/2014

Al reducir el ancho de banda

del filtro

El proceso de captura se hace ms lento.

El rango de captura disminuye.

las propiedades de rechazo a las interferencias mejoran.

Pues la componente de error causado por las interferencias se

atena ms.

La respuesta transitoria del lazo ante cambios sbitos de

la frecuencia de entrada( dentro del rango de captura)

se hace subamortiguado.

Esto pone un lmite inferior al ancho de banda y a la pendiente

en la zona de transicin y banda de rechazo del filtro de lazo.

18

También podría gustarte

- Detector de Fase-InformeDocumento5 páginasDetector de Fase-InformejohnpiryukAún no hay calificaciones

- Será Mejor Que Lo Cuentes. PRIMER CAPÍTULO - Antonio NúñezDocumento22 páginasSerá Mejor Que Lo Cuentes. PRIMER CAPÍTULO - Antonio NúñezJonatan Molina Torres100% (3)

- Control de Frecuencia Con PLLDocumento13 páginasControl de Frecuencia Con PLLGiancarlo Villanueva OropezaAún no hay calificaciones

- Guia5 6-PLL DemodulacionFSKDocumento7 páginasGuia5 6-PLL DemodulacionFSKRamiro Alonso Bruz SilvaAún no hay calificaciones

- Exp 10 PLL 1 2Documento37 páginasExp 10 PLL 1 2AlexandreAún no hay calificaciones

- Laboratorio 4 Grupo 1Documento9 páginasLaboratorio 4 Grupo 1Carlos Carrillo ZapataAún no hay calificaciones

- Guía de Prácticas PLL-1Documento11 páginasGuía de Prácticas PLL-1Jamil NinaAún no hay calificaciones

- 8 Demodulador FMDocumento15 páginas8 Demodulador FMErick PonceAún no hay calificaciones

- 6-4-Apendice 4 Circuitos de Fase Cerrada PLLDocumento16 páginas6-4-Apendice 4 Circuitos de Fase Cerrada PLLAbraham ZavaletaAún no hay calificaciones

- PLLDocumento5 páginasPLLArsenio VillanuevaAún no hay calificaciones

- PLLDocumento16 páginasPLLTazann24Aún no hay calificaciones

- 5 Práctica 5Documento3 páginas5 Práctica 5Luis Angel Nina SánchezAún no hay calificaciones

- Semana 8 - PLLDocumento8 páginasSemana 8 - PLLHernan Calvo SantiagoAún no hay calificaciones

- Lazos de Fase CerradaDocumento2 páginasLazos de Fase CerradajavierAún no hay calificaciones

- Circuitos Integrados E J 2023Documento51 páginasCircuitos Integrados E J 2023Luis Antonio PérezAún no hay calificaciones

- Informe PLLDocumento7 páginasInforme PLLArias D. CristianAún no hay calificaciones

- Modulador y Demodulador FSKDocumento23 páginasModulador y Demodulador FSKJose Patricio Rubio OrozcoAún no hay calificaciones

- Lazos Enganchados en Fase y Multiplicadores - Pablo GamezDocumento24 páginasLazos Enganchados en Fase y Multiplicadores - Pablo GamezMauricio Orlando Ovando GarciaAún no hay calificaciones

- Informe PLLDocumento7 páginasInforme PLLDaniel Mesa100% (1)

- Demodulador PLLDocumento7 páginasDemodulador PLLSorenllyAún no hay calificaciones

- Introduccion A Los PLLDocumento13 páginasIntroduccion A Los PLLpablo9vAún no hay calificaciones

- Lazo Cerrado de Fase (PLL)Documento5 páginasLazo Cerrado de Fase (PLL)Erick Africano MejiaAún no hay calificaciones

- Proyecto Final PLLDocumento41 páginasProyecto Final PLLJorge Deza ConcoriAún no hay calificaciones

- Comunicaciones IDocumento14 páginasComunicaciones IRelaxing RainAún no hay calificaciones

- PLL 4046Documento6 páginasPLL 4046Carlos RamosAún no hay calificaciones

- Guia 5 Ctos IIIDocumento4 páginasGuia 5 Ctos IIIFernando Gutierrez OportoAún no hay calificaciones

- TL 494Documento8 páginasTL 494SOPHIE PCJONAún no hay calificaciones

- Informe PLLDocumento10 páginasInforme PLLRubenCalleSanchezAún no hay calificaciones

- CD4046Documento15 páginasCD4046Victor SanchezAún no hay calificaciones

- Sintetizador de Frecuencias ExpoDocumento26 páginasSintetizador de Frecuencias ExpoDeyvis Juli YabarAún no hay calificaciones

- Multiplicador LM565 - ReporteDocumento3 páginasMultiplicador LM565 - ReporteAngel CondeAún no hay calificaciones

- Informe PLLDocumento5 páginasInforme PLLJuanCarlosAún no hay calificaciones

- Guia 2 de Electronica de Comunicaciones 2018 - PDFDocumento3 páginasGuia 2 de Electronica de Comunicaciones 2018 - PDFFernando VargasAún no hay calificaciones

- Reporte Práctica 8Documento10 páginasReporte Práctica 8Abimael SimbronAún no hay calificaciones

- Mallas de Fase EncadenadaDocumento11 páginasMallas de Fase EncadenadaCars SandovalAún no hay calificaciones

- TemporizadorDocumento21 páginasTemporizadorYERSON CRISTOBAL VICENTEAún no hay calificaciones

- Laboratorio 4 PPL LM656Documento6 páginasLaboratorio 4 PPL LM656Oscar Alejandro Feria PrietoAún no hay calificaciones

- El 555 Es Un Circuito Integrado Cuya Función Principal Es Producir Pulsos de Temporización Con PrecisiónDocumento57 páginasEl 555 Es Un Circuito Integrado Cuya Función Principal Es Producir Pulsos de Temporización Con PrecisiónlimberAún no hay calificaciones

- Osciladores Controlados Por Tensión (Vco) - PLLDocumento20 páginasOsciladores Controlados Por Tensión (Vco) - PLLAlex VinAún no hay calificaciones

- Practica 4analogicos2Documento9 páginasPractica 4analogicos2Hugho FigueroaAún no hay calificaciones

- Cap 11Documento49 páginasCap 11Nitabo EstradaAún no hay calificaciones

- Lazo Amarrado Por FaseDocumento5 páginasLazo Amarrado Por FaseJulian Prieto RiverosAún no hay calificaciones

- Aplicaciones PLLDocumento32 páginasAplicaciones PLLEduardo RomeroAún no hay calificaciones

- Informe de Laboratorio - PLLDocumento12 páginasInforme de Laboratorio - PLLJuan David Cardenas AcostaAún no hay calificaciones

- PLL Daniel5TODocumento10 páginasPLL Daniel5TODavid FernandezAún no hay calificaciones

- 555 AstableDocumento11 páginas555 AstableCarlos RozAún no hay calificaciones

- Presentacion Tema 2 Parte 2Documento16 páginasPresentacion Tema 2 Parte 2fuedcheddad5Aún no hay calificaciones

- Repa Tv139Documento4 páginasRepa Tv139Mariano Cabrales LabastidasAún no hay calificaciones

- Manejo 555 e Introducción A Flip FlopsDocumento22 páginasManejo 555 e Introducción A Flip FlopsNicoll GonzalezAún no hay calificaciones

- De Moduladores FMDocumento10 páginasDe Moduladores FMMarko Montalban MonteroAún no hay calificaciones

- PLL InformeDocumento4 páginasPLL InformericardoAún no hay calificaciones

- Electrónica de ComunicacionesDocumento6 páginasElectrónica de Comunicacionesjoine0Aún no hay calificaciones

- Curso Ur AlmaDocumento88 páginasCurso Ur AlmaMiroslav Vulinovic100% (1)

- Multiplicador de Frecuencia x10 CompletoDocumento14 páginasMultiplicador de Frecuencia x10 CompletoDavid Pamo100% (1)

- Modulador y Demodulador FSKDocumento11 páginasModulador y Demodulador FSKChristian RuizAún no hay calificaciones

- Sistemas Electronicos Digitales - 4 - Guia n3Documento13 páginasSistemas Electronicos Digitales - 4 - Guia n3Franz LluscoAún no hay calificaciones

- Filtro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoDe EverandFiltro adaptativo: Mejora de la visión por computadora mediante filtrado adaptativoAún no hay calificaciones

- 100 Circuitos de Audio (ES) - volume 1De Everand100 Circuitos de Audio (ES) - volume 1Calificación: 5 de 5 estrellas5/5 (2)

- Manual Motorola Pro 5100 Esp CompressDocumento58 páginasManual Motorola Pro 5100 Esp CompressYadin Mena SanchezAún no hay calificaciones

- Ensamble de Violas de BoliviaDocumento4 páginasEnsamble de Violas de BoliviaSoleitoAún no hay calificaciones

- Datos de Los EstudisntesDocumento13 páginasDatos de Los EstudisntesTEODOROAún no hay calificaciones

- Viga RESEÑADocumento2 páginasViga RESEÑAMoises Martinezz SalazarAún no hay calificaciones

- Razonamiento Verbal 1bim 4 SDocumento7 páginasRazonamiento Verbal 1bim 4 SMilagriitoss C. AngelitaAún no hay calificaciones

- Dinamica 6 EquipajesDocumento2 páginasDinamica 6 EquipajesWilliam FloresAún no hay calificaciones

- ADORNOSDocumento6 páginasADORNOSPathrycia MendozaAún no hay calificaciones

- Mineduc Me 2015 00065 A Curriculo Colegios de Arte Musica JaimemolaDocumento1 páginaMineduc Me 2015 00065 A Curriculo Colegios de Arte Musica JaimemolaTreidys PerdomoAún no hay calificaciones

- Plano de Ubicación y Localización de Lote Por PrescripciónDocumento1 páginaPlano de Ubicación y Localización de Lote Por PrescripciónWily R. Flores Rivera100% (1)

- Agatha ChristieDocumento1 páginaAgatha ChristieFernando A. Mejia LAún no hay calificaciones

- Jovenes Brujula 2 Olaya RafaelDocumento9 páginasJovenes Brujula 2 Olaya RafaelGisela Margarita MezaAún no hay calificaciones

- ACTIVIDAD 10 DE DICIEMBRE ArteDocumento2 páginasACTIVIDAD 10 DE DICIEMBRE ArteAlexsa Liana Romero DiazAún no hay calificaciones

- Camacho Martha S4 PI My Personal Blog WORDDocumento3 páginasCamacho Martha S4 PI My Personal Blog WORDMartita CamachoAún no hay calificaciones

- Señal PALDocumento54 páginasSeñal PALLau BenalcazarAún no hay calificaciones

- La Historia de AcordeDocumento3 páginasLa Historia de Acordedagaza01Aún no hay calificaciones

- Monografia de DanzaDocumento26 páginasMonografia de Danzaisabel100% (1)

- Texto ExpositivoDocumento11 páginasTexto Expositivocenterglobalservicec.g.s. Globalservice100% (1)

- ExoplanetasDocumento3 páginasExoplanetasbrayanAún no hay calificaciones

- Gustad y Ved PDFDocumento2 páginasGustad y Ved PDFRichard Daniel Espinoza Gamboa100% (1)

- Ue40f6400aw - Especificaciones Técnicas - Atención Al Cliente - SamsungDocumento6 páginasUe40f6400aw - Especificaciones Técnicas - Atención Al Cliente - Samsungunivkey1Aún no hay calificaciones

- Ejercicios SICODI IIDocumento3 páginasEjercicios SICODI IIJair Flores CaroAún no hay calificaciones

- Estudiantes Procesos 1Documento2 páginasEstudiantes Procesos 1jehseed chiaraAún no hay calificaciones

- Laboratorio 1-2022-IDocumento13 páginasLaboratorio 1-2022-Imary pinzonAún no hay calificaciones

- Teatro Del Siglo XXi AntuñanoDocumento16 páginasTeatro Del Siglo XXi AntuñanoJuan Antonio Coba Rosado100% (1)

- Capitulo 5 Uplink Downlink y Rendimiento General de Un Enlace SatelitalDocumento19 páginasCapitulo 5 Uplink Downlink y Rendimiento General de Un Enlace SatelitaljesusAún no hay calificaciones

- Maelstrom Borrado1Documento76 páginasMaelstrom Borrado1LAURA GARCIA GARCIAAún no hay calificaciones

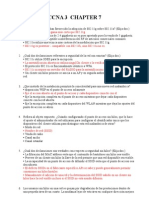

- Examen Ccna 3 Capitulo 7 ESPDocumento4 páginasExamen Ccna 3 Capitulo 7 ESPshf06Aún no hay calificaciones

- Lista de Canales Satelite NS806Documento32 páginasLista de Canales Satelite NS806Oscar Garcia CruzAún no hay calificaciones

- Troubleshooting SMSCDocumento44 páginasTroubleshooting SMSCMiguel BarcoAún no hay calificaciones