Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Diseño de Circuitos Lógicos

Diseño de Circuitos Lógicos

Cargado por

Edwin Florez AnzolaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Diseño de Circuitos Lógicos

Diseño de Circuitos Lógicos

Cargado por

Edwin Florez AnzolaCopyright:

Formatos disponibles

D.I.I.C.

C Arquitectura de Sistemas Computacionales

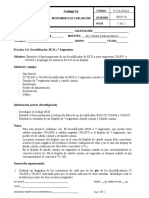

CAPITULO 7 .- DISEO DE CIRCUITOS LOGICOS

7.1 INTRODUCCION

l diseo de los circuitos de combinacin comienza con la descripcin verbal del problema y termina en un diagrama de circuito lgico. El procedimiento comprende los siguientes pasos: Se enuncia el problema. A las variables de entrada y salida se les asignan smbolos de letras. Se deriva la tabla de verdad que define las relaciones entre entradas y salidas. Las funciones Booleanas simplificadas se obtienen para cada una de las salidas. Se dibuja el diagrama lgico.

7.2 Circuitos Lgicos Tradicionales

7.2.1 Semi-sumador

La funcin aritmtica digital ms bsica es la suma de dos dgitos binarios. Un circuito de combinacin que realiza esta suma aritmtica de dos bits se denomina un semi - sumador. Uno que realiza la suma de tres bits (dos bits significantivos y un bit previo de acarreo) se denomina un sumador completo. El nombre para el ltimo se basa en el hecho de que se pueden utilizar dos semi - sumadores para implementar un sumador completo. Las variables de entrada de un semi - sumador se denominan bits sumando y sumador. Las variables de salida se denominan suma y acarreo. Es necesario especificar dos variables de salida puesto que la suma de 1+ 1 es el binario 10, que tiene dos dgitos. Asignamos los smbolos XY a las dos variables de entrada, y S (para la suma) y C (para el acarreo) a las dos variables de salida. La salida C es 0 a no ser que ambas entradas sean 1. La salida S representa el bit menos significativo de la suma. Las funciones Booleanas para las dos salidas pueden obtenerse directamente de la tabla de verdad: Tabla de Verdad:

X 0 0 1 1 Y 0 1 0 1 C 0 0 0 1 S 0 1 1 0

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 1

D.I.I.C.C Arquitectura de Sistemas Computacionales

De la tabla de verdad se obtienen las siguientes funciones: 1).2).Para la Suma Para el Carrie (Acarreo)

S = xy + xy = x y C = xy

A partir de estas dos ecuaciones podemos implementar el siguiente circuito lgico:

Circuito lgico de un Semi - Sumador.

El diagrama lgico se muestra en la Figura, consiste de una compuerta exclusiva OR y de una compuerta AND. Adems se ha utilizado un generador de aleatorio de entrada y sendos display para rutear los valores en cuestin. 7.2.2 Sumador-completo

El sumador - completo es un circuito de combinaciones que forma la suma aritmtica de tres bits. Consiste de tres entradas y dos salidas. Dos de las variables de entrada, denotadas por X e Y, representan los dos bits significativos que deben sumarse. La tercera entrada, Z, representa el acarreo de la posicin significante previa ms baja. Las dos salidas son necesarias porque la suma aritmtica de tres dgitos binarios est en el rango de 0 a 3, y los binarios 2 3 necesitan dos dgitos. Las dos salidas son designadas por los smbolos S (para la suma) y C (para el acarreo). La variable binaria S da el valor del bit menos significativo de la suma. La variable binaria C de la salida del acarreo. Las ocho filas debajo de las variables de entrada designan todas las combinaciones posibles de 1s y 0s que estas variables pueden tener. Los 1s y 0s para las variables de salida

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 2

D.I.I.C.C Arquitectura de Sistemas Computacionales

son determinados de la suma aritmtica d los bits de entrada. Cuando todos los bits de entrada son 0 la salida es 0. La salida S es igual a 1 cuando solamente una entrada es igual a 1 o cuando todas las tres entradas son iguales a 1. La salida C tiene un acarreo de 1 si dos o tres entradas son iguales a 1. Los mapas de Karnaugh, son utilizados para encontrar expresiones algebraicas para cada una de las variables de salida. Los 1s en los cuadrados de los mapas de S y C se determinan directamente de los minterms en la tabla de verdad. Los cuadrados con 1s para la salida S no se combinan en grupos de cuadrados adyacentes. Pero puesto que la salida es 1 cuando hay un nmero impar de entradas, S es una funcin impar, y representa la relacin OR exclusivo de las variables Los cuadrados con 1 para la salida C pueden combinarse en una diversidad de maneras. Una expresin posible de C es: C = xy + (xy + xy)z, la cual obtendremos a partir del siguiente desarrollo: Tabla de verdad

Entradas X Y Z 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Salidas C S 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1

Mapa de Karnaugh:

Del mapa se obtienen las siguientes ecuaciones: 1).2).-

S = xyz + xyz + xyz + xyz = x y z C = xy + xz + yz = xy + ( xy + xy ) = xy + ( x y ) z

A partir de estas ecuaciones obtenidas por la minimizacin del mapa de Karnaugh, podemos implementar el siguiente circuito lgico.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 3

D.I.I.C.C Arquitectura de Sistemas Computacionales

Circuito Lgico

Circuito Lgico de un Sumador Completo

Teniendo en cuenta que xy + xy = x y, e incluyendo la expresin para la salida S, obtenemos las dos funciones para el sumador - completo:

S =xyz C = xy + ( x y ) z

Note que el circuito sumador - completo consta de dos semi sumadores y una compuerta OR. A dems se ha agregado un generador de entradas aleatorio ms display de ruteo. Este circuito se puede representar por un circuito integrado de la siguiente manera. Cabe hacer notar que dentro de este circuito estar el subcircuito diseado anteriormente.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 4

D.I.I.C.C Arquitectura de Sistemas Computacionales

7.2.3

Comparadores

Un circuito Comparador detecta una concidencia de valores de dos o ms seales lgicas. Este circuito se puede representar a partir de la siguiente tabla de verdad: Tabla de Verdad:

A 0 0 1 1 B 0 1 0 1 SALIDA (1 = Iguales, 0 = distintos) 1 0 0 1

De la tabla de verdad se obtiene la siguiente ecuacin: S = AB + AB . A pesar de la simplicidad de la tabla de verdad, son necesarias cinco compuertas lgicas para esquematizarla. La salida ser 1, si A=B, sino ella ser 0. Los comparadores ms sofisticados presentan elementos lgicos con dos salidas adicionales: una para la salida , si A >B, y la otra salida 1 cuando B > A. Existen comparadores de ms de dos bit , en este caso, se torna esencial el uso de un inversor (compuerta NOT) para cada bit y puertas AND con tantas entradas como nmero de bits de entrada y se necesita apenas una puerta OR. Los chip disponibles comercialmente no slo tienen salidas para A=B, sino tambin para A<B y para A>B. A partir de la ecuacin encontrada S = AB + AB podemos construir el siguiente circuito lgico:

Circuito lgico de un Comparador de 2 bits

Ntese que la tabla de verdad utilizada en el comparador, es semejante a la tabla OR - Exclusivo, solo que las salidas estn negadas, por lo tanto ste comparador tambin puede ser implementado con compuertas OR - exclusivo. A continuacin se presenta un comparador de 4 bit utilizando compuertas OR - exclusivo.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 5

D.I.I.C.C Arquitectura de Sistemas Computacionales

El circuito est basado en la puerta OR EXCLUSIVO, que da 0 si las entradas son iguales y 1 si son distintas. Si las dos palabras, son iguales, las cuatro puertas OR - EXCLUSIVO deben dar 0. Despus se pueden pasar estas cuatro salidas por una puerta OR, que dar 0 si las palabras son iguales y 1 si son diferentes. En nuestro ejemplo hemos usado una puerta NOR en la etapa final para invertir el sentido de la comparacin: 1 significa igual y 0 desigual.

Circuito lgico de un Comparador de 4 bits

7.2.4

Decodificadores

Un Decodificador es una funcin digital que convierte informacin binaria de una forma codificada a otra. Por ejemplo, un Decodificador BCD de siete segmentos convierte un dgito decimal en BCD (Decimal Codificado en Binario) en siete salidas para la seleccin de un conjunto de segmentos necesarios para exhibir un dgito decimal. Los Decodificadores presentados en sta seccin son denominados Decodificadores de Lnea n - a - 2n y su propsito es generar los 2n miniterm de las n variables de entrada. Estos codificadores forman un circuito de combinacin con n variables de entrada y 2n variables de salida. Para cada combinacin de entrada binaria de 1s y 0s hay una y slo una, lnea de salida que adquiere el valor de 1. Este tipo de Decodificador se encuentra en muchas aplicaciones y es utilizado extensamente en el diseo de sistemas digitales. El consta de cuatro compuertas AND y dos Inversores. Un Decodificador tiene tantas salidas cuantas combinaciones de entradas

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 6

D.I.I.C.C Arquitectura de Sistemas Computacionales

binarias sean posibles. En este ejemplo particular, las dos entradas X e Y pueden estar en uno en los cuatro valores binarios posibles, como se muestra en la tabla de verdad. Observe que las variables de salida son mutuamente excluyentes y que slo una salida puede ser igual a 1 en cualquier instante. La salida cuyo valor es igual a 1 representa la combinacin del miniterm en las lneas de entrada. Un ejemplo de un Decodificador de 2 por 4 se muestra a continuacin.

Tabla de Verdad :

X 0 0 1 1 Y 0 1 0 1 D0 1 0 0 0 D1 0 1 0 0 D2 0 0 1 0 D3 0 0 0 1

De la tabla de verdad obtenemos las siguientes ecuaciones: D0 = XY; D1= XY ; D2= XY circuito lgico es: ; D3= XY , por lo tanto, el

Circuito lgico de un Decodificador de 2 por 4

Los Decodificadores de circuitos integrados pueden utilizar compuertas NAND o NOR en vez de compuertas AND. En este caso, las salidas son los complementos de los valores enumerados en la tabla de verdad. La combinacin del miniterm de las variables de entrada se distingue entonces por la salida cuyo valor es cero mientras todas las otras salidas son iguales a 1.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 7

D.I.I.C.C Arquitectura de Sistemas Computacionales

Es conveniente algunas veces incluir una entrada de habilitacin con un Decodificador para controlar la operacin del circuito. Por ejemplo, un Decodificador de 3 por 8 con una habilitacin se muestra a continuacin. Todas las salidas sern igual a 0 si la entrada habilitadora est en 0. Esto ocurre debido a que un 0 en la entrada de una compuerta AND produce un 0 en la salida, sin importar qu valores tengan las otras variables de entrada. Cuando la entrada habilitadora est en 1, el circuito opera como un Decodificador convencional. Para evitar dibujar el circuito lgico cada vez que se necesite un codificador (u otro circuito) podemos representarlo por medio de un diagrama de bloques simulando un circuito integrado. El tamao de un Decodificador en un CI (circuito integrado) depende usualmente del nmero de patas del chip. Por ejemplo, los Decodificadores de 2 por 4 pueden ser insertos en un chip de 14 patas. Un Decodificador de 3 por 8 con una entrada habilitadora puede insertarse en un chip de 14 patas (8 salidas, 3 entradas, 1 habilitadora y 2 patas para el suministro de energa). Es posible proporcionar tres entradas habilitadoras si el chip contiene 16 patas. El siguiente muestra el esquema Decodificador de 3 por 8 entradas del circuito lgico de un

Circuito lgico de un Decodificador de 3 por 8

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 8

D.I.I.C.C Arquitectura de Sistemas Computacionales

Nota: El circuito integrado 3and contiene el siguiente subcircuito y es utilizado para simplificar la implementacin, como se muestra a continuacin:

Por otro lado el Decodificador 3 por 8 se puede representar por el siguiente diagrama de bloques:

En resumen, un Decodificador 1 de 2n es un circuito combinacional con n lneas de entrada y 2n lneas de salida tal que, cada una de las 2n posibles combinaciones de entrada, activa una y slo una de las lneas de salida. Nota: En el circuito presentado no aparece la lnea habilitadora, pero tenga presente, que solo es una entrada extra a las compuertas AND, es decir, en vez de poseer tres entradas, poseern 4 siendo la ltima para la lnea habilitadora.

7.2.5

Demultiplexores

Un Decodificador con una o ms entradas habilitadoras puede funcionar como un Demultiplexor. Un Demultiplexor es una funcin digital que recibe informacin en una sola lnea y transmite esta informacin en una de 2n posibles lneas de salida. La lnea de salida que es seleccionada se determina de la combinacin de bits de las n lneas de seleccin. Un Decodificador (como el de 3 por 8 mostrado ac), funcionar como un Demultiplexor s la lnea habilitadora se toma como los datos de entrada y las entradas del Decodificador x, y, z, son tomadas como las lneas de seleccin. La sola variable de entrada (disponible en la lnea de

Capitulo 7.- Diseo de Circuitos Lgicos Pgina 9

D.I.I.C.C Arquitectura de Sistemas Computacionales

habilitacin) tiene una ruta a todas las ocho salida, pero la informacin de entrada es dirigida a solamente una de las lneas de salida como se especifica por la combinacin binaria de las tres lneas de seleccin. Por ejemplo, si las lneas de seleccin xyz = 000, la salida D0 ser la misma como la informacin de entrada en la lnea de habilitacin mientras que las otras salidas se mantendrn en 0. Debido a la simililitud de los Decodificadores y Demultiplexores, a estos circuitos se les conoce con el nombre de Decodificadores / Demultiplexores.

7.2.6

Multiplexores

La funcin de un Multiplexor es recibir informacin de una sola fuente y conducirla a 2n salidas bajo control de las lneas de seleccin. Un Multiplexor digital realiza la operacin inversa. Un Multiplexor es una funcin digital que recibe informacin binaria de 2n lneas y transmite informacin a una sola salida. La nica lnea de entrada que es seleccionada se determina a partir de la combinacin de bits de las n lneas seleccionadas. Un ejemplo de un Multiplexor de 4 por 1 se muestra a continuacin.

Los CI 3and corresponde a una compuerta AND con tres entradas

El diagrama de bloques correspondiente a un Multiplexor de 4 entradas por una salida es :

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 10

D.I.I.C.C Arquitectura de Sistemas Computacionales

Las cuatro lneas de entrada son aplicadas a cuatro compuertas AND cuyas salidas van a una sola compuerta OR. Solamente una lnea de entrada tiene S1 y S0 determinan cul de las entradas se selecciona para formar una ruta directa hacia la salida. As, con S1S0 =10, la compuerta AND asociada con la entrada I2 tiene dos de sus entradas iguales a 1. Si I2 =1 la salida de la compuerta es tambin igual a 1; si I2 =0, la salida es igual a 0. Todas las otras compuertas AND tienen una salida en 0. La salida de la compuerta OR ser igual al valor de la salida de la compuerta AND asociada con la salida I2 .Un Multiplexor tambin se le conoce con el nombre de Selector de Datos puesto que selecciona una de las mltiples lneas de entrada de datos y dirige la informacin binaria a la lnea de salida. La compuerta AND es un Multiplexor se parecen a un circuito Decodificador y en realidad, ellas descodifican las lneas de seleccin de entrada. En general, un circuito Multiplexor se construye a partir de un Decodificador n por 2n aadiendo una lnea de entrada a cada compuerta AND y aplicando todas las salidas de las compuertas AND a una sola compuerta OR. El tamao de un Multiplexor es especificado por el nmero de sus entradas, 2n. Esto entonces implica que l tambin contiene una lnea de salida y n de salidas de seleccin. Un Multiplexor puede tener una o ms lneas de habilitacin, como en un Decodificador. Las lneas de habilitacin pueden utilizarse para expandir dos o ms Multiplexores CI (circuito integrado) a un Multiplexor digital con un mayor nmero de entradas. En resumen, en el nivel de lgica digital, un Multiplexor es un circuito de 2 entradas de datos, una salida de datos y n entradas de control que seleccionan una de las entradas de datos. El dato de entrada seleccionado es el que aparece a la salida del circuito. Un Multiplexor a dems de poseer las entradas correspondientes, posee unas lneas seleccionadoras (o lneas de control ), que codifican un nmero de tantos bits como lneas de control existan, que especifica que lnea de las tantas de entrada, pasa a la salida del circuito. Independientemente de los valores de las lneas de control, slo una de las compuertas AND dar un valor igual a 0 1, segn sea el valor de la lnea de entrada que se seleccione y las restantes darn un valor igual a 0. Cada combinacin de las entradas de control permite el paso de informacin por una sola compuerta AND.

n

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 11

D.I.I.C.C Arquitectura de Sistemas Computacionales

7.3 Unidad aritmtica lgica

Como sabemos, la unidad encargada de sumar, multiplicar, comparar y realizar todas las operaciones Aritmticas y lgicas en el computador es la Unidad Aritmtica - Lgica. Para realizar todas las operaciones mencionadas, necesita de circuitos combinacionales lgicos que realicen cada operacin en particular, la mayora de estos circuitos han sido estudiado en sta seccin, por lo tanto, a modo de ejemplo se muestra un esquema general de la Unidad Aritmtica - Lgica y sus principales circuitos involucrados.

Circuito lgico de la UNIDAD ARITMTICA LGICA

Explicacin del circuito: La mayora de los computadores tienen un circuito nico para realizar, al menos, las operaciones AND, OR y suma de dos palabras de mquina. Uno de estos circuitos para procesar dos palabras de n bits suele construirse a partir de n circuitos idnticos, cada uno de los cuales procesa el par de bits de mismo peso de cada una de las palabras de entrada. La figura muestra a un ejemplo de Unidad Aritmtica y Lgica. Puede calcular una de las cuatro funciones siguientes: A AND B, A OR B, B o A + B, segn las lneas de seleccin de funcin, F0 y F1, contengan (en binario) 00, 01, 10 u 111, respectivamente.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 12

D.I.I.C.C Arquitectura de Sistemas Computacionales

La esquina inferior izquierda de nuestra UAL (Unidad Aritmtica Lgica) contiene un Decodificador de 2 bits que genera las lneas de permiso para las cuatro operaciones a partir de F0 y F1. La esquina superior izquierda tiene la lgica para calcular A AND B, A OR B y B , pero a lo sumo slo uno de estos resultados puede pasar a la compuerta OR final; lo cual depende de las lneas de permiso que vienen del Decodificador. Como slo una de las salidas del Decodificador estar a 1, slo se permitir el paso a travs de una de las compuertas AND que estn conectadas a la puerta OR; las tres restantes darn 0, independiente de A y B. La esquina inferior derecha tiene un sumador completo de un bit que calcula la suma de A y B, teniendo en cuenta los acarreos, ya que es probable que este circuito se use como una etapa para la realizacin de operaciones sobre palabras completas.

7.4 PRACTICANDO CON CIRCUITOS DIGITALES

El siguiente ejemplo representa un circuito de alarma de equilibrio. Este circuito accionar una alarma solo si la embarcacin pierde el equilibrio, es decir, si se ladea a la izquierda o a la derecha, en otro caso la alarma no sonar. El siguiente dibujo muestra esquemticamente los estados posibles de la embarcacin.

Tabla de verdad

POSICIN I C D 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 ALARMA ESTADO 0 1 0 0 1 0 0 0

Para esta tabla de verdad, no es necesario aplicar el mtodo de minimizacin del mapa de Karnaugh debido a que posee muy pocas variables. A continuacin se muestra la ecuacin obtenida directamente de esta tabla de verdad. ICD + ICD = C (ID+ID) = C (ID)

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 13

D.I.I.C.C Arquitectura de Sistemas Computacionales

Como podemos apreciar, se obtienen dos circuitos equivalentes para la misma operacin, pero uno de ellos utiliza menos compuertas lgicas en su implementacin. El siguiente circuito digital muestra los dos circuitos implementados. Circuito Digital El siguiente ejemplo muestra una entrada que representa que la embarcacin se desequilibr a la derecha, por lo tanto la alarma sonar. Note que ambos circuitos activan la alarma ya que son equivalentes entre s.

En el siguiente ejemplo se supone que en una casa existen tres tipos de alarmas, dependiendo de cual de ellas se active marcar un determinado telfono. En este ejemplo se utilizarn las siguientes variables para representar las alarmas, L = Luz, C = Calor, S = sonido. Si se activa la alarma de Luz se deber discar el telfono de la polica, si se activa la alarma de Calor se llamar a los bomberos, y finalmente si se activa la alarma de Sonido se llamar a la Unidad de Rescate. Por otro lado, se tendrn en cuenta las siguientes condiciones especiales: CS, LC LS LCS Bomberos Polica Polica - Bomberos - Rescate

A continuacin se muestra la tabla de verdad correspondiente a este ejemplo:

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 14

D.I.I.C.C Arquitectura de Sistemas Computacionales

ALARMA L C D 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 LLAMADA B R 0 0 0 1 1 0 1 0 0 0 0 0 1 0 1 1

P 0 0 0 0 1 1 0 1

Ntese que en este caso no se utiliza el mapa de Karnaugh debido a la simplicidad de las variables. Por lo tanto, de la tabla de verdad podemos obtener directamente las siguientes ecuaciones: 1).2).3).Para la alarma de Polica se tiene la LCS+LCS+LCS = L(C+CS)= L(C+S) siguiente frmula:

Para la alarma de Bomberos se tiene la siguiente frmula: LCS+LCS+LCS+LCS =C Para la alarma de la Unidad de Rescate se tiene la siguiente frmula LCS+LCS = S(LC+ LC)= S(L C)

A continuacin se muestra el circuito digital correspondiente al ejemplo de las alarmas mltiples: Circuito Digital El siguiente circuito muestra a modo de ejemplo la condicin de que se activ tanto la alarma de Luz como de Calor, por definicin del problema como resultado del circuito, se debera llamar a los bomberos.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 15

D.I.I.C.C Arquitectura de Sistemas Computacionales

El siguiente ejemplo simula un tablero de auto que posee los siguientes indicadores: una letra L para indicar luz, una letra A para indicar Aceite y finalmente una letra G para indicar gasolina. Estas letras se activarn en un display atendiendo de las siguientes condiciones:

Condiciones para letra L: Puertas abiertas Ampolletas en mal estado Corto circuito

Condiciones para letra A: Aumento de temperatura Aumento de consumo agua Disminucin de nivel aceite de de

Condiciones para letra G: Disminucin gasolina nivel de

Antes de definir la tabla de verdad diremos que para representar las letras L , A, G deben estar prendidos los siguientes segmentos:

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 16

D.I.I.C.C Arquitectura de Sistemas Computacionales

A partir de estas condiciones, podemos generar la siguiente tabla de verdad:

Condicin ---------Puertas abiertas Ampolletas malas Corto circuito temperatura Consumo de agua Nivel de aceite Nivel de gasolina

Variables x y z 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

g 0 0 0 0 1 1 1 1

f 0 1 1 1 1 1 1 1

Display e d c b 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 0 1 1 1 0 1 1 1 0 1 1 1 1 1 0

a 0 0 0 0 1 1 1 1

Mapa de karnaugh Ecuaciones obtenidas para G, F ,E:

g= X

f = XZ + ( X Y ) + XY

e = XZ + ( X Y ) + XY

Ecuaciones obtenidas para D, C, B, A:

c= X

b = X (Z + Y )

a=X

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 17

D.I.I.C.C Arquitectura de Sistemas Computacionales

sigue:

En resumen las ecuaciones

obtenidas las podemos agrupar como

a,c,g=x; d= X ( Z + Y ) + YZ ; f,e= XZ + ( X Y ) + XY ; b= X ( Z + Y ) A partir de estas ecuaciones se obtiene el siguiente circuito:

Circuito Digital En el siguiente circuito se muestra como ejemplo la condicin (100) que significa segn la tabla de verdad a la condicin, Aumento de temperatura, por lo tanto, el tablero del auto est marcando la letra A correspondiente a la seal de Aceite.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 18

D.I.I.C.C Arquitectura de Sistemas Computacionales

7.5

Introduccin a los flip -flop

DEFINICIONES: Un circuito se dice combinacional cuando su salida depende de las entradas en el restante considerado no importando el valor que haya tomado anteriormente. En general es posible realizar una funcin Booleana mediante combinacin de las diferentes compuertas existentes. En cambio, un circuito secuencial no slo depende de las entradas en el instante considerado sino que adems, de la evolucin anterior de ste. Para este caso se utilizan los Flip -Flop. Hay dos tipos de circuitos secuenciales y su clasificacin depende de las seales de tiempo. Un circuito secuencial sincrnico emplea elementos de almacenamiento denominados flip-flops que se permiten que cambien sus valores binarios solamente en instantes discretos de tiempo. Un circuito secuencial asincrnico es un sistema cuyas salidas dependen del orden en el cual sus variables de entrada cambian y puede afectarse en cualquier instante de tiempo. Los sistemas asincrnicos del tipo compuerta son bsicamente circuitos de combinacin con rutas de realimentacin. Debido a la realimentacin entre las compuertas lgicas el sistema puede, algunas veces, volverse inestable. Los problemas de inestabilidad encontrados en sistemas asincrnicos imponen muchas dificultades y por esta razn, rara vez son utilizados en el diseo de sistemas de computadores digitales. Los sistemas de lgica secuencial sincrnica utilizan compuertas lgica y dispositivos de almacenamiento con flip-flops. La sincronizacin se logra por un dispositivo de tiempo denominado un generador de pulsos de reloj. Los pulsos de reloj de generador son distribuidos a travs del sistema de tal manera que los flip-flops son afectados solamente con la llegada del pulso de sincronizacin. Los circuitos secuenciales sincrnicos de reloj no manifiestan problemas de inestabilidad y su sincronizacin de tiempo se puede desdoblar fcilmente en pasos independientes discretos, cada uno de los cuales puede considerarse separadamente. Los circuitos secuenciales discutidos en este libro son exclusivamente del tipo sincrnico con reloj. Un flip-flops es una celda binaria capaz de almacenar un bit de informacin. Tiene dos salidas, una para el valor normal y otra para el valor complementado del bit almacenado en l. Un flip-flops mantiene un estado binario hasta que sea dirigido por un flops est en el nmero de entradas que posan y en la manera en la cual las entradas afectan el estado binario. Los tipos ms comunes de flip-flops se discuten a continuacin.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 19

D.I.I.C.C Arquitectura de Sistemas Computacionales

7.5.1

Flip-flop bsico o de pestillo

Un flip-flop asincrnico se construye a partir de dos compuertas NAND y dos compuertas NOR conectadas frente a frente. EL circuito para la versin NAND se muestra en la Figura. Las conexiones cruzadas de la salida de una compuerta con la entrada de la otra constituyen el camino de realimentacin. Por esta razn, el circuito se clasifica como asincrnico. Cada flip-flop tiene dos salidas, Q y Q, y dos entradas, set y reset. Este tipo de flip-flop es denominado un flip-flop RS directamente acoplado, la R y la S son las primeras letras de los nombres de las dos entradas. Otro nombre ms popular para este tipo de flip-flop es un pestillo. El pestillo forma un circuito bsico a partir del cual pueden construirse tipos ms complicados de flip-flop.

Flip-flop bsico (pestillo)

El pestillo NAND opera con ambas entradas normales en 1, a no ser que el estado del circuito tenga que cambiarse. La aplicacin de un 0 momentneo a la entrada set hace que la salida Q se coloque en 1 y Q en 0. Las salidas del circuito no cambian cuando la entrada set regresa a 1. Un 0 momentneamente aplicado a la entrada reset coloca la salida Q = 0 y Q = 1. El estado de flip-flop es siempre tomado del valor de su salida normal Q. Cuando Q = 1, decimos que el flip-flop almacena un 1 y est en el estado set. Cuando Q = 0, decimos que el flip-flop almacena un 0 y est en el estado aclarado. El circuito pestillo manifiesta una condicin indeseable si ambas entradas se colocan en 0 simultneamente. La investigacin del circuito mostrar que cuando ambas entradas son 0, las salidas Q y Q se colocan en 1, una condicin que no tiene normalmente ningn significado en la operacin de un flip-flop. Si ambas entradas regresan a 1, el estado del flipflop no es predecible; cualquier estado puede resultar, dependiendo de cul entrada permanezca en el estado 0 por el mayor perodo de tiempo antes de la transicin a 1.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 20

D.I.I.C.C Arquitectura de Sistemas Computacionales

7.5.2

Flip-flop RS

Aadiendo compuertas a las entradas del pestillo, el flip-flop puede hacer que responda solamente durante la ocurrencia de un pulso de reloj: El flip-flop RS con reloj, que se muestra en la Figura, consiste en un pestillo bsico y dos compuertas adicionales NAND. Las salidas de compuerta 3 y 4 permanecen en 1 siempre y cuando el pulso de reloj (abreviado CP) est en 0, independiente de los valores de las entradas R y S. Cuando el pulso de reloj va a 1, la informacin de las entradas S y R se permite que alcance el pestillo en las compuertas 1 y 2. El estado de set se alcanza con S = 1, R = 0 y CP = 1. Para cambiar al estado aclarado, las entradas deben ser S = 0, R = 1, y CP = 1. Con S = 0 y R = 0, un CP de 1 no afecta el estado del flipflop. S y R no pueden ser 1 durante la ocurrencia de un pulso de reloj debido a que el estado siguiente del flip-flop es indeterminado.

Diagrama lgico de un flip-flop RS con reloj

El smbolo grfico o diagrama de bloques del flip-flop que se muestra en la Figura, tiene tres entradas: S, R, y CP. La entrada CP se marca con un pequeo tringulo. El tringulo es un smbolo para un indicador dinmico y denota el hecho de que el circuito responde a una entrada de transicin de 0 a 1. A las salidas del flip-flop se les da un nombre variable tal como Q o cualquier otra designacin con una letra conveniente. El pequeo tringulo rectngulo es un smbolo grfico para un indicador de polaridad. El designa la salida complementada del flip-flop la cual es en este caso Q.

Diagrama de Bloques Flip-flop RS

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 21

D.I.I.C.C Arquitectura de Sistemas Computacionales

Tabla de Verdad

S 0 0 1 1 R 0 1 0 1 Q( t+1 ) Q( t ) 0 1 ? COMENTARIO No Cambias Aclarar Set No Permitido

La tabla caracterstica mostrada, resume la operacin del flip-flop RS en forma tabular. Q(t) es el estado binario del flip-flop en un instante dado de tiempo (conocido como el estado presente). Las columnas S y R dan los valores binarios de las entradas. Q(t+1) es el estado del flip-flop despus que ha ocurrido un pulso de reloj (conocido el estado siguiente). Si S=R=0, un pulso no produce cambio de estado, esto es Q(t+1)=Q(t). Si S=0 y R=1, el flip-flop llega al estado 0 (el estado aclarado). Si S=1 y R=0 el flip-flop llega al estado 1 (el estado set). Un flip-flop RS no debe ser pulsado cuando S=R=1 puesto que produce un estado siguiente indeterminado.

7.5.3

El flip-flop D

El flip-flop D (dato) es una modificacin ligera del flip-flop RS. Un flipflop RS se convierte a un flip-flop D insertando un inversor entre S y R y asignndole el smbolo D a la entrada S. La entrada D es muestreada durante la ocurrencia de un pulso de reloj y si este es 1, el flip-flop alcanza el estado 1 (debido a que S=1 y R=0). Si l es 0, el pulso cambia el estado del flip-flop a 0 (debido a que S=0 y R=1). El smbolo grfico y la tabla caracterstica del flip-flop D se muestran en la siguiente Figura. Note que no existe condicin de entrada que deje el estado del flip-flop sin cambiar. Aunque un flip-flop D tiene la ventaja de tener solamente una entrada (excluyendo CP), tiene la desventaja de que su tabla caracterstica no tiene una condicin de no cambio Q(t+1)=Q(t). El no cambio puede lograrse bien rehabilitando los pulsos de reloj con una compuerta externa AND o alimentando la entrada de nuevo hacia la salida de tal manera que los pulsos del reloj mantengan el estado del flip-flop sin modificar.

Flip-flop D

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 22

D.I.I.C.C Arquitectura de Sistemas Computacionales

Tabla de Verdad

D 0 1 Q ( t+1 ) 0 1 COMENTARIO Aclarar Set

7.5.4

El flip - flop Jk y T

Un flip-flop JK es un refinamiento de un flip-flop RS en que la condicin intermedia del tipo RS est definida en el tipo JK. Las entradas J y K se comportan como un conjunto de entradas S y R para hacer el set y el aclaramiento del flip-flop respectivamente. Cuando las entradas J y K son ambas iguales a 1, un pulso de reloj conmuta las salidas del flip-flop a su estado complementario, Q(t+1)=Q(t). El smbolo grfico y tabla caracterstica del flip-flop JK se muestran en la Figura. Note que la entrada J es equivalente a la condicin set mientras que la entrada K produce la condicin de aclaramiento. Adems hay condiciones de no cambio y complementarias en este tipo de flip-flop.

Flip-flop JK

Tabla de Verdad

J 0 0 1 1 K 0 1 0 1 Q ( t+1 ) Q( t+1 ) 0 1 Q ( t ) COMENTARIO No Cambia Aclarar Set Complemento

Flip-flop T

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 23

D.I.I.C.C Arquitectura de Sistemas Computacionales

Tabla de Verdad

T 0 1 Q ( t+1 ) Q(t) Q ( t ) COMENTARIO No Cambia Complemento

Otro tipo de flip-flop que se encuentra en los libros de texto es el flipflop T (toggle). Este flip-flop, mostrado en la Figura, se obtiene de un tipo JK cuando las entradas J y K se amarran juntas. El flip-flop T, por consiguiente, tiene solamente dos condiciones. Cuando T=0 (J=K=0) un pulso de reloj no cambia el estado de flip-flop. Cuando T=1 (J=K=1) un pulso de reloj complementa el estado del flip-flop. Tabla de Excitacin Las tablas caractersticas de flip-flops especifican el estado cuando las entradas y el estado presente se conocen. Durante el proceso de diseo conocemos normalmente la transicin requerida del estado presente al estado siguiente y deseamos encontrar las condiciones de entrada del flipflop que harn la transicin requerida. Por esta razn necesitamos una tabla que liste las combinaciones de entrada requerida para un cambio dado de estado. Una tabla como esta se denomina una tabla de excitacin del flipflop. La Tabla Resumen, lista las tablas de excitacin para los cuatro tipos de flip-flops. Cada una de las tablas consta de dos columnas, Q(t) y Q(t+1), y una columna para cada una de las entradas para mostrar como se logra la transicin requerida. Hay cuatro transiciones posibles de un estado presente Q(t) a un estado siguiente Q(t+1). Las condiciones de entrada requeridas para cada una de estas transiciones se derivan de la informacin disponible en las tablas caractersticas. El smbolo X en las tablas representa condiciones que no importan; esto es, no importa si la entrada del flip-flop es 0 1. Tablas de excitacin para los cuatro tipos de flip-flops

Q(t) 0 0 1 1 Q(t+1) 0 1 0 1 S 0 1 0 X R X 0 1 0 Q(t) 0 0 1 1 Q(t+1) 0 1 0 1 J 0 1 X X K X X 1 0

(a) Flip-Flop RS

(b) Flip-Flop JK

Q(t) 0 0 1 1

Q(t+1) 0 1 0 1

D 0 1 0 1

Q(t) 0 0 1 1

Q(t+1) 0 1 0 1

T 0 1 1 0

(c ) Flip-flop D

Capitulo 7.- Diseo de Circuitos Lgicos

(d) Flip-Flop T

Pgina 24

D.I.I.C.C Arquitectura de Sistemas Computacionales

Tabla resumen de Flip -Flop

La razn para las condiciones que no importan en las tablas de excitacin es que hay dos maneras de lograr la transicin requerida. Por ejemplo, en un flip-flop RS, una transicin del estado presente de 0 a un estado siguiente de 0 puede lograrse teniendo las entradas S y R iguales a 0 (para que no ocurra cambio cuando se aplica el pulso de reloj), o haciendo S=0 y R=1 para aclarar el flip-flop (aunque ya est aclarado). En ambos casos S debe ser 0, pero R es 0 en el primer caso y 1 en el segundo. Puesto que la transicin requerida ocurrir en cualquier caso, marcamos la entrada R con una X y dejamos al diseador para que escoja o 0 o 1 para la entrada R, la que para l sea ms conveniente.

7.6 Ejemplos prcticos utilizando flip -flop:

7.6.1

RESTADOR UTILIZANDO SUMADORES

La Unidad Aritmtica Lgica (UAL) realiza otras operaciones aritmticas, tales como la multiplicacin y divisin por nmeros distintos de 2, suma de cdigos decimales y resta. La resta puede ser realizada utilizando un circuito restador, en la misma forma en que se utilizaba un circuito sumador. De todas formas, para limitar el nmero de circuitos diferentes, la resta en los computadores se realiza mediante el circuito sumador. Para hacer esto, es necesario cambiar algunos de los nmeros binarios a nmeros codificados en Complemento A2. Como se mostrar en la siguiente figura, ntese que las entradas de los bits B estn negados por un inversor, invirtiendo las entradas antes que entren en el sumador y aplicando un arrastre de entrada (Cin), el sumador efectuar la operacin resta en vez de sumar. Para aclarar el concepto, utilizaremos como ejemplo efectuar la siguiente operacin aritmtica: A - B, donde A=12 y B=6.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 25

D.I.I.C.C Arquitectura de Sistemas Computacionales

Observemos que enviando el nmero B a travs de los inversores del circuito, los bit a sumar son 1001, en vez de 0110 (el equivalente decimal de 6). Este es el complemento o Complemento A1 de 0110. Sumando 1001 al nmero A, 1100 (equivalente binario del nmero decimal 12), con un arrastre de entrada 1, se obtiene el resultado 0110. As mediante la suma obtenemos la resta deseada (12 - 6 = 6). El arrastre sumado proporciona el complemento A2 del nmero B. Con este procedimiento se ahorra superficie en el circuito integrado, porque los circuitos del sumador se utilizan para ms de una funcin. A continuacin se realizar el desarrollo matemtico de la operacin resta: Sea A= 1210 B = 6 10 = 11002 = 01102

Calculemos el Complemento A1 de B A1 de B = 1001 Efectuemos la suma A+ A1 de B, y finalmente el Complemento A2 producido por el acarreo.

en binario).

Por lo tanto : El circuito Sumador a restado 12 - 6 = 6 (0110

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 26

D.I.I.C.C Arquitectura de Sistemas Computacionales

Diagrama de Bloques del Circuito Lgico:

Para comprender mejor el funcionamiento de las operaciones aritmticas bsicas, hemos utilizado slo nmeros de 4 bits. A continuacin se muestra el diagrama de bloques del circuito que se comporta como Sumador / Restador. 7.6.2 MULTIPLICADORES Y DIVISORES (Desplazadores):

Para realizar la multiplicacin y la divisin se necesitan registros con capacidad de desplazamiento de nmeros a derecha e izquierda. Otras operaciones aritmticas necesarias en los Pc son la multiplicacin y la divisin de un nmero por 2. Para realizar estas operaciones se necesitan circuitos de control y / o registros que puedan desplazar un nmero binario una posicin a la derecha (Divisin por 2) o una posicin hacia la izquierda (Multiplicacin por 2). Una forma en que esto pueda hacerse es dando salida a los datos del registro y hacindolos volver a ste en la posicin desplazada. La siguiente figura muestra un circuito que permite hacer desplazamientos a la derecha o la izquierda. Para realizar el desplazamiento a la izquierda, se coloca un 1 en la lnea de Desplazamiento Izquierda y se enva la salida de un determinado Flip-Flop a la entrada del Flip - Flop situado inmediatamente a su izquierda a travs de las puertas de Retencin. La seal de Desplazamiento Izquierda es sincronizada por el reloj. El Flip - Flop de arrastre de salida guarda el Bit ms significativo presente antes del desplazamiento, puede necesitarse para las operaciones siguientes. Un desplazamiento a la derecha se realiza enviando una seal 1 por la lnea de Desplazamiento Derecha, en vez de por la de Desplazamiento Izquierda, a lo que provoca que cada Flip -Flop enve su contenido situado inmediatamente a su derecha, a travs de las puertas de retencin. Por ejemplo, si el nmero almacenado en el registro es 0110 ( equivalente al 6 decimal) antes del desplazamiento a la izquierda, el nmero almacenado despus de la operacin de desplazamiento es 1100 ( equivalente al nmero 12 decimal). El desplazamiento a la izquierda ha multiplicado el nmero por 2. Si el 1100 es desplazado a la derecha, se convierte en 0110; significa que el nmero 12 ha sido dividido por 2. A

Capitulo 7.- Diseo de Circuitos Lgicos Pgina 27

D.I.I.C.C Arquitectura de Sistemas Computacionales

modo de ejemplo, se desarrollar las operaciones de multiplicacin y divisin aprovechando el desplazamiento de bit a la izquierda o derecha. Se desea ejecutar la siguiente operacin matemtica 6*2 = 12:

El equivalente del nmero 6 decimal a binario es 0110, veamos en forma grfica el desplazamiento a la izquierda para generar el resultado 1100 equivalente a 12 en decimal:

Multiplicacin: Sea el nmero decimal 6 igual 0110 binario, ste nmero se ha representado en un arreglo de 8 bit, los 4 bit segmentados llenos de ceros, servirn para efectuar el desplazamiento. Como se trata de una multiplicacin el desplazamiento se realizar en un bit a la izquierda a partir del dgito ms significativo (1). La siguiente figura el desplazamiento a la izquierda.

Despus del desplazamiento a la izquierda se obtiene el nmero binario 1100 equivalente al nmero 12 decimal. Por lo tanto, se ha multiplicado por 2.

Divisin En forma anloga al ejemplo anterior, se representa el nmero a dividir (4 2) en un arreglo, pero con la diferencia que las posiciones de los bit segmentados aparecen a la izquierda, puesto que se realizar un desplazamiento a la derecha:.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 28

D.I.I.C.C Arquitectura de Sistemas Computacionales

Despus del desplazamiento a la derecha, se obtiene el nmero binario 0010 equivalente al nmero 2 decimal. Por lo tanto, se ha dividido por 2.

La siguiente figura muestra el diagrama de bloques que representa a un Multiplicador / Divisor de 4 bit.

Nota: La seal de Izquierda - Derecha controla las puertas de retencin Nmero antes del desplazamiento en un registro de 4 bits 0110 (6) Nmero despus del desplazamiento en un registro de 4 Bits 1100 (12).

7.6.3

MEMORIA RAM DE CIRCUITOS INTEGRADOS.

Las memorias de circuitos integrados algunas veces tienen una sola lnea para el control leer/escribir. Un estado binario, digamos 1, especifica una operacin leer y el otro estado binario especifica una operacin escribir. Adems, se pueden incluir o ms lneas de habilitacin en cada uno de los paquetes del circuito integrado para proporcionar medios para expandir varios paquetes en una unidad de memoria con un gran nmero de palabras. La construccin interna de una memoria de acceso aleatorio de m palabras con n bits por palabra consta de m * n celdas de almacenamiento binario y lgica necesaria para seleccionar una palabra para escribir o leer. La celda de almacenamiento binario es el bloque de construccin bsico de una unidad de memoria. El diagrama lgico de una celda binaria que almacena un bit de informacin se muestra a continuacin. Aunque la celda se muestra que incluye cinco compuertas y

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 29

D.I.I.C.C Arquitectura de Sistemas Computacionales

un flip-flop, internamente es construida con 2 flip-flop de transistores que tienen entradas mltiples. La celda binaria de una unidad de memoria debe ser muy pequea para ser capaz de empacar tantas celdas como sea posible en el rea del semiconductor disponible en la pastilla. La celda binaria se muestra que tiene tres lneas de entrada y una lnea de salida.

Diagrama Lgico

Diagrama de bloque BC Celda Binaria

Este circuito es equivalente al recin mencionado, para efectos de simplicidad del circuito se ha utilizado ste ltimo en vez del anterior.

El propsito de la entrada select es seleccionar una celda de las muchas disponibles. Con la lnea select en 1, un 1 en el terminal

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 30

D.I.I.C.C Arquitectura de Sistemas Computacionales

leer/escribir conforma una ruta de la salida del flip-flop al terminal de salida. Con el terminal leer/escribir en 0, el bit en la lnea de entrada se transfiere al flip-flop. Con la entrada como la salida son deshabilitadas cuando la lnea select es 0. Note que el flip-flop opera sin pulso de reloj y que su propsito es almacenar el bit de informacin en la celda binaria. La configuracin de una RAM de 4 por 3 se muestra en la figura que sigue. Contiene cuatro palabras de tres bits cada una para un total de 12 celdas de almacenamiento. Cada caja pequea rotulada BC en el diagrama contiene el circuito de una celda binaria. Las cuatro lneas que se ven en cada caja BC designan los tres terminales de entrada y un terminal de salida como se especific en el diagrama anterior. Circuito lgico de una Memoria RAM de 4 por 3.

Las dos lneas de direccin van a un Decodificador 2 por 4 con una entrada de habilitacin. Cuando la habilitacin de memoria es 0, todas las salidas del Decodificador son 0 y ninguna de las palabras de la memoria se seleccionan. Con la entrada habilitada de memoria en 1, una de las cuatro palabras es seleccionada, dependiendo de la combinacin del bit de las dos lneas de direccin. Ahora, con el control leer/escribir en 1, los bits de la palabra seleccionada van a tres compuertas OR y a los terminales de

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 31

D.I.I.C.C Arquitectura de Sistemas Computacionales

salida. Las celdas binarias no seleccionadas producen 0's en las entradas del OR y no tienen efecto en las salidas. Con el control leer/escribir en 0, la informacin disponible en las lneas de entrada se transfiere a los flip-flop de la palabra seleccionada. Las celdas binarias no seleccionadas en las otras palabras son deshabilitadas por la lnea de seleccin de tal manera que los valores previos permanecen inmodificados. As, con la habilitacin de la memoria en 1, el control leer/escribir inicia las operaciones leer y escribir para la unidad de memoria. Una operacin de inhibicin se obtiene manteniendo la habilitacin de memoria en 0. Esta condicin deja los contenidos de todas las palabras en la memoria como eran, independiente del valor del control leer/escribir.

7.6.4

MEMORIAS DE SOLO LECTURA (ROM).

Una memoria de solo lectura (ROM), como su nombre lo indica, es una unidad de memoria que realiza solamente la operacin de lectura: no tiene la capacidad de escribir. Esto implica que la informacin binaria almacenada en una ROM se realiza permanentemente durante la produccin del hardware de la unidad y no puede ser alterada escribiendo palabras diferentes en ella. Mientras que una RAM es un dispositivo de propsito general cuyos contenidos pueden alterarse durante el proceso de cmputo, una ROM est restringida a la lectura de palabras que son permanentemente almacenadas dentro de la unidad. Una ROM m por n es un arreglo de celdas binarias organizadas en m palabras de n bits cada una. Como se muestra en el diagrama de bloques de la figura siguiente, una ROM tiene k lneas de direccin para seleccionar una de 2k =m palabras de memoria, y n lneas de salida, una para cada uno de los bits de la palabra.

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 32

D.I.I.C.C Arquitectura de Sistemas Computacionales

La ROM no necesita una lnea de control leer puesto que en un instante dado, las lneas de salida automticamente proporciona los 1's y 0's de los n bits de la palabra selecciona por el valor de la direccin. Debido a que las salidas son una funcin solamente de las entradas presentes (las lneas de direccin) una ROM es clasificada como un circuito de combinacin. En realidad, una ROM se construye internamente con Decodificadores y un conjunto de compuertas OR. No hay necesidad de proporcionar condiciones de almacenamiento como en el RAM, puesto que los valores de los bits en la ROM se mantienen fijos permanentes. Considere el diagrama lgico siguiente de una ROM 4 por 3. La unidad contiene un Decodificador de 2 por 4 para decodificar las dos lneas de direccin. Las compuertas OR proporcionan tres salidas. Si cada uno de los minterms de salida del Decodificador es conectado a la entrada de cada uno de las compuertas OR, las salidas del circuito estarn en 1 no importa cual sea la palabra seleccionada por las lneas de direccin. Supongamos que deseamos que la ROM contenga las combinaciones de bits que se numeran en la tabla de verdad que acompaa al diagrama. La tabla de verdad especifica una combinacin de bit de 010 para la palabra 0. Esta combinacin de bits se obtiene rompiendo dos alambres (marcados con una cruz) entre la palabra 0 y las entradas que estn ms a la izquierda de las compuertas OR. En otras palabras, cuando la lnea de direccin de entrada es 00, la salida D del Decodificador es igual a 1 y todas las otras salidas del Decodificador son iguales a 0. Solamente la compuerta OR asociada con la salida A2 recibe una entrada de 1 debido a que los otros dos alambres estn rotos. Por consiguiente, las lneas de salida proporcionan una salida A1A2A3=010 (suponiendo que un alambre abierto de la compuerta OR se comporta como una entrada 0). Similarmente, todos los otros alambres marcados con cruces indican alambres rotos y cuando estos alambres se retiran del diagrama, el diagrama lgico as obtenido implementar la tabla de verdad que se enumeran para la ROM.

Circuito ROM de 4 por 3

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 33

D.I.I.C.C Arquitectura de Sistemas Computacionales

Tabla de Verdad:

X 0 0 1 1 Direccin Y 0 1 0 1 A1 0 0 1 1 Salidas A2 A3 1 0 0 1 0 1 1 0

Una ROM CI se fabrica primero con todas las salidas en 1 (o todas en 0, dependiendo del CI particular). El patrn particular de 1's y 0's se obtiene proporcionando una mscara en el ltimo paso de fabricacin. Cada una de las celdas en una ROM incorpora un enlace (en la posicin de la cruz en diagrama) que puede fusionarse durante el ltimo proceso de fabricacin. Un enlace roto en una celda define un estado binario y un enlace no roto representa el otro estado. El procedimiento involucrado en la fabricacin de ROMs requiere que el cliente llene la tabla de verdad que l desea que satisfaga la ROM. El fabricante entonces hace la mscara correspondiente para los enlaces para que se produzcan los 1's y 0's de cada palabra deseada. Este procedimiento es denominado una programacin al cliente o una programacin de mscara. Es un procedimiento de hardware aunque se utilice aqu la palabra programacin. Para pequeas cantidades es ms conveniente utilizar la ROM programable, conocido como una PROM. Cuando se ordena, las PROMs contienen todos 0's (o todos 1's) en cada palabra. Cada una de las celdas de una PROM incorpora un enlace que puede fundirse por aplicacin de un pulso de corriente elevada. Un enlace roto en una celda define un estado binario y uno que no est roto representa el otro

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 34

D.I.I.C.C Arquitectura de Sistemas Computacionales

estado. El procedimiento usualmente es irreversible y, una vez fundido, la salida para aquel bit es permanente. Esto permite al usuario programar la unidad en su propio laboratorio rompiendo los enlaces que deben ser abiertos para lograr las relaciones deseadas entre las direcciones de entrada y los datos de salida. Tambin se encuentra disponibles las PROMs borrables. Estas ROMs tienen un procedimiento especial para restaurar los enlaces a su valor inicial (todos 0's o todos 1's) aunque ellos hayan sido programados previamente. En cualquier caso, todos los procedimientos para programar o borrar ROMs son procedimientos de hardware. Las aplicaciones digitales que utilizan ROMs especifican un patrn de palabra fija. El aspecto de programacin de la ROM tiene que ver con los procedimientos para obtener el patrn fijo deseado. Las ROMs son ampliamente utilizadas para convertir un cdigo binario a otro, para tablas que se necesitan en funciones matemticas, para la exhibicin de caracteres, y muchas otras aplicaciones que requieren un gran nmero de entradas y salidas. Tambin se emplean en el diseo de unidades de control para computadores digitales. En este aspecto se usan para almacenar informacin codificada que representa la secuencia de variables de control internas necesarias para habilitar las diversas operaciones en el computador. Una unidad de control que utilizan una ROM para almacenar informacin de control binario es denominada una unidad de control microprogramada. El siguiente ejemplo muestra un contador digital de 2 bit. Este sumador podr sumar desde 00 hasta el nmero 99 decimal. Este circuito ha sido implementado utilizando 4 Flip - Flop JK, ms una compuerta AND. Para efectos de simplicidad del circuito, se ha utilizado un CI llamado bcdcnt (Contador BCD). El siguiente esquema muestra el circuito lgico del contador:

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 35

D.I.I.C.C Arquitectura de Sistemas Computacionales

Circuito Integrado utilizado:

Subcircuito del CI bcdcnt:

Capitulo 7.- Diseo de Circuitos Lgicos

Pgina 36

También podría gustarte

- Circuitos Logicos Flip-FlopDocumento47 páginasCircuitos Logicos Flip-FlopFreddy's Beltran OficialFb100% (1)

- TAREA CAPÍTULO 6 - Aritmética Digital - Operaciones y CircuitosDocumento3 páginasTAREA CAPÍTULO 6 - Aritmética Digital - Operaciones y CircuitosXleyendaXAún no hay calificaciones

- 6 Circuitos Combinacionales P ImprimirDocumento36 páginas6 Circuitos Combinacionales P ImprimirFabian AcostaAún no hay calificaciones

- ED Practica - 6 Decodificador BCDDocumento2 páginasED Practica - 6 Decodificador BCDCarlos DeleiverAún no hay calificaciones

- Naturales y Enteros EJERCICIOS RESUELTOSDocumento8 páginasNaturales y Enteros EJERCICIOS RESUELTOSAbraham Nelson100% (3)

- Unidad 2 Lenguaje EnsambladorDocumento12 páginasUnidad 2 Lenguaje EnsambladorJose Gpe TGAún no hay calificaciones

- Ensayo Sistemas DigitalesDocumento15 páginasEnsayo Sistemas DigitalesDilan Jimenez II100% (1)

- Math Type GUIADocumento12 páginasMath Type GUIAJose Vilchez ChumoAún no hay calificaciones

- Guia Cursos Anuales - Algebra 2009Documento264 páginasGuia Cursos Anuales - Algebra 2009hectorAún no hay calificaciones

- 10.6.1 Creación de Una Pequeña Topología de LaboratorioDocumento15 páginas10.6.1 Creación de Una Pequeña Topología de Laboratorioalejoney100% (2)

- VHDLDocumento34 páginasVHDLAnel VallarinoAún no hay calificaciones

- Como Utilizar El Cd4017Documento3 páginasComo Utilizar El Cd4017Mario Jiménez100% (1)

- Informe Programas Con With SelectDocumento13 páginasInforme Programas Con With SelectKathleen LeblancAún no hay calificaciones

- Señal Síncrona y AsíncronaDocumento6 páginasSeñal Síncrona y AsíncronaVictor Alejandro Balam MatosAún no hay calificaciones

- Lección #06 Diseño de Contadores SincronosDocumento8 páginasLección #06 Diseño de Contadores SincronosAnghel CarreroAún no hay calificaciones

- Interconexión de CiDocumento3 páginasInterconexión de CiJessi laraAún no hay calificaciones

- Analisis Entrada Salida de Sistemas en El TiempoDocumento6 páginasAnalisis Entrada Salida de Sistemas en El TiempoSebastián Muñoz AndradeAún no hay calificaciones

- Arboles ImportanciaDocumento33 páginasArboles ImportanciagabrielaAún no hay calificaciones

- Especificación ComplementariaDocumento3 páginasEspecificación Complementariam_valderasAún no hay calificaciones

- Primer Parcial Liderazgo y DesempeñoDocumento5 páginasPrimer Parcial Liderazgo y DesempeñoReyes OrtegaAún no hay calificaciones

- Normalizacion RedesDocumento3 páginasNormalizacion RedesadealbAún no hay calificaciones

- 1.1 Diagramas de VennDocumento4 páginas1.1 Diagramas de VennDickie GreenleafAún no hay calificaciones

- TareaDocumento15 páginasTareaNova Issei GremoryAún no hay calificaciones

- 74LS76 TTL Flip Flop J KDocumento1 página74LS76 TTL Flip Flop J KemersonAún no hay calificaciones

- Como Utilizar El I C cd4017Documento3 páginasComo Utilizar El I C cd4017Jose RuizAún no hay calificaciones

- Complementos A1, A2 y Signo-MagnitudDocumento5 páginasComplementos A1, A2 y Signo-MagnitudhyperkrizAún no hay calificaciones

- Paso 6 - Proyecto Final IVAN FELIPE SARMIENTO GARCIA Sistemas EmbebidosDocumento23 páginasPaso 6 - Proyecto Final IVAN FELIPE SARMIENTO GARCIA Sistemas EmbebidosKATHEAún no hay calificaciones

- Circuitos MSIDocumento81 páginasCircuitos MSIrxaviervaAún no hay calificaciones

- Generalidades ElectronicaDocumento12 páginasGeneralidades ElectronicaMike Sabchez VilchisAún no hay calificaciones

- Tarea Unidad 3Documento5 páginasTarea Unidad 3Javiel Romero100% (1)

- 8255 PDFDocumento17 páginas8255 PDFAliangie Valeria ZambranoAún no hay calificaciones

- Segundo Parcial, Base de Datros JCCDocumento21 páginasSegundo Parcial, Base de Datros JCCErnestoo AdrianooAún no hay calificaciones

- Boletin 2Documento4 páginasBoletin 2Jose Teijeiro CruzAún no hay calificaciones

- Modelo 4 +1Documento4 páginasModelo 4 +1KrÚz JÓzeAún no hay calificaciones

- Unidad 2. Actividad 1. EntregableDocumento3 páginasUnidad 2. Actividad 1. EntregableGilber GomezAún no hay calificaciones

- Teclado Matricial 4x4Documento9 páginasTeclado Matricial 4x4Breyner Oroya Cruz100% (1)

- Qué Es Un ContadorDocumento2 páginasQué Es Un ContadorSergio Eduardo Hernandez LozanoAún no hay calificaciones

- GUÍA DE LABORATORIO No 1. MANEJO DE PHET, TINKERCAD Y SOLVE ELECDocumento16 páginasGUÍA DE LABORATORIO No 1. MANEJO DE PHET, TINKERCAD Y SOLVE ELECESTHER ISABEL CEBALLOS PORTILLOAún no hay calificaciones

- Actividad 3 - Unidad 4Documento1 páginaActividad 3 - Unidad 4cpyin88Aún no hay calificaciones

- Ejercicios de Arboles BinariosDocumento8 páginasEjercicios de Arboles BinariosRené De La RosaAún no hay calificaciones

- Codigos de ArduinoDocumento8 páginasCodigos de ArduinoruthAún no hay calificaciones

- Familia Lógica CmosDocumento14 páginasFamilia Lógica CmosKaro DukeAún no hay calificaciones

- Mapas de KarnaughDocumento10 páginasMapas de KarnaughCarlos CastilloAún no hay calificaciones

- 4 Integracion de Entidades Senales y Variables5Documento24 páginas4 Integracion de Entidades Senales y Variables5Camilo Andres RojasAún no hay calificaciones

- Algebra de BooleDocumento7 páginasAlgebra de BooleJosé Carlos GuerraAún no hay calificaciones

- Ejercicio de Estructuras de Datos PDFDocumento4 páginasEjercicio de Estructuras de Datos PDFJose AlejandroAún no hay calificaciones

- Estructura de Decision LogicaDocumento23 páginasEstructura de Decision LogicaMcGregor JamesAún no hay calificaciones

- Unidad 1 - Sección 1.2 Gráficas de Una FunciónDocumento27 páginasUnidad 1 - Sección 1.2 Gráficas de Una FunciónJulio Cesar De Los Santos MéndezAún no hay calificaciones

- Sumador RestadorDocumento15 páginasSumador RestadorJulio Cesar Carruyo VillalobosAún no hay calificaciones

- Operadores y Expresiones Con VHDLDocumento24 páginasOperadores y Expresiones Con VHDLjenafuAún no hay calificaciones

- MSIA - MAPR - Guia FinalDocumento16 páginasMSIA - MAPR - Guia FinalMiguel PérezAún no hay calificaciones

- Ps 1Documento7 páginasPs 1correorikAún no hay calificaciones

- Notacion InfijaDocumento2 páginasNotacion InfijaJudiith ReyesAún no hay calificaciones

- Tarea Método Simplex Ejemplo Básico A Mano para MaximizarDocumento5 páginasTarea Método Simplex Ejemplo Básico A Mano para MaximizarRoman Rivera BarronAún no hay calificaciones

- Cap 9 New MarginDocumento56 páginasCap 9 New MarginRoberto TorresAún no hay calificaciones

- Mantenimiento 1Documento5 páginasMantenimiento 1Osmar Gunnar Gutierrez Delgado100% (1)

- Ensayo de Procesadores PDFDocumento2 páginasEnsayo de Procesadores PDFLIZANDRO CARRERAAún no hay calificaciones

- Las 7 Consecuencias Negativas de Una Mala Red InformáticaDocumento2 páginasLas 7 Consecuencias Negativas de Una Mala Red InformáticaJuan A. Aguilera A.Aún no hay calificaciones

- Circuitos Logicos - Logica CombinacionalDocumento6 páginasCircuitos Logicos - Logica Combinacionalbrayan flores0% (1)

- Aplicaciones de Circuitos DigitalesDocumento15 páginasAplicaciones de Circuitos DigitalesAlex Pomier AliagaAún no hay calificaciones

- Laboratorio de Logica CombinacionalDocumento6 páginasLaboratorio de Logica CombinacionalAbimael Erasmo Huamani MallmaAún no hay calificaciones

- 1Documento15 páginas1leonelAún no hay calificaciones

- Santa JoaquinaDocumento27 páginasSanta JoaquinaKariennys MorenoAún no hay calificaciones

- Respuesta Matematica Basica 1Documento8 páginasRespuesta Matematica Basica 1KAREN MARGARITA RAMOS DIAZAún no hay calificaciones

- Mat - Adición y Sustracción de Números DecimalesDocumento5 páginasMat - Adición y Sustracción de Números DecimalesRichard Andres Cuadros TamayoAún no hay calificaciones

- Fichas U1 - MATEMÁTICA 2°-2023Documento10 páginasFichas U1 - MATEMÁTICA 2°-2023RubyVallejosAún no hay calificaciones

- Temario DEADocumento5 páginasTemario DEAPalmeIgAún no hay calificaciones

- Acv 2014 - Aritmetica 04Documento6 páginasAcv 2014 - Aritmetica 04Edinsson R. Javier VillanuevaAún no hay calificaciones

- Algebra 1ro - IbDocumento22 páginasAlgebra 1ro - IbFranciss MartínezAún no hay calificaciones

- 5to Prim Doc Vol1Documento166 páginas5to Prim Doc Vol1Jonathan FuentesAún no hay calificaciones

- Que Son Los Numeros EnterosDocumento3 páginasQue Son Los Numeros Enterosbuen_docente_danielAún no hay calificaciones

- AlgebraDocumento288 páginasAlgebraHombre Sin Miedo100% (1)

- Matematicas Pud 2 PlanificacionDocumento23 páginasMatematicas Pud 2 PlanificacionCARLOS PAUCAYAún no hay calificaciones

- Tarea 1 PROPEDEUTICO DE MATEMATICASDocumento5 páginasTarea 1 PROPEDEUTICO DE MATEMATICASHarold Oz100% (3)

- Topografia Compensacion de AngulosDocumento3 páginasTopografia Compensacion de AngulosPatricia Janett Inocente MorenoAún no hay calificaciones

- Prueba 6Documento54 páginasPrueba 6AngelvkAún no hay calificaciones

- Números RacionalesDocumento7 páginasNúmeros RacionalesYelitza PerezAún no hay calificaciones

- JuegosDocumento5 páginasJuegosHernando CuestaticAún no hay calificaciones

- Planificaciones de 2do A A7moDocumento32 páginasPlanificaciones de 2do A A7moErika Aleska Cheme CoxAún no hay calificaciones

- Unidad #1 Mat. 2°.Documento5 páginasUnidad #1 Mat. 2°.Lucas Silva GoicocheaAún no hay calificaciones

- Guía Didáctica 3ro BásicoDocumento21 páginasGuía Didáctica 3ro BásicoAlicia Fady Lobos AcuñaAún no hay calificaciones

- Tema 07Documento22 páginasTema 07kudasai_sugoiAún no hay calificaciones

- Actividad No.1 Numeros RealesDocumento6 páginasActividad No.1 Numeros RealesMiguel Angel AriasAún no hay calificaciones

- 4° Grado - Matematica Dia 16 de AbrilDocumento14 páginas4° Grado - Matematica Dia 16 de AbrilvaleskamillethAún no hay calificaciones

- Sumador RestadorDocumento15 páginasSumador RestadorasdsadwAún no hay calificaciones

- Enteros 1-6Documento14 páginasEnteros 1-6Keymar GladysAún no hay calificaciones

- 4.-Sucesiones y Sumatorias Notables 2022Documento12 páginas4.-Sucesiones y Sumatorias Notables 2022pablochallco179Aún no hay calificaciones

- Experiencia 4Documento27 páginasExperiencia 4WALTER RUIZ ALCALÁAún no hay calificaciones