Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Tutorial Maxplus

Tutorial Maxplus

Cargado por

Richard MooreDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Tutorial Maxplus

Tutorial Maxplus

Cargado por

Richard MooreCopyright:

Formatos disponibles

DISEO DIGITAL CON LOGICA PROGRAMABLE MANUAL MAX+PLUS II

Sadot Alexandres F.

DISEO DE SISTEMAS DIGITALES

INDICE: 1.- INTRODUCCIN. ......................................................................................... 2

1.1.- ENTORNO MAX+PLUS II. ........................................................................................................3 1.2.- TARJETA PARA EL DESARROLLO DE PROTOTIPOS........................................................................4 1.2.1.- PLDS .....................................................................................................................................5 1.2.2.- OSCILADOR.............................................................................................................................5 1.2.3.- PULSADORES ...........................................................................................................................5 1.2.4.- MICROINTERRUPTORES ...........................................................................................................6 1.2.5.- DISPOSITIVOS LUMINOSOS. .....................................................................................................7 1.2.6.- MEMORIA RAM......................................................................................................................9 1.2.7.- CONECTOR DE ACCESO A TERMINALES DE USUARIO..............................................................11 1.2.8.- ZONA DE WRAPPING..............................................................................................................12 1.2.9.- ACCESO A LOS TERMINALES DE LA TARJETA ......................................................................12

2.- DEFINICIN DE UN PROYECTO. ............................................................ 13

2.1.- JERARQUA DE UN PROYECTO...................................................................................................15

3.- EJEMPLO BSICO DE OPERACIN. ...................................................... 15

3.1.- CREACIN DEL PROYECTO......................................................................................................16 3.1.1.- CAPTURA DE ESQUEMAS......................................................................................................16 3.1.1.1.- CAPTURA POR OR CAD. ...................................................................................................18 3.1.1.2.- CAPTURA DE ESQUEMAS EN EL ENTORNO ALTERA . .....................................................19 3.1.1.4.- ASIGNACIN DEL PATILLAJE DE LA FPGA . ....................................................................19 3.2.- VERIFICAR LAS REGLAS DE DISEO.............................................................................................21 3.3.- COMPILAR, COMPLETAR Y ENSAMBLAR. .............................................................................23 3.4.- PROGRAMAR LA TARJETA DE DESARROLLO CON EL EJEMPLO. ...................................28 3.6.- VERIFICACIN DEL FUNCIONAMIENTO. ...........................................................................32

4.- SIMULACIN LOGICA.............................................................................. 33

4.1.- SIMULACIN LGICA CON HERRAMIENTAS DE ALTERA...............................................33 4.2.- FICHEROS GRFICOS PARA SIMULACIN. .................................................................................34 4.3.- DEFINICIN DE ESTMULOS .......................................................................................................38 4.3.1.- DEFINICIN DE SEALES ....................................................................................................39 4.4.- PUESTA EN MARCHA DE LA SIMULACIN ........................................................................42

5.- LENGUAJES HDL. ...................................................................................... 44

5.1.- REALIZACIN PRCTICA DE CIRCUITOS MEDIANTE EL LENGUAJE HDL. ........................44 5.1.2.- CREAR UN FICHERO DE DISEO..........................................................................................46 5.1.2.1.- INTERFACE DEL DISPOSITIVO Y DECLARACIN DE ENTIDAD. .......................................47 5.2.- LIBRERIAS VHDL DE USUARIO...........................................................................................56 5.3.- INTEGRACIN DE MDULOS VHDL EN ESQUEMAS.........................................................57

DISEO DE SISTEMAS DIGITALES

1.- INTRODUCCIN.

Los entornos EDA (Electronic Design Automation) son las herramientas de trabajo ms comnmente empleadas en el diseo e implantacin de circuitos lgicos. Permiten una gran versatilidad a la hora de simular cualquier posible situacin en el funcionamiento de los diseos efectuados por el profesional que emplea esta herramienta, adems son sencillos de manejar gracias a las interfaces grficas que incorporan las plataformas de diseo como: ALTERA, OrCAD, XILINX, que permiten la instrumentacin de dichos diseos y su implantacin en los PLDs y FPGA`s. Dichas herramientas de trabajo son puestas al alcance del alumno en esta obra con el fin de dar a conocer las ltimas tcnicas de diseo con una formacin integral en todas ellas. Para ello, a lo largo de los diferentes captulos del tutorial y de las prcticas que en este libro se proponen, el alumno adquirir los conocimientos que le permitirn manejar los dispositivos fabricados por ALTERA , junto con el soporte de software Max+plus II como principal herramienta de diseo, verificacin y simulacin de prcticas y proyectos en el Laboratorio de Sistemas Digitales y posteriormente en su vida profesional. Para la implantacin de los diseos que se efectuarn durante el curso, dispondremos de un FPGA situado en una tarjeta de desarrollo que permitir una fcil simulacin de los circuitos y prcticas propuestos, mediante una serie de visualizadores, pulsadores, microinterruptores y otros elementos, tiles para realizar simulaciones fsicas en la tarjeta de desarrollo de los diseos realizados .

DISEO DE SISTEMAS DIGITALES

1.1.- ENTORNO MAX+PLUS II.

Primeramente nos familiarizaremos con el entorno de trabajo. El software que vamos a emplear es una versin de ALTERA que se ofrece para estudiantes y Universidades. Al iniciar el programa encontramos la siguiente pantalla:

En la parte superior de la misma nos encontramos con los mens tpicos de las aplicaciones bajo Windows. Adems, por debajo est una lnea de iconos que nos dan acceso a las diferentes partes del programa. A continuacin detallaremos el significado de cada uno de estos iconos y la funcin que realizan:

Visualizador de jerarquas.

Editor de Patillajes y asignaciones. (Floorplan)

Compilador.

Ventana del simulador.

DISEO DE SISTEMAS DIGITALES

Analizador de tiempos.

Programador.

Especifica el nombre del proyecto.

Cambia el nombre del proyecto al del archivo que se est empleando.

Maneja el archivo de diseo de nivel superior.

Opciones para guardar (Archivos, simulador y compilador).

Si durante la ejecucin del programa surge alguna duda, en cualquier momento, situando el cursor del ratn sobre el icono correspondiente, aparece en la parte inferior de la pantalla una descripcin de su funcin.

1.2.- TARJETA PARA EL DESARROLLO DE PROTOTIPOS

En esta parte del documento se describe la tarjeta para el desarrollo de prototipos SEC-7000. Esta tarjeta ser empleada por el alumno para la implementacin fsica de los diseos realizados en el entorno MAX+plus II. Los elementos de que disponemos en nuestra tarjeta de prototipos son: 1.- Una PLD de la familia MAX7000S de ALTERA . 2.- Un oscilador de cuarzo de 1.8432 MHz... 3.- 4 Pulsadores situados en la tarjeta. 4.- 16 Microinterruptores. 5.- 3 Indicadores de siete segmentos. 6.- 10 LEDs . 7.- Una memoria RAM (con posibilidad de ampliacin). 8.- Zona de insercin de componentes complementarios al diseo. 9.- Conector de acceso a los terminales accesibles de la FPGA.

DISEO DE SISTEMAS DIGITALES

1.2.1.- PLDS

La tarjeta dispone de cierta flexibilidad respecto al tipo de PLD que puede llevar instalada. En concreto, puede ser cualquiera de las siguientes: EPM7064S. EPM7096S. EPM7128S. EPM7160S.

La tarjeta requiere que el integrado de la PLD's tenga un encapsulado PLCC de 84 pines para poder ser colocados en el zcalo disponible en la tarjeta y funcione correctamente con el Software.

1.2.2.- OSCILADOR

El mdulo oscilador genera una seal de frecuencia de 18432 MHz, que puede ser usada como seal de reloj cuando sea preciso, dividindola si fuera necesario para alimentar de forma sncrona a dispositivos de distinta frecuencia que empleemos en nuestros desarrollos. El oscilador est conectado al pin 83 del PLD, que se corresponde con una de las entradas dedicadas del mismo. Las entradas dedicadas de las EPLD's de ALTERA tienen caractersticas especiales que las hacen apropiadas para su conexin a seales que precisen de un alto FAN-OUT y un bajo skew, tales como las de inicializacin (reset) o reloj.

1.2.3.- PULSADORES.

Cada pulsador de la tarjeta dispone de un circuito anti-rebote de forma que pone un nivel alto TTL (+5V) en un pin de la FPGA mientras se mantiene pulsado y en caso contrario se asigna de forma permanente un nivel bajo (GND). Los cuatro pulsadores se identifican como S1 a S4. Los tres ltimos ( S2, S3 y S4 ) se encuentran conectados a entradas dedicadas y S1 se encuentra conectado a un pin de entrada/salida. La interconexin entre los pulsadores y los terminales de la PLD empleada en esta tarjeta de circuito impreso se detalla en la siguiente tabla:

PULSADOR S1 S2 S3 S4 PIN F.P.G.A. 39 2 1 84

DISEO DE SISTEMAS DIGITALES

1.2.4.- MICROINTERRUPTORES.

La tarjeta dispone de diecisis microinterruptores distribuidos en dos mdulos de ocho que se encuentran en la parte izquierda. La forma con que se han identificado para su empleo en los diseos es el siguiente: 1.- Todos los nombres comienzan por SW. 2.- A continuacin viene un 1 un 2 para identificar el mdulo al que pertenecen. 3.- Finalmente viene el nmero que ocupa dentro del mdulo de microinterruptores, precedido por el smbolo _ . Cada uno de los microinterruptores se encuentra conectado a un terminal de la PLD y pone un nivel bajo TTL (GND) en la posicin ON mostrada en la serigrafa de los mismos y un nivel alto (+5V) en la posicin opuesta. La interconexin de los microinterruptores y los terminal se muestra a continuacin:

MICROINTERRUPTOR SW1_1 SW1_2 SW1_3 SW1_4 SW1_5 SW1_6 SW1_7 SW1_8 SW2_1 SW2_2 W2_3 SW2_4 SW2_5 SW2_6 SW2_7 SW2_8 TERMINAL F.P.G.A. 12 15 16 17 18 20 21 22 24 25 27 28 29 30 31 33

DISEO DE SISTEMAS DIGITALES

1.2.5.-DISPOSITIVOS LUMINOSOS.

La tarjeta dispone de tres indicadores luminosos de siete segmentos (con punto decimal) y de una matriz que tiene diez LEDs. Para polarizar tanto los segmentos de los indicadores como los LEDs hay que poner un nivel bajo 0 en el terminal al que estn conectados, ya que son de nodo comn.

Estos tres dispositivos estn multiplexados entre s junto con ocho de los LEDs de la matriz, por lo que se emplea cuatro terminales de la FPGA para generar las seales de control adecuadas para que se puedan emplear todos ellos de forma simultnea en los diseos que realice el alumno. Cada seal de multiplexacin habilita, con un nivel alto (+5V), el funcionamiento del indicador o del grupo de LEDs individuales de la matriz con el que est asociado. En adelante se har referencia a los indicadores de siete segmentos de acuerdo con la siguiente notacin:

DISPLAY1 identificado por la etiqueta U6. DISPLAY2 identificado por la etiqueta U7. DISPLAY3 identificado por la etiqueta U8.

DISEO DE SISTEMAS DIGITALES

SW5

ON 1 a b c d e f g punto mux0 mux1 mux2 mux3 led9 led10

U6 a f e d g b c

U7 a f e d g b c

U8 a f e d g b c

U9

SW6

ON 1

ALTERA

MAX EPM7128SLC84

S1 S2 S3 S4 PULSADORES

BUS DE DATOS 10 9 8 7 6 5 4 3 25 24 21 23 2 26 27 20 22 1 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 CE OE VPP MEMORIA RAM U16 O0 O1 O2 O3 O4 O5 O6 O7 11 12 13 15 16 17 18 19

BUS DE DIRECCIONES

27256

OSCILADOR 1.8 MHz.

Los ocho LEDs que estn multiplexados con los indicadores, de los diez que forman la matriz, son los que van del nmero 1 al 8, empezando por arriba. Los LED 9 y 10 situados en la parte inferior se encuentran asignados a terminales independientes de la F.P.G.A. y no requieren multiplexacin para su funcionamiento, es decir, se pueden asignar mediante un terminal de entrada/salida de forma directa. Las seales de multiplexacin se denominan MUX_0, MUX_1, MUX_2 y MUX_3. Estn asociadas a los displays y al grupo de Leds tal y como se muestra en la siguiente tabla:

SEAL DE MULTIPLEXACIN DISPOSITIVO ASOCIADO

MUX_0 MUX_1 MUX_2 MUX_3

DISPLAY1 DISPLAY2 DISPLAY3 LED'S

Los terminales de la PLD conectados a las seales de multiplexacin empleadas en el control son los indicados en la siguiente tabla:

8

DISEO DE SISTEMAS DIGITALES

SEAL DE MULTIPLEXACIN

TERMINAL F.P.G.A. 77 76 75 74

MUX_0 MUX_1 MUX_2 MUX_3

De la misma forma, los terminales que han sido conectados a los segmentos y al punto decimal de los tres indicadores y a los ocho Leds multiplexados de la matriz son los que aparecen en la siguiente tabla:

SEGMENTOS DEL INDICADOR LEDS DE LA MATRIZ TERMINAL F.P.G.A.

SEG A SEG B SEG C SEG D SEG E SEG F SEG G PUNTO DECIMAL

LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

9 8 4 81 80 10 11 5

Los dos Leds restantes son denominados como LED_1 y LED_2. Los terminales de la PLD a los que est asignada su conexin son:

TERMINAL F.P.G.A. 70 73

LEDS LED_1 LED_2

1.2.6.- MEMORIA RAM.

La memoria RAM de la tarjeta es un circuito integrado con una capacidad de 32K x 8 bits que puede ser reemplazado por otro dispositivo de mayor capacidad con acuerdo al patillaje de la tarjeta de circuito impreso que dispone de 28 terminales en el zcalo dispuesto para tal efecto. Dicha sustitucin del integrado de la memoria dar lugar a un nuevo replanteo de los terminales de entrada y de salida con respecto a los terminales de la FPGA.

Las seales de interconexin entre la memoria y la PLD son las siguientes: 1.- El bus de direcciones: formado por quince lneas A0 A14.

DISEO DE SISTEMAS DIGITALES

2.- El bus de datos : formado por 8 lneas identificadas como DATA0 DATA7 . 3.- Seales de control: Chip Select, Output Enable y Write Enable, que son tres lneas identificadas como CS, OE y WE, que realizan el control de acceso a la memoria y la realizacin de lectura y escritura en la misma.

La interconexin entre estas seales y los terminales de la FPGA se indica en la siguiente tabla: TERMINAL DE LA MEMORIA

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 DATA0 DATA1 DATA2 DATA3 DATA4 DATA5

TERMINAL F.P.G.A.

51 49 45 54 56 58 61 64 63 60 44 57 67 65 69 52 50 48 34 36 35

10

DISEO DE SISTEMAS DIGITALES

DATA6 DATA7 CS OE WE

37 40 41 55 68

El diagrama de bloques interno de la memoria RAM es el siguiente:

1.2.7.- CONECTOR DE ACCESO A TERMINALES DE USUARIO.

Los terminales de la EPLD que no estn conectados a ninguno de los recursos anteriormente descritos y que no estn dedicados a la programacin del dispositivo, son accesibles por medio de un conector, situado junto a la memoria. Los terminales libres de la PLD son 3, y se identifican como CUS_1 a CUS_3. Numerando los pines del conector JP11 a partir del nmero 1 serigrafiado en la tarjeta, la asignacin entre etiquetas de las patillas del conector y los terminales de la EPLD se muestra en la siguiente figura.

NOMBRE DEL TERMINAL

TERMINAL F.P.G.A.

PATILLA DEL CONECTOR

11

DISEO DE SISTEMAS DIGITALES

CUS2_1 CUS2_2 CUS2_3

46 79 6

1 2 3

1.2.8.- ZONA DE WRAPPING.

La zona de wrapping permite aadir hardware adicional para aplicaciones en que los recursos de la placa sean insuficientes. El hardware de esta zona puede conectarse con la EPLD por medio de los terminales de usuario que se encuentren libres de otras conexiones y si estos son insuficientes, la conexin se realizar por medio de los terminales de entrada/salida que no se hayan empleado en otras funciones o cometidos. En el caso de que no sean necesarios estos elementos de hardware adicionales para otra aplicacin, pueden ser desalojados de la tarjeta y permitir la instalacin de otros recursos que resulten necesarios en cada caso .

1.2.9.- ACCESO A LOS TERMINALES DE LA TARJETA.

Los terminales asignados a recursos de la tarjeta estn unidos a los ocho conectores que rodean la EPLD, con el fin de permitir su monitorizacin con un analizador lgico o un osciloscopio, o que se puedan utilizar como pines de usuario, en el caso de que se desmonten recursos de la placa o se amplen los mismos para aplicaciones personalizadas del prototipo de desarrollo.

La asignacin de los terminales de los recursos de la tarjeta a los conectores se detalla en la siguiente tabla:

12

DISEO DE SISTEMAS DIGITALES

CONECTOR

P1 NC 12 53 34 74 73 10 75

P2 15 14 51 36 GND 71 8 77

P3 17 16 49 NC 70 69 6 79

P4 NC 18 GND 40 68 67 4 81

P5 21 20 45 NC VCC 65 2 83

P6 23 22 NC 44 64 63 84 1

P7 25 24 41 46 62 61 NC VCC

P8 27 VCC 39 48 60 NC 80 5

P9 29 28 37 50 58 57 NC GND

P10 31 30 35 52 56 55 76 9

P11 33 GND NC NC 54 NC NC 11

JP1 JP2 JP3 JP4 JP5 JP6 JP7 JP8

2.- DEFINICIN DE UN PROYECTO.

El primer paso que se debe dar al comenzar cualquier diseo es definir el proyecto. Ms adelante encontraremos todos los pasos necesarios para poder realizarlo, pero a modo de

13

DISEO DE SISTEMAS DIGITALES

introduccin, comentaremos algunos aspectos de la jerarqua de los proyectos en el entorno MAX+PLUS II. Un proyecto est formado por una serie de ficheros, que pueden ser clasificados bsicamente de dos formas: Ficheros auxiliares Ficheros de diseo. FICHEROS DE DISEO: Puede ser de diversos tipos: Grfico, de texto o de formas de onda. Contienen la informacin que ms tarde ser procesada por un compilador que preparar el NETLIST para ser volcado junto con otras informaciones sobre la tarjeta de prototipos. A continuacin se realiza una descripcin de todos estos tipos de ficheros que podemos encontrarnos: 1. Ficheros de texto HDL: Pueden estar en lenguaje AHDL con extensin (.tdf) bien en VHDL (.vhd). 2. Ficheros grficos: Si son generados por la captura de esquemas de nuestro propio entorno de ALTERA, stos tendrn la extensin ( .gdf). En el caso de que usemos OrCAD Capture, compatible con las libreras de ALTERA, entonces la extensin ser (.sch). 3. Ficheros NETLISTS: stos son formados al importar de otros entornos de trabajo distintos a MAX+PLUS II y pueden estar en los formatos: EDIF (.edf), XNF (.xnf). Cualquier otro formato de Netlist empleado no ser reconocido por el software del compilador. 4. Ficheros de formas de onda: Son generados por el editor de formas de ondas del programa y especifican el tipo de onda empleado en simulaciones. La extensin de estos ficheros es (.wdf). 5. Archivos de diseo de ALTERA. (.adf) 6. Archivos de mquinas de estado. (.smf)

FICHEROS AUXILIARES: Son los asociados al proyecto en el que nos encontramos trabajando y los crea el programa de ALTERA. Algunos de ellos se generan automticamente por la aplicacin que estemos ejecutando y otros los crea el usuario al definir smbolos, situaciones especiales en el programa, etc. Algunos de los ms comunes que nos podemos encontrar son: Ficheros de programacin del dispositivo PLD. (.sof , .pof , .hex ) Ficheros de simulacin. (.scf .snf ) Informes de compilacin. (.rpt)

14

DISEO DE SISTEMAS DIGITALES

Ficheros de configuracin. (.acf) Smbolos (.sym)

2.1.- JERARQUA DE UN PROYECTO.

Todo proyecto desarrollado en un capturador dispone de una jerarqua de archivos que son los componentes del proyecto. Estos archivos se presentan de la siguiente manera, formando un rbol:

En la imagen mostrada anteriormente podemos ver como est compuesta la jerarqua de archivos de un determinado diseo del cual parten otros diseos complementarios con la informacin sobre los componentes y las simulaciones efectuadas en el transcurso del proyecto. Las diversas ramificaciones del rbol nos llevan a los archivos de menor nivel en la jerarqua. El punto de partida de estos va siendo otro archivo de mayor nivel, hasta llegar a la parte superior del rbol (TOP LEVEL) en donde se encuentra el principal archivo del diseo que sirve de punto de partida.

3.- EJEMPLO BSICO DE OPERACIN.

Para seguir con mejor precisin este manual, emplearemos unos sencillos proyectos, basados en el diseo de circuitos combinacionales y secuenciales a los que alimentaremos con el reloj de la tarjeta mediante unos divisores de frecuencia.

15

DISEO DE SISTEMAS DIGITALES

El proceso que se va a seguir para estudiar los ejemplos, as como todos los diseos que se realicen, se muestra a continuacin: Crear el proyecto y capturar el esquema del ejemplo. 1. Verificar las reglas de diseo. 2. Compilar. 3. Corregir posibles fallos. 4. Programar la tarjeta de desarrollo con el ejemplo. 5. Verificacin del funcionamiento.

3.1.- CREACIN DEL PROYECTO.

Primeramente se va a comentar los pasos a seguir para crear un nuevo proyecto. Para ello debemos crear o importar el archivo que va a ser el nivel superior de la jerarqua e identificar el directorio en el que se encuentra. El primer paso consistir, por tanto en la captura del ejemplo del contador y a partir de ah se establecer el proyecto de trabajo.

3.1.1.- CAPTURA DE ESQUEMAS.

Existen varios procedimientos para realizar la captura de un esquema bajo diversas plataformas, las ms corrientes son: OrCAD ALTERA EWB PROTEL (.sch) (.gdf) (.sch) (.sch)

16

DISEO DE SISTEMAS DIGITALES

Para cualquiera de ellos emplearemos la opcin del men FILE mediante la opcin OPEN o la opcin PROJECT dependiendo de la localizacin del archivo.

Si el archivo que vamos a emplear est en otro proyecto, lo podemos seleccionar a travs de la pantalla anterior, indicando el proyecto en el que se encuentra y seleccionando el visualizador de jerarquas. Posteriormente seleccionamos el elemento que queremos dentro del rbol de seleccin y realizamos doble click sobre l para que se abra el editor grfico del programa, con el archivo especificado.

17

DISEO DE SISTEMAS DIGITALES

En caso de que se trate de un archivo que no se encuentre en nuestro proyecto de trabajo, emplearemos la opcin de apertura de ficheros e indicaremos en la misma el formato de fichero que queremos abrir, la ruta de acceso a dicho fichero y el nombre del mismo en la pantalla que se muestra a continuacin:

3.1.1.1.- CAPTURA POR ORCAD.

Esta primera opcin es la ms adecuada para aquellas personas que tengan experiencia en el manejo este tipo de software o estn familiarizados con el entorno OrCAD y sus funciones. Los archivos resultantes de dicha captura son los que tienen la extensin (*.sch). El nico problema que puede surgir en estos casos es la compatibilidad entre libreras especficas de un determinado entorno que no sean compatibles con nuestro software de ALTERA. En cualquiera de estos casos, habr que consultar al profesor para buscar la mejor solucin. Los archivos que proceden de OrCAD tienen la extensin sch por lo que ser necesario indicarlo en la seleccin: Graphic Editor files del men OPEN .

18

DISEO DE SISTEMAS DIGITALES

3.1.1.2.- CAPTURA DE ESQUEMAS EN EL ENTORNO ALTERA.

La otra posibilidad para manejar un esquema es crearlo nosotros mismos dentro del propio capturador que el programa de ALTERA nos proporciona. Esto lo haremos mediante las libreras de componentes y accesorios que tiene el programa. Para crear un esquema nuevo seguiremos los siguientes pasos. En primer lugar, en el men archivo, seleccionamos la opcin NEW y nos encontraremos con una pantalla en la que marcamos las opciones indicadas. Esta pantalla es la siguiente:

A partir de ah, dibujaremos el esquema del contador, segn se indic en apartados anteriores y siguiendo el modelo que podemos encontrar en el anexo a este documento.

3.1.1.4.- ASIGNACIN DEL PATILLAJE DE LA FPGA.

Como se indic en el apartado de la tarjeta de desarrollo, la FPGA que estamos empleando se encuentra dentro de una tarjeta de circuito impreso junto con otros componentes accesorios. La asignacin de cada una de las salidas de la FPGA a dichos perifricos se debe realizar en el esquema principal de la siguiente manera: 1. Identificar en las tablas del apartado 1.2 los terminales que vamos a necesitar en nuestra simulacin.

19

DISEO DE SISTEMAS DIGITALES

2. Mediante el botn derecho del ratn, se tiene que seleccionar la opcin ASSIGN, PIN/LOCATION/CHIP...

Y la pantalla que nos encontraremos ser la siguiente:

En esta pantalla asociamos una conexin o referencia del esquema a un terminal de la FPGA, de forma que cuando se programe el circuito, la referencia del esquema ser conectada internamente con el terminal elegido del integrado.

20

DISEO DE SISTEMAS DIGITALES

3.2.- VERIFICAR LAS REGLAS DE DISEO.

Puesto que trabajamos con software o herramientas de diseo, se han definido una serie de reglas de diseo mediante las cuales evitamos que el ensamblador del programa cometa error al realizar los pasos finales (por ejemplo, si el compilador tiene un bucle). Adems, cumplir estas reglas es indispensable para realizar un diseo seguro, evitando as muchos de los fallos ms comunes como dejar componentes sin conectar, cortocircuitos de la alimentacin, y otros. La operacin que tenemos que realizar para comprobar el circuito implica que lo guardemos, al realizarse una orden conjunta de verificacin y salvado del diseo con el que estemos trabajando. Las rdenes para hacerlo son: - En el men FILE, seleccionamos la opcin PROJECT. - Una vez all, seleccionamos SAVE&CHECK entre las opciones, y comenzar a ejecutarse el verificador que al finalizar se quedar con la siguiente pantalla:

Que mostrar tambin los errores y advertencias que hayan podido surgir en el proceso de verificacin. Lo ideal es que aparezca de la siguiente manera:

21

DISEO DE SISTEMAS DIGITALES

Pero puede que al principio surjan errores que se puedan arreglar sin ninguna dificultad para el alumno. Con respecto a las advertencias (Warnings), son cosas que no influyen directamente en el correcto funcionamiento del diseo, pero es conveniente que sean revisadas por el alumno antes de continuar con el proceso siguiente. Pero, Cmo solucionar los errores que tenga el diseo? Para esta operacin, el programa dispone de una ventana de avisos sobre errores o advertencias en la cual nos indica cul han sido estos y en que lugar del esquema se encuentran. Para acceder a ellas, tras pulsar la aceptacin en la ventana final que vimos antes, aparece otra ventana junto a la del compilador donde se procesan los mensajes de error.

Seleccionamos uno de ellos con el cursor del ratn y se pulsa sobre el botn Locate de esa ventana. Con ello se activa una bsqueda automtica en el esquema en donde nos localizar el error. Una vez localizado el error por el alumno, se procede a su correccin y se vuelve a iniciar este apartado para verificar que todo est correcto.

22

DISEO DE SISTEMAS DIGITALES

3.3.- COMPILAR, COMPLETAR Y ENSAMBLAR.

El siguiente paso que tenemos que dar es convertir el esquema del editor grfico que acabamos de comprobar, en un archivo que el ordenador sea capaz de reconocer, simular y analizar. Para ello empleamos el compilador, mediante las instrucciones: FILE, PROJECT, SAVE&COMPILE. Automticamente se guardar el archivo del proyecto y comenzar a ejecutarse el compilador en una ventana como la siguiente:

Como podemos observar en la figura, se han creado varios archivos asociados a la compilacin, completado rellenado y ensamblaje del proyecto en curso. Estos archivos aparecern posteriormente en el visualizador de jerarquas como auxiliares que nos indican que el proyecto fue compilado con el programa. Al igual que en la verificacin de las reglas de diseo, al concluir el proceso aparecer una ventana que nos indica los errores cometidos y las advertencias.

Como en el verificador de diseo, si se produce algn error en el proceso de compilado, quedara reflejado en la pantalla anterior y se podra seguir un proceso anlogo en la verificacin de los errores mediante la pantalla de avisos:

23

DISEO DE SISTEMAS DIGITALES

Se corrigen los errores que se hayan podido cometer en el proceso y se vuelve a realizar la compilacin del proyecto segn se mostr al comienzo de este apartado. Si alguno de los errores mostrados anteriormente persiste una vez realizada la verificacin y correccin por el alumno, ser conveniente que ste repase paso por paso con el profesor el proceso seguido en busca del posible fallo, que emplee la ayuda disponible en el programa, accediendo a ella mediante el botn: HELP ON MESSAGE situado en la parte inferior derecha de la pantalla anterior.

24

DISEO DE SISTEMAS DIGITALES

EJEMPLO 1: Circuito Lgico 1. Decodificador Hexadecimal a 7 segmentos.

Realice el esquema lgico de la siguiente pgina en el editor grfico de ALTERA. El circuito corresponde a un decodificador de 4 bits en hexadecimal a un visualizador de 7 segmentos que corresponden a la figura siguiente segn los 4 bits de entrada.

25

DISEO DE SISTEMAS DIGITALES

26

DISEO DE SISTEMAS DIGITALES

En primer lugar inserte los componentes haciendo doble click con el cursor del ratn en la ventana de dibujo. Aparecer la siguiente pantalla de seleccin de componentes en la que existen varias libreras:

Se realiza la seleccin del componente and2 que corresponde, como su nombre indica, a una puerta and de dos entradas. Con este mismo procedimiento se van ubicando todas y cada una de las puertas lgicas del circuito mostrado en el enunciado y una vez emplazadas se procede a la insercin de los terminales de entrada y de salida. Estos componentes reciben el nombre de output e input y se pueden obtener de la misma forma que las puertas lgicas que ya tenemos en nuestro esquema. Para editar las propiedades de alguno de estos componentes, y en especial los nombres de los terminales de entrada y salida, colocamos el ratn sobre el tem a modificar y hacemos click sobre l. Automticamente el componente seleccionado es recuadrado en rojo, tal y como se muestra en la figura: Entonces se puede seleccionar el texto y editarlo, o bien pulsar con el botn derecho del ratn y acceder a otras propiedades:

27

DISEO DE SISTEMAS DIGITALES

Para trazar el cableado entre los diferentes componentes, site el cursor sobre uno de los extremos del terminal origen y deslice ste sobre el tablero de dibujo hasta conseguir la forma del cable que se adapte a las necesidades del circuito. Repita esta operacin hasta completar el esquema propuesto. A continuacin, siga los pasos descritos anteriormente en este tutorial para salvar el diseo con el nombre: hex7seg.gdf y a continuacin realice una comprobacin y la correspondiente simulacin hasta que no existan errores en el circuito.

3.4.- PROGRAMAR LA TARJETA DE DESARROLLO CON EL EJEMPLO.

Nos encontramos en la parte final del proceso en donde ejecutamos una parte del programa en la cual se produce la programacin en la FPGA del diseo realizado por el alumno. Como ya se explic en los primeros apartados relacionados con la tarjeta de desarrollo de prototipos, los datos del ordenador son volcados a la tarjeta a travs del puerto paralelo del ordenador y un medio de transmisin fsico con el dispositivo que es el cable de conexin, segn se muestra en la siguiente figura:

28

DISEO DE SISTEMAS DIGITALES

La asignacin de los contactos de dicho conector se muestra en la siguiente tabla:

En la parte que concierne al software, el programador de ALTERA realiza la funcin de transferir el diseo efectuado a la tarjeta. Primeramente se tiene que especificar al programa qu tipo de tarjeta, de entre las posibles alternativas posibles, se va a emplear. Es conveniente realizar esta operacin antes de asignar las patillas en el circuito esquemtico y de compilar el diseo. Esta operacin se realizar en el men ASSIGN en la opcin DEVICE , mediante la pantalla siguiente:

29

DISEO DE SISTEMAS DIGITALES

La Familia de FPGA EPLD seleccionada es la MAX7000S, y el dispositivo que tiene la tarjeta de desarrollo del laboratorio es la EPM7128SLC84-7 (-15). Este elemento puede ser detectado de forma automtica por el software en el caso de no conocer exactamente el modelo que estamos empleando, en el caso de trabajar con dispositivos diferentes al del Laboratorio. Una vez realizada la seleccin, aceptamos los valores fijados y el sistema queda listo para realizar la simulacin con la tarjeta del laboratorio. Para ello, y continuando con el ejemplo propuesto, vamos a activar la opcin del programador. Como en ocasiones anteriores, se activar automticamente una pantalla en donde se proceder a la programacin de nuestro diseo en la memoria interna de la tarjeta para que podamos simular el circuito.

Para comenzar el proceso seleccionamos el botn PROGRAM . La pantalla del programador tiene este aspecto:

Si todo ha transcurrido con normalidad, en ella se crearn los ltimos archivos auxiliares en donde se guarda la informacin necesaria para ejecutar la aplicacin en la tarjeta. Desde aqu tambin podemos seleccionar el dispositivo de hardware que vayamos a emplear y verificar si ste est correctamente conectado a nuestro PC y se encuentra alimentado. En caso contrario aparecer el siguiente mensaje de error y tendremos que comprobar la alimentacin y las conexiones del aparato.

30

DISEO DE SISTEMAS DIGITALES

En este proceso, se definen fsicamente las conexiones entre los terminales del integrado y el dispositivo lgico que ha sido programado. Para visualizar cmo ha quedado distribuidas estas conexiones empleamos el FLOORPLAN EDITOR, que es una herramienta de visualizacin con una pantalla como la que se muestra a continuacin:

Situando el cursor del ratn sobre la cabecera de los bloques representados en la figura, el programa nos dar informacin acerca de ese contacto, su procedencia y la patilla de la FPGA a la que corresponde la conexin (si es entrada salida) el integrado al que pertenecen de los empleados en el diseo. Adems disponemos de un estudio estadstico de la congestin y el nivel de aprovechamiento que tenemos de los recursos del sistema. Para acceder a ella, hacemos Doble click sobre la cabecera del integrado del cual queramos saber sus parmetros y encontraremos la siguiente pantalla:

31

DISEO DE SISTEMAS DIGITALES

Con este proceso se puede analizar cualquier nodo del circuito y plantear posibles alternativas para mejorar los recursos de que se dispone. Esta informacin no ser relevante en el ejemplo propuesto en este manual pero, sin duda, puede ser muy til cuando el diseo que se desee realizar tenga mayores perspectivas y se encuentre prximo a superar las capacidades de la FPGA, teniendo en cuenta que el integrado que empleamos es uno de los Hermanos menores de la familia de EPLD que hay en el mercado.

3.6.- VERIFICACIN DEL FUNCIONAMIENTO.

Ya hemos realizado todos los pasos para convertir un proyecto sobre el papel en un modelo ejecutable por el alumno en una tarjeta de circuito impreso diseada para tal efecto. Ahora lo que resta es que ste compruebe que las condiciones de funcionamiento que haba especificado en su diseo se ajusten a las que est observando en la tarjeta. Hay que tener muy en cuenta que la alimentacin de dicha tarjeta ha de ser de +5V y que no se debe superar sta o se provocar una avera. Las tarjetas estn dotadas de una proteccin contra sobretensiones, pero no es recomendable superar el valor antes mencionado al aplicar tensin en las bornas de alimentacin.

32

DISEO DE SISTEMAS DIGITALES

Tambin hay que vigilar que la conexin de la tarjeta con el ordenador est correcta y asegurada, ya que si se desprende el conector puede dar lugar a un mal funcionamiento del proceso de volcado de datos que es realizado al programar la tarjeta.

4.- SIMULACIN LOGICA.

Los primeros pasos a dar para realizar la simulacin lgica pasan por la creacin de un modelo de simulacin a partir de los ficheros que se han empleado para hacer el diseo y lo enfocaremos a un tipo de simulacin funcional o con retardos. Definiremos tambin una serie de Vectores de test que son un conjunto de estmulos o seales que aplicamos a los elementos de entrada de nuestro circuito para verificar su funcionamiento bajo una serie de caractersticas definidas en los mismos. La creacin de estas seales de entrada vectores de test debe ser realizada con toda precaucin, ya que se trata de un paso muy importante en la simulacin lgica que resulta ser la base de la comprobacin del circuito. Esta operacin puede ser efectuada mediante dos mtodos: uno grfico y otro mediante un lenguaje de texto, como por ejemplo VHDL o VERILOG, muy extendidos en la Industria. La complejidad de la simulacin depende proporcionalmente del circuito que tratemos de verificar, ya que a mayor nivel de circuito, ms dificultad a resolver por la mquina. En cualquier caso, para todas la aplicaciones que se vern en este curso, la simulacin lgica no tomar ms de unos minutos de trabajo por parte del software de aplicacin.

4.1.- SIMULACIN LGICA CON HERRAMIENTAS DE ALTERA.

Como ejemplo de la simulacin lgica con MAX+PLUS II emplearemos el diseo del decodificador BCD a 7 segmentos que realizamos unos captulos atrs. Primero abriremos el archivo que lo contiene y posteriormente activaremos el compilador. Ahora decidiremos el tipo de simulacin que se va a realizar, ya sea funcional o simulacin con retardos de propagacin en los componentes lgicos empleados en la sintaxis del diseo. En la barra de men principal encontramos un men desplegable con el nombre de PROCESSING. Al abrirlo encontramos las posibles opciones de compilacin. Para una simulacin funcional , activamos la opcin FUNCIONAL SNF EXTRACTOR , tal y como se muestra en la figura:

33

DISEO DE SISTEMAS DIGITALES

Y el compilador queda con la siguiente apariencia:

4.2.- FICHEROS GRFICOS PARA SIMULACIN.

Vamos a partir de un proyecto que ya haya sido compilado con xito para proceder posteriormente a la creacin de un fichero de estmulos y asociar estos a las correspondientes entradas o salidas de nuestro diseo. Los ficheros grficos de simulacin son los ms fciles de estudiar ya que estamos ms acostumbrados a este tipo de seales (ORCAD) que las generadas por un archivo de texto. Para crear un fichero grfico que contenga los estmulos de entrada salida, establecemos el proyecto de trabajo, con el diseo a comprobar, en el directorio en curso.

34

DISEO DE SISTEMAS DIGITALES

A continuacin seleccionamos en el men principal la opcin FILE, NEW y una vez all la opcin de WAVEFORM EDITOR FILE, tal y como se muestra en la figura:

Al aceptar esta opcin nos encontraremos con una pantalla como esta:

El siguiente paso ser definir en qu terminales vamos a introducir seales de simulacin. Para ello , en el men principal activamos la opcin NODE , ENTER NODES FROM SNF y aparecer la siguiente pantalla:

35

DISEO DE SISTEMAS DIGITALES

Arriba a la derecha pulsamos el botn LIST y nos aparecern todos los terminales que hayan sido declarados en el diseo del circuito (GDF). En la siguiente figura vemos el ejemplo del decodificador BCD a 7 segmentos que diseamos anteriormente mediante circuitos combinacionales y que posteriormente se integr en un bloque.

Podemos observar que el programa nos muestra directamente la seales de entrada y de salida claramente identificadas para que nosotros a continuacin slo tengamos que asignar una de ellas a cada canal de simulacin:

36

DISEO DE SISTEMAS DIGITALES

Los nodos terminales que llevan consigo la letra (I) son de entrada y los que tienen la (O) son de salida. Seleccionamos, por ejemplo, el nodo d(I) de la lista que nos ofrecen y pulsamos el botn => del centro de la pantalla para confirmar su seleccin. A continuacin ste nodo se activar en la lista de nodos seleccionados. Repetimos estos pasos para todas las entradas del decodificador. Tras realizar esta operacin pulsamos el botn OK y los nodos estarn entonces representados en la pantalla principal en forma de ejes de abcisas en los que podremos componer las seales mediante el simulador grfico, emplazando las seales por cada canal de simulacin como si se tratase de un osciloscopio digital en el que se introducen las entradas procedentes de un emulador digital. Estas referencias de diseo abarcan todos y cada uno de las entradas o salidas seleccionadas anteriormente, tal y como se muestra en la figura de la pgina siguiente. Existe tambin la posibilidad de emular los Bits o palabras (Bytes) del contenido que se situara en una memoria del tipo RAM ROM de las que se incluyen en la librera, de forma que se podra simular la entrada o salida de datos a uno de estos elementos con las dos opciones situadas en la parte derecha del tipo de nodo.

37

DISEO DE SISTEMAS DIGITALES

4.3.- DEFINICIN DE ESTMULOS

La primera operacin a efectuar es delimitar el tiempo total de simulacin. Seleccionamos en el men FILE la opcin END TIME y nos aparecer por defecto el tiempo de 1 microsegundo en la siguiente pantalla:

Escribimos el valor del tiempo de ejecucin del sistema en la simulacin, dependiendo de cada diseo en particular. Para el ejemplo que estamos ilustrando en este manual de trabajo, seleccionamos el tiempo de 10 s y pulsamos el botn OK.

38

DISEO DE SISTEMAS DIGITALES

A continuacin adaptamos la rejilla y los valores de sta. En el men OPTIONS tenemos que tener activado el SNAP TO GIRD y especificaremos el ancho de rejilla mediante la opcin GIRD SIZE... de ese mismo men. Aparecer entonces la siguiente pantalla en donde actualizaremos el valor que queramos para la rejilla:

En principio podemos dejar este valor que aparece en la pantalla ya que no provocar que sea demasiado densa ni muy extendida, sino equilibrada con respecto al tiempo lmite de simulacin que especificamos anteriormente. Para otro tipo de simulacin realizada por el alumno, los tiempos totales y las divisiones del mismo sern fijadas en cada caso, dependiendo de la aplicacin a simular y a las condiciones de diseo y funcionamiento de la misma.

4.3.1.- DEFINICIN DE SEALES.

En este apartado vamos a realizar las simulacin de seales cuadradas de factor de servicio del 50%, ptimas para el ejemplo del decodificador y punto de partida para que ele alumno pueda desarrollar el resto de seales que sean tiles para su propio modelo de simulacin. Partiendo de la pantalla principal del simulador lgico, seleccionamos sobre el campo VALUE de la seal de entrada d del decodificador y a continuacin pulsamos el icono situado en la barra de herramientas de la izquierda que tiene la siguiente forma fsica: Con ello se activar la pantalla siguiente :

Estos son los valores que aparecen por defecto y que tienen que ver con los parmetros de la rejilla que definimos anteriormente. Si queremos que la frecuencia vare slo tenemos que modificar el valor de multiplicacin que est a mano derecha.

39

DISEO DE SISTEMAS DIGITALES

Con ello formaremos las seales de diferente periodo, tal y como se indica en la figura:

Realizamos este proceso multiplicando las seales de entrada por 2, 4, y 8 respectivamente, de forma que tengamos un cdigo binario natural aplicado a las entradas del decodificador, tal y como se indica en la siguiente tabla:

NUMERO CODIFICACION REPRESENTADO BINARIA 0 0000 1 0001 2 0010 3 0011 4 0100 5 0101 ...... ...... 14 1110 15 1111

40

DISEO DE SISTEMAS DIGITALES

La seal generada queda as:

En el caso de que la seal a crear sea para un BUS, los pasos sern muy similares al de una seal sencilla, salvo que para asignar el valor a la misma, emplearemos el comando EDIT, OVERWRITE, COUNT VALUE.... Y la pantalla que aparecer ser la siguiente:

41

DISEO DE SISTEMAS DIGITALES

Finalmente aadiremos los valores que vayamos a emplear y aceptaremos el cambio en las opciones. Existen otros tipos de ficheros de estmulos basados en programas de texto muy similares a los descritos en el apartado VHDL, pero no van a ser objeto de estudio en este manual.

4.4.- PUESTA EN MARCHA DE LA SIMULACIN.

Tras definir el archivo que contiene las seales que sern simuladas posteriormente, hay que guardar ste con el mismo nombre que tenga el proyecto en curso . De lo contrario no ser capaz de encontrarlo al realizar la simulacin y dar un mensaje de error. Para realizar esta operacin correctamente, activamos en el men principal la siguiente secuencia de operaciones: FILE, SAVE AS y despus seleccionamos el mismo nombre que el fichero del proyecto y la extensin SNF de entre las opciones disponibles, que corresponde a un fichero grfico de estmulos o seales (Waveform editor file). El siguiente paso ser activar el simulador. Bien desde los iconos de la barra de herramientas superior o desde el men desplegable de Max+plus II situado a la izquierda, arriba. En cualquiera de los dos casos aparecer la siguiente pantalla:

IMPORTANTE: La opcin USE DEVICE no debe estar seleccionada para realizar la simulacin . En caso contrario aparecer el siguiente mensaje de error:

42

DISEO DE SISTEMAS DIGITALES

Una vez tenido en cuenta este importante detalle, el siguiente paso a dar es iniciar la simulacin pulsando el botn START de la pantalla del simulador. Arranca en ese momento el compilador del sistema de simulacin y al finalizar sta podemos encontrar dos posibilidades. Una de ellas es que todo el proceso se haya desarrollado satisfactoriamente y aparezca la siguiente pantalla:

La segunda posibilidad es que exista algn error en la simulacin, en cuyo caso aparecer esta misma pantalla, pero se indicarn en ella los errores o advertencias que se detectaron en el proceso de simulacin. Si acudimos a la ayuda existente en dicha ventana localizamos el error y lo solucionamos. Una vez repasados los errores comprobamos el funcionamiento en la pantalla del simulador de seales:

43

DISEO DE SISTEMAS DIGITALES

5.- LENGUAJES HDL.

Las siglas HDL (Hardware Description Lenguages) nos definen un lenguaje de especificacin de hardware que es empleado para el diseo, de manera alternativa a lo visto en los captulos anteriores, de forma que se realiza el proceso de diseo, comprobacin y simulacin de forma homloga a la captura o dibujo de esquemas de circuitos digitales. Existen dos variantes de este lenguaje que son empleadas por el software de ALTERA y que van a ser descritas a continuacin:

VHDL.- Es un lenguaje empleado en los entornos EDA que tiene un propsito general y

mantiene una alta compatibilidad con los diseos realizados sobre distintas plataformas ya que sus ficheros son identificados y aceptados por cualquier programa de diseo. Esto se debe a que este lenguaje ha sido normalizado por la IEEE.

AHDL.- Este otro lenguaje es ms particular del entorno EDA de ALTERA y slo vale

para ste. Plantea una ventaja frente al VHDL, que por su parte es muy verstil, pero muy complicado de manejar y dominar. El AHDL resulta ms sencillo de aprender por el alumno y ste puede emplearlo como base para estudiar otros lenguajes de este tipo de mayor nivel de dificultad. El nico inconveniente que plantea es que no es compatible con ninguna otra plataforma de diseo que no sea ALTERA.

5.1.- REALIZACIN PRCTICA DE CIRCUITOS MEDIANTE EL LENGUAJE HDL.

Continuando con el ejemplo que vimos en los captulos anteriores o comenzando otro proyecto de diseo diferente, los pasos que tenemos que dar para definir un fichero HDL en cualquiera de sus dos versiones (VHDL AHDL), son: 1.- Seleccionar un proyecto de trabajo en el que se desee crear el fichero. 2.- Crear un fichero de diseo dentro de ese proyecto. 3.- Escribir el cdigo de programa y la descripcin del mismo. 4.- Comprobar el fichero de diseo que hemos creado. 5.- Solucionar los posibles fallos encontrados y simular el diseo.

44

DISEO DE SISTEMAS DIGITALES

Siguiendo estos cinco sencillos pasos, el alumno ser capaz de crear un fichero en alguno de los lenguajes HDL y hacer una descripcin de hardware en dicho cdigo y comprobar su funcionamiento por distintos mtodos, entre ellos la simulacin lgica, vista en el captulo anterior y de una gran utilidad tanto para el estudiante como para los diseadores profesionales.

5.1.1.- SELECCIN DEL PROYECTO DE TRABAJO Y CREACIN EL FICHERO HDL.

En primer lugar y siguiendo los pasos establecidos anteriormente, hay que abrir un nuevo archivo de edicin de texto para trabajar sobre l. Se har mediante el men FILE, en la opcin NEW, seleccionando las opciones que se han indicado en la siguiente imagen:

Una vez aceptada la pantalla anterior, nos encontramos con una ventana de edicin de texto como la mostrada en la siguiente figura:

45

DISEO DE SISTEMAS DIGITALES

Ahora para convertir este fichero de texto a otro de la forma VHD, tenemos que guardar el fichero mediante el men FILE, SAVE AS, teniendo en cuenta que la extensin tiene que ser para un archivo de la forma VHDL, como se muestra a continuacin:

(Nombre del fichero ) . vhd

Ya que el propio programa tendera a salvarlo por defecto con la extensin tdf que como vimos al principio de este documento, se corresponda con los archivos de AHDL. La pantalla empleada para esta funcin es la siguiente:

5.1.2.- CREAR UN FICHERO DE DISEO.

Como parte del ejercicio que estamos realizando, vamos a hacer el decodificador de BCD a 7 segmentos y lo incluiremos posteriormente en el diseo efectuado al principio, en sustitucin del integrado que fue empleado en captulos anteriores y diseado mediante un circuito combinacional. En primer lugar tenemos que realizar las descripciones que son posibles sintetizar en VHDL mediante el ejemplo descrito, y posteriormente, en el editor de texto que abrimos antes realizaremos el programa que definir el decodificador en el lenguaje HDL. Este fichero tendr que conservar el nombre de la entidad de programacin. Durante todas las operaciones de esta creacin del archivo, si alguna de las terminologas empleadas o conceptos descritos no se ha desarrollado con la suficiente claridad, el alumno puede encontrar informacin complementaria en los archivos de ayuda de que dispone el programa de ALTERA en la carpeta de ayuda de VHDL que encontrar en el men principal de Ayuda (HELP).

46

DISEO DE SISTEMAS DIGITALES

5.1.2.1.- INTERFACE DEL DISPOSITIVO Y DECLARACIN DE ENTIDAD.

A continuacin se va a describir, dentro de este lenguaje, el nombre de los dispositivos con sus entradas y salidas, puertos y declaracin de entidades mediante la siguiente sintaxis:

ENTITY PORT (

(Nombre del dispositivo) IS

[Lista de puertos de entrada] [Lista de puertos de bidireccionales ] [Lista de puertos de salida] [Lista de puertos de salida] END (Nombre de dispositivo)

: IN : INOUT : OUT : BUFFER

[Tipo de dato] ; [Tipo de dato] ; [Tipo de dato] ; [Tipo de dato] ;

Las normas principales que tenemos que observar a la hora de realizar nuestro diseo son: El nombre asignado al campo ENTITY debe coincidir con el fichero empleado para la edicin que hemos asignado en los pasos anteriores, en caso contrario no podr compilar el archivo. Para los nombres de los puertos definiremos etiquetas alfanumricas que no coincidan con los elementos de sintaxis definidos por el programa para operaciones. Una vez que terminemos el diseo, estos nombres sern asignados a cada uno de los terminales del circuito y podrn dar lugar a conflicto con el programador a la hora de volcar los datos a la tarjeta de la FPGA. El flujo de entrada o salida que tienen cada uno de los terminales que hemos asignado puede ser unidireccional (Entrada salida) o bidireccional. La descripcin de cada una de las funciones de los puertos ser efectuada posteriormente. Los datos que van a recibir o enviar estos puertos deben ser definidos en tres grandes grupos: Variables, constantes y seales. Este tratamiento especfico nos permitir asignar operadores aritmtico-matemticos, lgicos (binarios o en matriz) o de conversin a cada terminal, dependiendo de su funcionalidad. Para el caso de que los datos a manejar sean seales, el lenguaje VHDL nos permite clasificarlos de otras dos formas: BIT y BIT_VECTOR, dependiendo del tamao del array o bus que se asigna a dicho elemento de entrada /salida / bidireccional, ya que si ste puede ser de un solo bit o de 4, 8, etc.

47

DISEO DE SISTEMAS DIGITALES

Dentro de las ayudas que facilita el programa se encuentran una serie de plantillas de las estructuras ms comnmente empleados en la programacin con VHDL. Para activarla seleccionamos en el men TEMPLATES la opcin que afecta al lenguaje de programacin que estemos empleando, tal y como se puede ver en la figura, pero seleccionando VHDL.

Posteriormente, el volver a esa misma opcin del men principal, lo que nos encontremos ser la siguiente ventana, en donde encontraremos una plantilla para cada uno de los siguiente casos posibles:

Por ejemplo, seleccione de la opcin Library Clause, posteriormente acepte. Repita los pasos anteriores para los casos: Use clause y Entity declaration.

48

DISEO DE SISTEMAS DIGITALES

Al realizar esta operacin aparecer en el editor de texto el cuadro de opciones que estbamos describiendo en las pginas anteriores, en donde podemos rellenar los datos que nos hagan falta sustituyendo las condiciones adecuadas para el ejemplo que se esta siguiendo, tal y como se muestra en las dos siguientes figuras:

Completando la plantilla descrita con los datos de programacin del decodificador, tal y como se muestra en la siguiente figura:

49

DISEO DE SISTEMAS DIGITALES

Se emplearn las letras maysculas para los comandos de funcin y las minsculas para los nombres de archivos y dispositivos auxiliares. Adems, para estos ltimos se emplea un color negro, y para los primeros el color azul que identifica automticamente nombre. Una vez definido el comienzo del programa, procederemos a definir las especificaciones de funcionamiento a travs de una serie de cuerpos de arquitectura . Podemos encontrar varios de stos dentro de un mismo componente ya que pueden existir pequeas modificaciones en el funcionamiento o diferencias de comportamiento por distintos por tener diferentes arquitecturas para simulacin y para sntesis. Para estas descripciones emplearemos los PROCESOS que utilizan los algoritmos o funciones que nos permiten determinar el valor de las salidas en funcin del valor que tomen las variables de entrada al circuito o las de control si es que se han especificado estas ltimas. Al igual que en el paso anterior, existe una plantilla que nos va a permitir facilitar la tarea de asignar la sintaxis adecuada al proceso de programacin:

ARCHITECTURE [nombre de arquitectura] OF [nombre de entidad] IS SIGNAL __signal_name : STD_LOGIC; SIGNAL __signal_name : STD_LOGIC; BEGIN -- Process Statement -- Concurrent Procedure Call -- Concurrent Signal Assignment -- Conditional Signal Assignment -- Selected Signal Assignment -- Component Instantiation Statement -- Generate Statement END [nombre de arquitectura]; Zona de descripcin

Zona de declaracin

El nombre que empleamos para la arquitectura hace referencia a la estructura o funcionamiento de la misma.

50

DISEO DE SISTEMAS DIGITALES

En la zona de declaracin, que se encuentra debajo del nombre de la arquitectura, se emplea para realizar las declaraciones de la unidad, especificando las seales, tipos de datos, subprogramas y componentes que vayan a ser empleados posteriormente en la descripcin que empieza despus del comando BEGIN y donde escribiremos el cdigo que describa el funcionamiento del circuito especificado. Para describir la funcionalidad del circuito combinacional que estamos empleando, elaboraremos el PROCESO que ser sensible a todas las seales de entrada y salida y nos asignar a las salidas la combinacin, adecuada en cada caso, de las seales de entrada al circuito. El proceso tiene esta estructura:

__process_label: PROCESS (__signal_name, __signal_name, __signal_name) VARIABLE __variable_name : STD_LOGIC; VARIABLE __variable_name : STD_LOGIC; BEGIN -- Signal Assignment Statement -- Variable Assignment Statement -- Procedure Call Statement Zona de descripcin -- If Statement -- Case Statement -- Loop Statement END PROCESS __process_label;

Zona de declaracin

Ahora que ya se conoce la estructura sintctica de alguno de los componentes bsicos de un archivo VHDL, completaremos los datos correspondientes al diseo del alumno de un decodificador BCD a 7 segmentos, tal y como se detalla a continuacin. En el archivo de texto que se haba abierto con el nombre decobcd7seg tras la declaracin de entidad vista anteriormente se sita la cabecera de arquitectura, completndola como se indica en el ejemplo.

51

DISEO DE SISTEMAS DIGITALES

Se aade a continuacin el proceso que tenga todas las seales de entrada y describa el algoritmo de funcionamiento o tabla de verdad del decodificador buscado, empleando una sentencia adecuada como es CASE, conocida en varios lenguajes de programacin.

ARCHITECTURE funcional OF decobcd7seg IS BEGIN PROCESS (a,b,c,d) VARIABLE index : STD_LOGIC_VECTOR (3 DOWNTO 0); BEGIN index := d & c & b & a ; CASE index IS WHEN 0000 => S <= 1111110; WHEN 0001 => S <= 1101101; WHEN 0010 => S <= 1111101; WHEN 0011 => S <= 1111001; WHEN 0100 => S <= 0110011; WHEN 0101 => S <= 1011011; WHEN 0110 => S <= 1011111; WHEN 0111 => S <= 1100000; WHEN 1000 => S <= 1111111; WHEN 1001 => S <= 1110011; WHEN OTHERS => S <= 0000000; END CASE; END PROCESS;

END funcional;

Ahora se comprueba que ha sido introducido el cdigo de programa satisfactoriamente mediante la comprobacin del compilador. Para ello se presiona las teclas CTRL + K y ste arrancar.

52

DISEO DE SISTEMAS DIGITALES

Si se produce algn error en el proceso nos lo comunicar y lo solucionaremos. En caso de que se haya completado con xito la compilacin, cerramos la ventana del compilador. En este momento el programa habr creado un smbolo para este nuevo mdulo. Este lo podremos encontrar abriendo el fichero decobcd7seg.sym mediante el men principal de archivos.

Y el smbolo que se ha creado es el mostrado en la figura:

53

DISEO DE SISTEMAS DIGITALES

Una vez que hemos visto el smbolo creado mediante el programa, comprobamos si las especificaciones iniciales que tenamos de dicho componente se asocian con la realidad que estamos visualizando. En caso contrario, realizaremos las modificaciones del smbolo del mdulo VHDL mediante la edicin del archivo de texto decobcd7seg.vhd. Vamos a convertir el vector de salidas en elementos individuales, asignando cada uno de los segmentos de visualizador a uno de los terminales de salidas del decodificador creado. Modificamos y aadimos la siguiente secuencia de cdigo al programa: LIBRARY ieee; USE ieee.std_logic_1164.ALL, ieee.std_logic_arith.ALL;

ENTITY decobcd7seg IS PORT( a,b,c,d : IN STD_LOGIC; sa,sb,sc,sd,se,sf,sg : OUT STD_LOGIC; ); END decobcd7seg;

ARCHITECTURE funcional OF decobcd7seg IS BEGIN PROCESS (a,b,c,d) VARIABLE index : STD_LOGIC_VECTOR (3 DOWNTO 0); VARIABLE S: STD_LOGIC_VECTOR (6 DOWNTO 0); BEGIN index := d & c & b & a ; CASE index IS WHEN "0000" => S := "1111110"; WHEN "0001" => S := "1101101"; WHEN "0010" => S := "1111101"; WHEN "0011" => S := "1111001"; WHEN "0100" => S := "0110011"; WHEN "0101" => S := "1011011"; WHEN "0110" => S := "1011111"; WHEN "0111" => S := "1100000";

54

DISEO DE SISTEMAS DIGITALES

WHEN "1000" => S := "1111111"; WHEN "1001" => S := "1110011"; WHEN OTHERS => S := "0000000"; END CASE; sa <= S(6); sb <= S(5); sc <= S(4); sd <= S(3); se <= S(2); sf <= S(1); sg <= S(0); END PROCESS; END funcional; Al compilar el archivo de texto mediante la orden CTRL + K y verificar que no han existido errores, se procede a actualizar los puertos, abriendo el fichero que corresponde al smbolo creado. Al realizar esta operacin nos damos cuenta de que no han sido actualizados los puertos del mismo y continan siendo los del caso anterior. Para solucionar este problema se activa la opcin del men FILE; CREATE DEFAULT SYMBOL y en ella se confirma la actualizacin de dicho puerto. Para ello aparecer la siguiente pantalla que debemos aceptar en caso de que sea correcta la actualizacin que vamos a emplear:

Esta opcin modifica el smbolo anterior y lo convierte al nuevo. Y tras aceptar esta opcin el programa genera el smbolo:

Al abrir el archivo decobcd7seg.sym podemos ver que los cambios han sido efectuados, tal y como se puede ver en la siguiente imagen:

55

DISEO DE SISTEMAS DIGITALES

Estos pasos debern efectuarse tantas veces como sea necesario para que quede cambiado el smbolo con las distintas modificaciones que realicemos sobre l.

5.2.- LIBRERIAS VHDL DE USUARIO.

La primera condicin que debemos cumplir para emplear las libreras VHDL es que stas estn incluidas en el directorio del proyecto con el que estamos trabajando. Una vez que se cumple esta primera condicin, para poder manejar una librera en el diseo en el que trabajemos, activamos el compilador, seleccionamos la opcin INTERFACES de la barra de men principal y posteriormente en el men desplegable la opcin VHDL NETLIST READING SETTINGS... con lo que aparecer la siguiente ventana:

56

DISEO DE SISTEMAS DIGITALES

Escribimos en las casillas correspondientes al nombre de la librera y al directorio que la contiene y pulsamos el botn ADD, con lo que la librera quedar aadida al proyecto actual y ser posible acceder a ella en el transcurso del diseo. Si hace falta alguna librera ms, el alumno podr repetir estos pasos y aadir las libreras necesarias, bien las existentes en el entorno MAX+PLUS II o las creadas por l mismo.

5.3.- INTEGRACIN DE MDULOS VHDL EN ESQUEMAS.

Estos mdulos que han sido descritos en los apartados anteriores pueden insertarse en cualquier esquema que se realice, para ello, desde el directorio donde se encuentre asignado el proyecto en curso, se inserta el mdulo VHDL necesario y se emplean sus terminales de entrada/salida segn los requerimientos de diseo. Posteriormente se guarda el esquema finalizado y se comprueba su funcionamiento mediante el compilador y el programador, tal y como se defini en captulos anteriores.

57

También podría gustarte

- Contrato InformaticoDocumento7 páginasContrato InformaticosamAún no hay calificaciones

- 2 Costo Del ProductoDocumento17 páginas2 Costo Del ProductoJuan RamosAún no hay calificaciones

- Guia Rapida S7-300Documento11 páginasGuia Rapida S7-300Valentín García ÁngelesAún no hay calificaciones

- Informe Practicas Emsamble y MantenimientoDocumento24 páginasInforme Practicas Emsamble y Mantenimientoandres021_saenzAún no hay calificaciones

- Comparación de Tecnologías TTL y CMOSDocumento3 páginasComparación de Tecnologías TTL y CMOSBrayan Ulises Lopez Lugo100% (3)

- Instalación y Utilización Sepam 2000 PDFDocumento126 páginasInstalación y Utilización Sepam 2000 PDFPaco100% (1)

- 12 Sistemas CombinacionalesDocumento6 páginas12 Sistemas CombinacionalesJuan RamosAún no hay calificaciones

- 10 CompuertasLogicasDocumento29 páginas10 CompuertasLogicasJuan RamosAún no hay calificaciones

- 8 Sistema OctalDocumento1 página8 Sistema OctalJuan RamosAún no hay calificaciones

- 11 Operaciones BinariasDocumento15 páginas11 Operaciones BinariasJuan RamosAún no hay calificaciones

- 6 Electrónica DigitalDocumento16 páginas6 Electrónica DigitalJuan RamosAún no hay calificaciones

- 7 Qué Es Six SigmaDocumento21 páginas7 Qué Es Six SigmaJuan RamosAún no hay calificaciones

- 6 Poka-YokeDocumento19 páginas6 Poka-YokeJuan RamosAún no hay calificaciones

- 4 Norma ISODocumento25 páginas4 Norma ISOJuan RamosAún no hay calificaciones

- 1 Fundamentos de ManufacturaDocumento22 páginas1 Fundamentos de ManufacturaJuan RamosAún no hay calificaciones

- 2 Reglas Rígidas y FlexómetrosDocumento24 páginas2 Reglas Rígidas y FlexómetrosJuan RamosAún no hay calificaciones

- Mundo de MicrocontroladoresDocumento328 páginasMundo de MicrocontroladoresAlbert CarlosAún no hay calificaciones

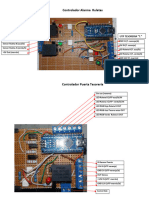

- Controlador Alarma RuletasDocumento6 páginasControlador Alarma RuletasMarcelo Estigarribia CymAún no hay calificaciones

- S03.s6 - MaterialDocumento19 páginasS03.s6 - MaterialCyntia peredaAún no hay calificaciones

- Practica 2Documento7 páginasPractica 2gestradag-1Aún no hay calificaciones

- Monitorizacion y Optimizacion Del RendimientoDocumento39 páginasMonitorizacion y Optimizacion Del RendimientoalbertoAún no hay calificaciones

- Informe VacacionesDocumento4 páginasInforme VacacionesCarlos Anzola100% (1)

- Eje 4 - Plan de MejoramientoDocumento15 páginasEje 4 - Plan de MejoramientoDaniel Alejandro Acosta OssaAún no hay calificaciones

- Protocolo de Venta Ideal Postpago y Enfoque Terminales 2509 - GGSSDocumento17 páginasProtocolo de Venta Ideal Postpago y Enfoque Terminales 2509 - GGSSJunior AlReAún no hay calificaciones

- 1.microcontrolador Embebido en FPGADocumento14 páginas1.microcontrolador Embebido en FPGAJonny Piñeros CastañedaAún no hay calificaciones

- Monitor de Translado y Modulos-ManualDocumento20 páginasMonitor de Translado y Modulos-ManualMiris RebollarAún no hay calificaciones

- Actividad 3 Caso de EstudioDocumento3 páginasActividad 3 Caso de EstudioEdwin Jesus Micolta FernandezAún no hay calificaciones

- Diseno y Automatizacion de Un Sistema de Riego Hidroponico 41Documento60 páginasDiseno y Automatizacion de Un Sistema de Riego Hidroponico 41hl0963988Aún no hay calificaciones

- DSP CNCDocumento6 páginasDSP CNCJuan Carlos CosmeAún no hay calificaciones

- La Memoria ROMDocumento2 páginasLa Memoria ROMLUIS ALBERTO CAMAYO ERAZOAún no hay calificaciones

- Modelo de ProyectoDocumento53 páginasModelo de ProyectoARMANDO ACUÑAAún no hay calificaciones

- InformeDocumento44 páginasInformejoseAún no hay calificaciones

- Historia de Los SODocumento1 páginaHistoria de Los SOJENNY HUANCA ANQUISEAún no hay calificaciones

- Evaluación Diagnóstica 4° MedioDocumento7 páginasEvaluación Diagnóstica 4° MedioCurihuinca Escobar ArmandoAún no hay calificaciones

- Act 3-2Documento1 páginaAct 3-2Aby Manoban100% (2)

- Temas Generales de La Memoria SDDocumento12 páginasTemas Generales de La Memoria SDjoseAún no hay calificaciones

- Educacion en Nuevas Tecnologias: Modulo 1 Y 2 1 DivisionDocumento6 páginasEducacion en Nuevas Tecnologias: Modulo 1 Y 2 1 Divisionno MolinaAún no hay calificaciones

- DDR4Documento7 páginasDDR4Manuel SalazarAún no hay calificaciones

- Instalacion de Windws 10Documento16 páginasInstalacion de Windws 10jorgeAún no hay calificaciones

- Guia de Instalacion SoftRest MovilDocumento22 páginasGuia de Instalacion SoftRest MovilJorge Luis Rojas VillaltaAún no hay calificaciones

- Easy PeasyDocumento10 páginasEasy Peasyapi-270580220Aún no hay calificaciones