Documentos de Académico

Documentos de Profesional

Documentos de Cultura

DMA

Cargado por

Alain NicolásDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

DMA

Cargado por

Alain NicolásCopyright:

Formatos disponibles

CONCEPTO

(Direct Memory Access o DMA). El acceso directo a memoria es una caracterstica de las computadoras y microprocesadores modernos que permite que ciertos subsistemas de hardware dentro de la computadora puedan acceder a la memoria del sistema para la lectura y/o escritura, independientemente de la unidad central de procesamiento (CPU). De lo contrario, la CPU tendra que copiar cada porcin de dato desde el origen hacia el destino, haciendo que sta no est disponible para otras tareas. Los subsistemas de hardware que utilizan DMA pueden ser: controladores de disco duro, tarjetas grficas, tarjetas de red, tarjetas de sonido y tarjetas aceleradoras. Tambin es utilizado para la transferencia de datos dentro del chip en procesadores con mltiples ncleos. DMA es esencial en los sistemas integrados.

Referencia: http://www.alegsa.com.ar/Dic/acceso%20directo%20a%20memoria.php

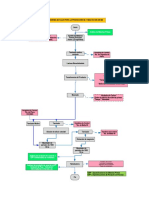

FUNCIONAMIENTO.

El mecanismo de acceso directo a memoria DMA es bastante complejo en sus detalles, y por supuesto, el movimiento de grandes volmenes de datos entre memoria y un dispositivo requiere cierta intervencin del procesador. El movimiento se hace a rfagas, y cada transferencia se inicia con una interrupcin que obliga al procesador a suspender su tarea para permitir un nuevo intercambio. Proceso. Empezaremos sealando que el DMA permite mover datos entre un puerto y memoria, o entre memoria y un puerto, pero no entre dos puertos o entre dos posiciones de memoria. Como veremos a continuacin, cada transferencia DMA requiere cierta preparacin previa; conocer el volumen de datos a transferir (la ms simple es de 1 byte) y la direccin de inicio del bfer de memoria involucrado (del que se leern los datos o donde se escribirn). Para esto dispone de dos registros para cada lnea; el contador y el registro de direcciones. Segn se refieran a operaciones de lectura (memoria dispositivo) o escritura (dispositivo memoria) reciben distintos nombres porque su significado difiere: Escritura: Direccin de inicio ("Write starting address"). Contador ("Write starting word count") Lectura: Direccin actual de lectura ("Read current address"). Contador ("Read remaining word count")

Despus de cada transferencia (de 1 byte) el registro de direcciones del DMAC es incrementado en una unidad, y el contador es disminuido en una unidad. Cuando este ltimo llega a cero, la transferencia ha concluido, el DMAC pone en nivel alto la lnea T/C ("Terminal Count") en el bus de control y procede a enviar al procesador la seal EOP ("End of Process"). A partir de este momento el controlador no puede realizar otra transferencia hasta que sea programado de nuevo por la UCP. Aunque existen varios canales, el sistema de prioridades garantiza que solo uno de ellos puede estar en funcionamiento cada vez, de forma que sus funcionamientos no pueden solaparse, y la seal EOP se refiere forzosamente al canal activo en ese momento.

Referencia: http://zator.com/Hardware/H2_3.htm

MODOS DE OPERACIN.

* DMA por robo de ciclo: es uno de los mtodos ms usados, ya que requiere poca utilizacin del CPU. Esta estrategia utiliza uno o ms ciclos de CPU para cada instruccin que se ejecuta. Esto permite alta disponibilidad del bus del sistema para la CPU, aunque la transferencia de datos se har ms lentamente. * DMA por rfagas: esta estrategia consiste en enviar el bloque de datos solicitado mediante una rfaga empleando el bus del sistema hasta finalizar la transferencia. Permite una altsima velocidad, pero la CPU no podr utilizar el bus de sistema durante el tiempo de transferencia, por lo que permanece inactiva. * DMA transparente: esta estrategia consiste en emplear el bus del sistema cuando la CPU no lo necesita. Esto permite que la transferencia no impida que la CPU utilice el bus del sistema; pero la velocidad de transferencia es la ms baja posible. * DMA Scatter-gather: esta estrategia permite transmitir datos a varias reas de memoria en una transaccin DMA simple. Equivale al encadenamiento de mltiples peticiones DMA simples. Su objetivo es librar a la CPU la tarea de la copia de datos e interrupciones de entrada/salida mltiples.

También podría gustarte

- Caja de Cambios Automática EpicicloidalDocumento24 páginasCaja de Cambios Automática EpicicloidalAdriana Largo Lopez89% (9)

- Investigacion 2Documento12 páginasInvestigacion 2Alain NicolásAún no hay calificaciones

- Robotic ADocumento8 páginasRobotic AAlain NicolásAún no hay calificaciones

- Chipset AMD 990FXDocumento7 páginasChipset AMD 990FXAlain NicolásAún no hay calificaciones

- Expo Sic IonDocumento21 páginasExpo Sic IonAlain NicolásAún no hay calificaciones

- Electronika 2004Documento1 páginaElectronika 2004Alain NicolásAún no hay calificaciones

- Practica 2 Uso Del PotenciometroDocumento10 páginasPractica 2 Uso Del PotenciometroRafael GonzálezAún no hay calificaciones

- Pictogramas Segunda Parte PDFDocumento25 páginasPictogramas Segunda Parte PDFKimberlyNaomiMontesDeOcaRodriguez100% (2)

- FisicaModerna 31 PDFDocumento188 páginasFisicaModerna 31 PDFJose Abelardo Capuñay Gonzales100% (1)

- 0.0 - Resumen EjecutivoDocumento5 páginas0.0 - Resumen EjecutivoOsmar ACAún no hay calificaciones

- Examen de Fisica Primer Periodo Con RespuestasDocumento3 páginasExamen de Fisica Primer Periodo Con RespuestasDiego David Durán Espinoza100% (1)

- Resumen Sistemas Operativos DistribuidosDocumento50 páginasResumen Sistemas Operativos DistribuidosJuan Nieto100% (1)

- Proyecto de ElectromagnetismoDocumento4 páginasProyecto de ElectromagnetismoCristian AndresAún no hay calificaciones

- 10°-2021-Taller Intro Electrónica A-D 1 JULIANADocumento5 páginas10°-2021-Taller Intro Electrónica A-D 1 JULIANAsara lorena infante bordaAún no hay calificaciones

- LAB1 Circuitos TrifasicosDocumento10 páginasLAB1 Circuitos TrifasicosŠtiveņ ŌrjûëlaAún no hay calificaciones

- ASRock G31M-GS G31M S Placa Madre PDFDocumento12 páginasASRock G31M-GS G31M S Placa Madre PDFmibor2012Aún no hay calificaciones

- Interruptores Indisponibles y Con Anomalias en El SenDocumento13 páginasInterruptores Indisponibles y Con Anomalias en El SenEduardo PerezAún no hay calificaciones

- Practica 1 AnalogaDocumento2 páginasPractica 1 AnalogaCristhianGomezAún no hay calificaciones

- P4-OM Enlaces DiatDocumento11 páginasP4-OM Enlaces DiatCedric Omar Hdz RiescoAún no hay calificaciones

- CNC Controls Product Overview Es PDFDocumento11 páginasCNC Controls Product Overview Es PDFwinder portilloAún no hay calificaciones

- ALCANOSDocumento6 páginasALCANOSMaritza Garcia CanalesAún no hay calificaciones

- Catálogo de Dispositivos de Un Circuito DigitalDocumento12 páginasCatálogo de Dispositivos de Un Circuito DigitalXandher Asdrubal Benavides DiazAún no hay calificaciones

- L00439A GU Essential-Measurement-Techniques A4 ES LR PDFDocumento62 páginasL00439A GU Essential-Measurement-Techniques A4 ES LR PDFGloria J GonzálezAún no hay calificaciones

- Transistor Emisor ComúnDocumento11 páginasTransistor Emisor ComúnMario RojasAún no hay calificaciones

- Tarea 3 SDI-SDUDocumento7 páginasTarea 3 SDI-SDUEdwin Rafael Quintanilla Guillén100% (1)

- Informe de Averias en Los Smart TVDocumento11 páginasInforme de Averias en Los Smart TVHernan AlcalaAún no hay calificaciones

- Tipos de Union en AceroDocumento6 páginasTipos de Union en AceroJorge Diaz GalvezAún no hay calificaciones

- Errores Mundoclima 2017-Multi PDFDocumento129 páginasErrores Mundoclima 2017-Multi PDFErik CorralesAún no hay calificaciones

- Informe N7Documento4 páginasInforme N7ingeneria biotecnologicaAún no hay calificaciones

- PCD 01 18 01Documento1 páginaPCD 01 18 01Li RLAún no hay calificaciones

- Análisis de Lineas de Transmisión Con Parámetros ConcentradosDocumento7 páginasAnálisis de Lineas de Transmisión Con Parámetros ConcentradosPaul Nahuelovich PellikovAún no hay calificaciones

- Criterios para Ajuste en Reles de SincronizacionDocumento7 páginasCriterios para Ajuste en Reles de SincronizacionHamylto PamoAún no hay calificaciones

- Robot Seguidor de LíneasDocumento4 páginasRobot Seguidor de Líneasfabioluis12Aún no hay calificaciones

- Software PrivadoDocumento11 páginasSoftware Privadoaitor_tito928992Aún no hay calificaciones