Documentos de Académico

Documentos de Profesional

Documentos de Cultura

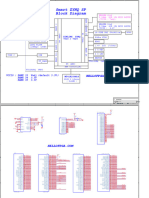

Smart ZYNQ SL Schematic 20230510

Cargado por

Satvik HardatDescripción original:

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Smart ZYNQ SL Schematic 20230510

Cargado por

Satvik HardatCopyright:

Formatos disponibles

5 4 3 2 1

D

Smart ZYNQ SL D

Block Diagram HEADER 20x2

2.54mm 40P (PL GPIO 36PIN)

BANK 33 BANK 35

(VCCIO : Vadj)

HEADER 20x2

BANK 0

2.54mm 40P (PL GPIO 36PIN)

JTAG VCCIO : 3.3V

1G GIGE PHY (Rtl8211e) RJ45

PL (FPGA)

PS (ARM)

C C

XINLINX ZYNQ

7010 / 7020 50Mhz XTAL

33.33Mhz XTAL

BANK 500

HDMI

QSPI FLASH

128Mbps (16MB) 2 X KEY

BANK 34

2 X LED

BANK 501

EEPROM

TF_CARD UART TYPE C

B B

PS (ARM)

DDR Controller

VCCIO : BANK 33 Vadj(default 3.3V)

HELLOFPGA.COM MT41K256M16 BANK 34 3.3V

256M X 16bits BANK 35 3.3V

( 512MB )

A A

Title

HELLOFPGA.COM

Size Document Number Rev

C <Doc> <RevCode>

Date: Wednesday, May 10, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

VCC3V3

R20

U33J

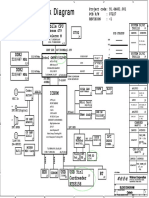

XC7Z020_CLG484

10k

VCC3V3

C9 PS_SRST_B

PS_SRST_B_501 F8

PS_MIO_VREF_501

R168 D6

U33A VCC3V3 10k PS_MIO16_501

E9

U33F PS_MIO17_501

A7

FPGA_TMS KEY3 SW PS_MIO18_501

N11 G12 E10

D DXP_0 TMS_0 FPGA_TCK PS_CLK_33.333M PS_MIO19_501 D

N12 G11 F7 A8

DXN_0 TCK_0 FPGA_TDI R446 PS_CLK_500 PS_POR_B C186 0.1uf PS_MIO20_501

H13 B5 F11

TDI_0 FPGA_TDO PS_POR_B_500 PS_MIO21_501

G14 A14

TDO_0 330R PS_MIO22_501

M11 E11

VREFP_0 DONE PS_MIO23_501

L12 T12 G6 B7

VREFN_0 DONE_0 VCC3V3 PS_MIO0_500 QSPI_CS PS_MIO24_501

A1 F12

R140 4.7k PS_MIO1_500 SPI_DQ0/MIO2 PS_MIO25_501

T11 A2 A13

PROGRAM_B_0 RED PS_MIO2_500 SPI_DQ1/MIO3 PS_MIO26_501

L11 F6 D7

VP_0 R141 4.7k LED3 PS_MIO3_500 SPI_DQ2/MIO4 PS_MIO27_501

M12 T14 E4 A12

VN_0 INIT_B_0 PS_MIO4_500 SPI_DQ3/MIO5 PS_MIO28_501

A3 E8

VCC3V3 VCC3V3 PS_MIO5_500 SPI_SCK/MIO6 PS_MIO29_501

A4 A11

PS_MIO6_500 VCFG0/MIO7 PS_MIO30_501

T13 T10 D5 F9

CFGBVS_0 RSVDVCC3 PS_MIO7_500 VCFG1/MIO8 PS_MIO31_501

T8 E5 C7

RSVDVCC2 PS_MIO8_500 PS_MIO32_501

T7 C4 G13

RSVDVCC1 PS_MIO9_500 PS_MIO33_501

VCC1V8 K11 G10 G7 B12

VCCADC_0 RSVDGND PS_MIO10_500 PS_MIO34_501

K12 B4 F14

GNDADC_0 PS_MIO11_500 PS_MIO35_501

C5 A9

PS_MIO12_500 PS_MIO36_501

A6 B14

PS_MIO13_500 PS_MIO37_501

B6 F13

PS_MIO14_500 PS_MIO38_501

XC7Z020_CLG484 E6 C13

PS_MIO15_500 PS_MIO39_501 SD_CLK

E14 22R R453

PS_MIO40_501 SD_CMD

C8

PS_MIO41_501 SD_D0

XC7Z020_CLG484 D8

PS_MIO42_501 SD_D1

B11

PS_MIO43_501 SD_D2

E13

PS_MIO44_501 SD_D3

B9

PS_MIO45_501 OTG_RST

D12

PS_MIO46_501 SD_CD

B10

PS_MIO47_501

D11

PS_MIO48_501

C14

PS_MIO49_501

D13

PS_MIO50_501

C10

PS_MIO51_501

D10

PS_MIO52_501

C12

PS_MIO53_501

C C

HELLOFPGA.COM

U33B

U33C U33D XC7Z020_CLG484 XC7Z020_CLG484 U33E

VCC3V3

R7 GPIO_R7 H15 GPIO_H15 H17 GPIO_H17

IO_0_13 GPIO_V10_L1P IO_0_34 GPIO_J15_L1P GPIO_U19 IO_0_35 GPIO_F16_L1P

V10 J15 U19 F16

IO_L1P_T0_13 GPIO_V9_L1N IO_L1P_T0_34 GPIO_K15_L1N R476 IO_0_33 GPIO_T21_L1P IO_L1P_T0_AD0P_35 GPIO_E16_L1N

V9 K15 T21 E16

IO_L1N_T0_13 GPIO_V8_L2P IO_L1N_T0_34 GPIO_J16_L2P IO_L1P_T0_33 GPIO_U21_L1N IO_L1N_T0_AD0N_35 GPIO_D16_L2P

V8 J16 1k U21 D16

IO_L2P_T0_13 GPIO_W8_L2N IO_L2P_T0_34 GPIO_J17_L2N IO_L1N_T0_33 GPIO_T22_L2P IO_L2P_T0_AD8P_35 GPIO_D17_L2N

W8 J17 T22 D17

IO_L2N_T0_13 GPIO_W11_L3P IO_L2N_T0_34 GPIO_K16_L3P IO_L2P_T0_33 GPIO_U22_L2N IO_L2N_T0_AD8N_35 GPIO_E15_L3P

W11 K16 U22 E15

IO_L3P_T0_DQS_13 GPIO_W10_L3N IO_L3P_T0_DQS_PUDC_B_34 GPIO_L16_L3N IO_L2N_T0_33 GPIO_V22_L3P IO_L3P_T0_DQS_AD1P_35 GPIO_D15_L3N

W10 L16 V22 D15

IO_L3N_T0_DQS_13 GPIO_V12_L4P IO_L3N_T0_DQS_34 GPIO_L17_L4P PL_UART_TX CH340_UART_RX IO_L3P_T0_DQS_33 GPIO_W22_L3N IO_L3N_T0_DQS_AD1N_35 GPIO_G15_L4P

V12 L17 W22 G15

IO_L4P_T0_13 GPIO_W12_L4N IO_L4P_T0_34 GPIO_M17_L4N PL_UART_RX CH340_UART_TX IO_L3N_T0_DQS_33 GPIO_W20_L4P IO_L4P_T0_35 GPIO_G16_L4N

W12 M17 W20 G16

IO_L4N_T0_13 GPIO_U12_L5P IO_L4N_T0_34 GPIO_N17_L5P IO_L4P_T0_33 GPIO_W21_L4N IO_L4N_T0_35 GPIO_F18_L5P

U12 N17 W21 F18

IO_L5P_T0_13 GPIO_U11_L5N IO_L5P_T0_34 GPIO_N18_L5N IO_L4N_T0_33 GPIO_U20_L5P IO_L5P_T0_AD9P_35 GPIO_E18_L5N

U11 N18 U20 E18

IO_L5N_T0_13 GPIO_U10_L6P IO_L5N_T0_34 GPIO_M15_L6P IO_L5P_T0_33 GPIO_V20_L5N IO_L5N_T0_AD9N_35 GPIO_G17_L6P

U10 M15 V20 G17

IO_L6P_T0_13 GPIO_U9_L6N IO_L6P_T0_34 GPIO_M16_L6N IO_L5N_T0_33 GPIO_V18_L6P IO_L6P_T0_35 GPIO_F17_L6N

U9 M16 V18 F17

IO_L6N_T0_VREF_13 GPIO_AA12_L7P IO_L6N_T0_VREF_34 GPIO_J18_L7P IO_L6P_T0_33 GPIO_V19_L6N IO_L6N_T0_VREF_35 GPIO_C15_L7P

AA12 J18 V19 C15

IO_L7P_T1_13 GPIO_AB12_L7N IO_L7P_T1_34 GPIO_K18_L7N IO_L6N_T0_VREF_33 GPIO_AA22_L7P IO_L7P_T1_AD2P_35 GPIO_B15_L7N

AB12 K18 AA22 B15

IO_L7N_T1_13 GPIO_AA11_L8P IO_L7N_T1_34 GPIO_J21_L8P HDMI_TX_TMDS_DAT2_P IO_L7P_T1_33 GPIO_AB22_L7N IO_L7N_T1_AD2N_35 GPIO_B16_L8P

AA11 J21 AB22 B16

IO_L8P_T1_13 GPIO_AB11_L8N IO_L8P_T1_34 GPIO_J22_L8N HDMI_TX_TMDS_DAT2_N IO_L7N_T1_33 GPIO_AA21_L8P IO_L8P_T1_AD10P_35 GPIO_B17_L8N

AB11 J22 AA21 B17

IO_L8N_T1_13 GPIO_AB10_L9P IO_L8N_T1_34 GPIO_J20_L9P KEY2 IO_L8P_T1_33 GPIO_AB21_L8N IO_L8N_T1_AD10N_35 GPIO_A16_L9P

AB10 J20 AB21 A16

IO_L9P_T1_DQS_13 GPIO_AB9_L9N IO_L9P_T1_DQS_34 GPIO_K21_L9N KEY1 IO_L8N_T1_33 GPIO_Y20_L9P IO_L9P_T1_DQS_AD3P_35 GPIO_A17_L9N

AB9 K21 Y20 A17

IO_L9N_T1_DQS_13 GPIO_Y11_L10P IO_L9N_T1_DQS_34 GPIO_L21_L10P HDMI_TX_TMDS_DAT1_P IO_L9P_T1_DQS_33 GPIO_Y21_L9N IO_L9N_T1_DQS_AD3N_35 GPIO_A18_L10P ETH_RXD1

Y11 L21 Y21 A18

IO_L10P_T1_13 GPIO_Y10_L10N IO_L10P_T1_34 GPIO_L22_L10N HDMI_TX_TMDS_DAT1_N IO_L9N_T1_DQS_33 GPIO_AB19_L10P IO_L10P_T1_AD11P_35 GPIO_A19_L10N ETH_RXD2

Y10 L22 AB19 A19

IO_L10N_T1_13 GPIO_AA9_L11P IO_L10N_T1_34 GPIO_K19_L11P IO_L10P_T1_33 GPIO_AB20_L10N IO_L10N_T1_AD11N_35 GPIO_C17_L11P

AA9 K19 AB20 C17

B IO_L11P_T1_SRCC_13 GPIO_AA8_L11N IO_L11P_T1_SRCC_34 GPIO_K20_L11N IO_L10N_T1_33 GPIO_Y19_L11P IO_L11P_T1_SRCC_35 GPIO_C18_L11N B

AA8 K20 Y19 C18

IO_L11N_T1_SRCC_13 GPIO_Y9_L12P IO_L11N_T1_SRCC_34 GPIO_L18_L12P IO_L11P_T1_SRCC_33 GPIO_AA19_L11N IO_L11N_T1_SRCC_35 GPIO_D18_L12P

Y9 L18 AA19 D18

IO_L12P_T1_MRCC_13 GPIO_Y8_L12N IO_L12P_T1_MRCC_34 GPIO_L19_L12N IO_L11N_T1_SRCC_33 GPIO_Y18_L12P IO_L12P_T1_MRCC_35 GPIO_C19_L12N

Y8 L19 Y18 C19

IO_L12N_T1_MRCC_13 GPIO_Y6_L13P IO_L12N_T1_MRCC_34 GPIO_M19_L13P CLK_50M IO_L12P_T1_MRCC_33 GPIO_AA18_L12N IO_L12N_T1_MRCC_35 GPIO_B19_L13P ETH_RXC

Y6 M19 AA18 B19

IO_L13P_T2_MRCC_13 GPIO_Y5_L13N IO_L13P_T2_MRCC_34 GPIO_M20_L13N IO_L12N_T1_MRCC_33 GPIO_W17_L13P IO_L13P_T2_MRCC_35 GPIO_B20_L13N ETH_RXD3

Y5 M20 W17 B20

IO_L13N_T2_MRCC_13 GPIO_AA7_L14P IO_L13N_T2_MRCC_34 GPIO_N19_L14P IO_L13P_T2_MRCC_33 GPIO_W18_L13N IO_L13N_T2_MRCC_35 GPIO_D20_L14P

AA7 N19 W18 D20

IO_L14P_T2_SRCC_13 GPIO_AA6_L14N IO_L14P_T2_SRCC_34 GPIO_N20_L14N IO_L13N_T2_MRCC_33 GPIO_W16_L14P IO_L14P_T2_AD4P_SRCC_35 GPIO_C20_L14N

AA6 N20 W16 C20

IO_L14N_T2_SRCC_13 GPIO_AB2_L15P IO_L14N_T2_SRCC_34 GPIO_M21_L15P HDMI_TX_TMDS_DAT0_P IO_L14P_T2_SRCC_33 GPIO_Y16_L14N IO_L14N_T2_AD4N_SRCC_35 GPIO_A21_L15P ETH_RXCTL

AB2 M21 Y16 A21

IO_L15P_T2_DQS_13 GPIO_AB1_L15N IO_L15P_T2_DQS_34 GPIO_M22_L15N HDMI_TX_TMDS_DAT0_N IO_L14N_T2_SRCC_33 GPIO_U15_L15P IO_L15P_T2_DQS_AD12P_35 GPIO_A22_L15N ETH_RXD0

AB1 M22 U15 A22

IO_L15N_T2_DQS_13 GPIO_AB5_L16P IO_L15N_T2_DQS_34 GPIO_N22_L16P HDMI_CLK_TX_TMDS_P IO_L15P_T2_DQS_33 GPIO_U16_L15N IO_L15N_T2_DQS_AD12N_35 GPIO_D22_L16P

AB5 N22 U16 D22

IO_L16P_T2_13 GPIO_AB4_L16N IO_L16P_T2_34 GPIO_P22_L16N HDMI_CLK_TX_TMDS_N IO_L15N_T2_DQS_33 GPIO_U17_L16P IO_L16P_T2_35 GPIO_C22_L16N

AB4 P22 U17 C22

IO_L16N_T2_13 GPIO_AB7_L17P IO_L16N_T2_34 GPIO_R20_L17P EEPROM_SCL IO_L16P_T2_33 GPIO_V17_L16N IO_L16N_T2_35 GPIO_E21_L17P ETH_TXD0

AB7 R20 V17 E21

IO_L17P_T2_13 GPIO_AB6_L17N IO_L17P_T2_34 GPIO_R21_L17N EEPROM_SDA IO_L16N_T2_33 GPIO_AA17_L17P IO_L17P_T2_AD5P_35 GPIO_D21_L17N ETH_TXC

AB6 R21 AA17 D21

IO_L17N_T2_13 GPIO_Y4_L18P IO_L17N_T2_34 GPIO_P20_L18P LED1 IO_L17P_T2_33 GPIO_AB17_L17N IO_L17N_T2_AD5N_35 GPIO_B21_L18P

Y4 P20 AB17 B21

IO_L18P_T2_13 GPIO_AA4_L18N IO_L18P_T2_34 GPIO_P21_L18N LED2 IO_L17N_T2_33 GPIO_AA16_L18P IO_L18P_T2_AD13P_35 GPIO_B22_L18N

AA4 P21 AA16 B22

IO_L18N_T2_13 GPIO_R6_L19P IO_L18N_T2_34 GPIO_N15_L19P IO_L18P_T2_33 GPIO_AB16_L18N IO_L18N_T2_AD13N_35 GPIO_H19_L19P

R6 N15 AB16 H19

IO_L19P_T3_13 GPIO_T6_L19N IO_L19P_T3_34 GPIO_P15_L19N IO_L18N_T2_33 GPIO_V14_L19P IO_L19P_T3_35 GPIO_H20_L19N

T6 P15 V14 H20

IO_L19N_T3_VREF_13 GPIO_T4_L20P IO_L19N_T3_VREF_34 GPIO_P17_L20P IO_L19P_T3_33 GPIO_V15_L19N IO_L19N_T3_VREF_35 GPIO_G19_L20P

T4 P17 V15 G19

IO_L20P_T3_13 GPIO_U4_L20N IO_L20P_T3_34 GPIO_P18_L20N IO_L19N_T3_VREF_33 GPIO_V13_L20P IO_L20P_T3_AD6P_35 GPIO_F19_L20N

U4 P18 V13 F19

IO_L20N_T3_13 GPIO_V5_L21P IO_L20N_T3_34 GPIO_T16_L21P IO_L20P_T3_33 GPIO_W13_L20N IO_L20N_T3_AD6N_35 GPIO_E19_L21P

V5 T16 W13 E19

IO_L21P_T3_DQS_13 GPIO_V4_L21N IO_L21P_T3_DQS_34 GPIO_T17_L21N IO_L20N_T3_33 GPIO_W15_L21P IO_L21P_T3_DQS_AD14P_35 GPIO_E20_L21N

V4 T17 W15 E20

IO_L21N_T3_DQS_13 GPIO_U6_L22P IO_L21N_T3_DQS_34 GPIO_R19_L22P IO_L21P_T3_DQS_33 GPIO_Y15_L21N IO_L21N_T3_DQS_AD14N_35 GPIO_G20_L22P ETH_TXD3

U6 R19 Y15 G20

IO_L22P_T3_13 GPIO_U5_L22N IO_L22P_T3_34 GPIO_T19_L22N IO_L21N_T3_DQS_33 GPIO_Y14_L22P IO_L22P_T3_AD7P_35 GPIO_G21_L22N ETH_MDC

U5 T19 Y14 G21

IO_L22N_T3_13 GPIO_V7_L23P IO_L22N_T3_34 GPIO_R18_L23P IO_L22P_T3_33 GPIO_AA14_L22N IO_L22N_T3_AD7N_35 GPIO_F21_L23P ETH_TXD1

V7 R18 AA14 F21

IO_L23P_T3_13 GPIO_W7_L23N IO_L23P_T3_34 GPIO_T18_L23N IO_L22N_T3_33 GPIO_Y13_L23P IO_L23P_T3_35 GPIO_F22_L23N ETH_TXD2

W7 T18 Y13 F22

IO_L23N_T3_13 GPIO_W6_L24P IO_L23N_T3_34 GPIO_P16_L24P IO_L23P_T3_33 GPIO_AA13_L23N IO_L23N_T3_35 GPIO_H22_L24P ETH_MDIO

W6 P16 AA13 H22

IO_L24P_T3_13 GPIO_W5_L24N IO_L24P_T3_34 GPIO_R16_L24N IO_L23N_T3_33 GPIO_AB14_L24P IO_L24P_T3_AD15P_35 GPIO_G22_L24N ETH_TXCTL

W5 R16 AB14 G22

IO_L24N_T3_13 GPIO_U7 IO_L24N_T3_34 GPIO_R15 IO_L24P_T3_33 GPIO_AB15_L24N IO_L24N_T3_AD15N_35 GPIO_H18 ETH_INT

U7 R15 AB15 H18

IO_25_13 IO_25_34 IO_L24N_T3_33 GPIO_U14 IO_25_35

U14

IO_25_33

XC7Z020_CLG484 XC7Z020_CLG484

A A

Title

HELLOFPGA.COM

Size Document Number Rev

C <Doc> <RevCode>

Date: Wednesday, May 10, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

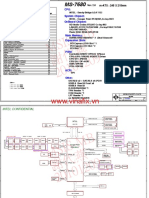

DDR3_VREF2 DDR3_VREF2 J1

U33G

MEM_ADD0 N3 E3 DDR3_D0

D A0 DQ0 D

P7 MEM_ADD1 P7 F7 DDR3_D7

PS_DDR_VREF1_502 A1 DQ1

H7 Y1 MEM_ADD2 P3 F2 DDR3_D1

PS_DDR_VREF0_502 PS_DDR_DQ31_502 A2 DQ2

W3 MEM_ADD3 N2 F8 DDR3_D6

PS_DDR_DQ30_502 A3 DQ3

Y3 MEM_ADD4 P8 H3 DDR3_D3

PS_DDR_DQ29_502 A4 DQ4

MEM_ADD14 G4 W1 MEM_ADD5 P2 H8 DDR3_D5

PS_DDR_A14_502 PS_DDR_DQ28_502 A5 DQ5

MEM_ADD13 F4 U2 MEM_ADD6 R8 G2 DDR3_D2

PS_DDR_A13_502 PS_DDR_DQ27_502 A6 DQ6

MEM_ADD12 H4 AA1 MEM_ADD7 R2 H7 DDR3_D4

PS_DDR_A12_502 PS_DDR_DQ26_502 A7 DQ7

MEM_ADD11 G5 U1 MEM_ADD8 T8

PS_DDR_A11_502 PS_DDR_DQ25_502 A8

MEM_ADD10 J3 AA3 MEM_ADD9 R3

PS_DDR_A10_502 PS_DDR_DQ24_502 A9

MEM_ADD9 H5 R1 MEM_ADD10 L7 D7 DDR3_D13

PS_DDR_A9_502 PS_DDR_DQ23_502 A10/AP DQ8

MEM_ADD8 J5 M2 MEM_ADD11 R7 C3 DDR3_D11

PS_DDR_A8_502 PS_DDR_DQ22_502 A11 DQ9

MEM_ADD7 J6 T2 MEM_ADD12 N7 C8 DDR3_D14

PS_DDR_A7_502 PS_DDR_DQ21_502 A12/BC_L DQ10

MEM_ADD6 J7 R3 MEM_ADD13 T3 C2 DDR3_D10

PS_DDR_A6_502 PS_DDR_DQ20_502 A13 DQ11

MEM_ADD5 K5 T1 MEM_ADD14 T7 A7 DDR3_D9

PS_DDR_A5_502 PS_DDR_DQ19_502 A14/NC DQ12

MEM_ADD4 K6 N3 M7 A2 DDR3_D12

PS_DDR_A4_502 PS_DDR_DQ18_502 A15/NC DQ13

MEM_ADD3 L4 T3 B8 DDR3_D8

PS_DDR_A3_502 PS_DDR_DQ17_502 DQ14

MEM_ADD2 K4 M1 MEM_BANK0 M2 A3 DDR3_D15

PS_DDR_A2_502 PS_DDR_DQ16_502 BA0 DQ15

MEM_ADD1 M5 K3 DDR3_D15 MEM_BANK1 N8

PS_DDR_A1_502 PS_DDR_DQ15_502 BA1 VCC1V5

MEM_ADD0 M4 J1 DDR3_D14 MEM_BANK2 M3

PS_DDR_A0_502 PS_DDR_DQ14_502 BA2

K1 DDR3_D13 B2

PS_DDR_DQ13_502 VDD0

L3 DDR3_D12 MEM_RAS# J3 D9

PS_DDR_DQ12_502 RAS_L VDD1

MEM_BANK2 M6 L2 DDR3_D11 MEM_CAS# K3 G7

PS_DDR_BA2_502 PS_DDR_DQ11_502 CAS_L VDD2 C2 C3 C4 C5 C6 C7 C150

MEM_BANK1 L6 L1 DDR3_D10 MEM_WE# L3 K2

PS_DDR_BA1_502 PS_DDR_DQ10_502 WE_L VDD3

MEM_BANK0 L7 G1 DDR3_D9 K8

C PS_DDR_BA0_502 PS_DDR_DQ9_502 VDD4 10uf 1uf 1uf 0.1uf 0.1uf 0.1uf 10nf

C

G2 DDR3_D8 MEM_CLK0_P J7 N1

PS_DDR_DQ8_502 CK VDD5

F1 DDR3_D7 MEM_CLK0_N K7 N9

PS_DDR_DQ7_502 CK_L VDD6

F3 F2 DDR3_D6 R1

MEM_RESET# PS_DDR_DRST_B_502 PS_DDR_DQ6_502 VDD7

R5 E1 DDR3_D5 MEM_DQS0_P F3 R9

MEM_RAS# PS_DDR_RAS_B_502 PS_DDR_DQ5_502 LDQS VDD8 VCC1V5

P3 E3 DDR3_D4 MEM_DQS0_N G3

MEM_CAS# PS_DDR_CAS_B_502 PS_DDR_DQ4_502 LDQS_L

P6 D3 DDR3_D3 MEM_DQS1_P C7

MEM_MA0_CS_L0 PS_DDR_CS_B_502 PS_DDR_DQ3_502 UDQS

R4 B2 DDR3_D2 MEM_DQS1_N B7 A1

MEM_WE# PS_DDR_WE_B_502 PS_DDR_DQ2_502 UDQS_L VDDQ0

C3 DDR3_D1 A8

PS_DDR_DQ1_502 VDDQ1

D1 DDR3_D0 MEM_DM0 E7 C1

PS_DDR_DQ0_502 LDM VDDQ2 C12 C13 C14 C15 C16 C17

V3 MEM_DM1 D3 C9

MEM_MA0_CKE0 PS_DDR_CKE_502 UDM VDDQ3

N4 D2

MEM_CLK0_P PS_DDR_CKP_502 VDDQ4 0.1uf 0.1uf 0.1uf 0.1uf 0.1uf 10nf

N5 AA2 MEM_MA0_CKE0 K9 E9

MEM_CLK0_N R10 80.6r PS_DDR_CKN_502 PS_DDR_DM3_502 CKE0 VDDQ5

P1 J9 F1

PS_DDR_DM2_502 CKE1/NC VDDQ6

H3 MEM_DM1 H2

PS_DDR_DM1_502 VDDQ7

P5 B1 MEM_DM0 MEM_MA0_CS_L0 L2 H9

MEM_MA0_ODT0 PS_DDR_ODT_502 PS_DDR_DM0_502 CS0_L VDDQ8

L1

CS1_L/NC

R13 80.6r N7 V2 MEM_MA0_ODT0 K1 B1

R14 80.6r PS_DDR_VRP_502 PS_DDR_DQS_P3_502 ODT0 VSSQ0

VCC1V5 M7 W2 J1 B9

PS_DDR_VRN_502 PS_DDR_DQS_N3_502 MEM_RESET# ODT1/NC VSSQ1

N2 MEM_RESET# T2 D1

PS_DDR_DQS_P2_502 RESET_L VSSQ2

P2 D8

PS_DDR_DQS_N2_502 VSSQ3

H2 MEM_DQS1_P DDR3_VREF M8 E2

PS_DDR_DQS_P1_502 VREFCA VSSQ4

R12

J2 MEM_DQS1_N H1 E8

PS_DDR_DQS_N1_502 VREFDQ VSSQ5

B C2 MEM_DQS0_P F9 B

PS_DDR_DQS_P0_502 VSSQ6

D2 MEM_DQS0_N L8 G1

PS_DDR_DQS_N0_502 ZQ0 VSSQ7

4.7k

L9 G9

ZQ1/NC VSSQ8

R15

A9 J8

VSS0 VSS5

XC7Z020_CLG484 B3 M1

VSS1 VSS6

240R

E1 M9

VSS2 VSS7

G8 P1

VSS3 VSS8

J2 P9

VSS4 VSS9

T1

VSS10

T9

VCC1V5 VCC1V5 VSS11

DDR3_VREF2 MT41K256M16TW-107

R16

R144 1k

C151 C159 DDR3_VREF C155

0.1uf 10nf 0.1uf

1k

DDR PART HELLOFPGA.COM

R18

R145 1k

C21 C22 C156 C160

1k

0.1uf 10nf 0.1uf 0.1uf

A A

Title

HELLOFPGA.COM

Size Document Number Rev

B <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

VCC3V3

R436

R437

R438

R439

R440

R441

R442

R443

D HELLOFPGA.COM D

5V_DC

49.9R

49.9R

49.9R

49.9R

49.9R

49.9R

49.9R

49.9R

J29

D24 MBR052018

+5V

HDMI_TX_TMDS_DAT0_P C154 0.1uf _HDMI_TX_TMDS_DAT0_P 7

DATA0+

8

HDMI_TX_TMDS_DAT0_N C187 0.1uf _HDMI_TX_TMDS_DAT0_N DATA0_SHIELD

9

DATA0-

HDMI_TX_TMDS_DAT1_P C188 0.1uf _HDMI_TX_TMDS_DAT1_P 4 20

DATA1+ SHIELD_1

5

HDMI_TX_TMDS_DAT1_N C157 0.1uf _HDMI_TX_TMDS_DAT1_N DATA1_SHIELD

6

DATA1-

HDMI_TX_TMDS_DAT2_P C158 0.1uf _HDMI_TX_TMDS_DAT2_P 1 21

DATA2+ SHIELD_2

C 2 C

HDMI_TX_TMDS_DAT2_N C189 0.1uf _HDMI_TX_TMDS_DAT2_N DATA2_SHIELD

3

DATA2-

HDMI_CLK_TX_TMDS_P C190 0.1uf _HDMI_CLK_TX_TMDS_P 10

CLK+

11

HDMI_CLK_TX_TMDS_N C161 0.1uf _HDMI_CLK_TX_TMDS_N CLK_SHIELD

12 22

CLK- SHIELD_3

13

CEC

15

SCL

16 23

SDA SHIELD_4

U15 19

HOT PLUG DET

HDMI_TX_TMDS_DAT1_N 1 10 HDMI_TX_TMDS_DAT1_N 17

HDMI_TX_TMDS_DAT1_P 2 CH1 NC_4 HDMI_TX_TMDS_DAT1_P DDC/CEC_GND

9

CH2 NC_3

14

RSVD

3 8

GND_1 GND_2

B CONN_HDMI B

HDMI_TX_TMDS_DAT2_N 4 7 HDMI_TX_TMDS_DAT2_N

HDMI_TX_TMDS_DAT2_P 5 CH3 NC_2 HDMI_TX_TMDS_DAT2_P

6

CH4 NC_1

PUSB3FR4

HDMI_CLK_TX_TMDS_N 1

U8

10 HDMI_CLK_TX_TMDS_N

HDMI

HDMI_CLK_TX_TMDS_P CH1 NC_4 HDMI_CLK_TX_TMDS_P

2 9

CH2 NC_3

3 8

GND_1 GND_2

HDMI_TX_TMDS_DAT0_N 4 7 HDMI_TX_TMDS_DAT0_N

HDMI_TX_TMDS_DAT0_P 5 CH3 NC_2 HDMI_TX_TMDS_DAT0_P

6

CH4 NC_1

A A

PUSB3FR4

Title

HELLOFPGA.COM

Size Document Number Rev

A <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

DVDD33

AVDD33

DVDD10 AVDD33

D AVDD10 VDDREG D

C660 C661

DVDD33 22uf 0.1uf AVDD10

RTL8211E-VB-CG

28

36

15

21

37

40

41

44

45

9

3

6

C664 C665 C666

AVDD10_1

AVDD10_2

AVDD10_3

AVDD33_1

AVDD33_2

DVDD10_1

DVDD10_2

DVDD33_1

DVDD33_2

DVDD33_3

VDDREG_1

VDDREG_2

0.1uf 0.1uf 0.1uf

R43

R55

R56

R454

VCC1V0 DVDD10

R42 0R

C662 C663 C668C669

4.7k

4.7k

4.7k

4.7k

ETH_RXD0 14

ETH_RXD1 RXD0/SELRGV 22uf 0.1uf 0.1uf0.1uf

16

ETH_RXD2 RXD1/TXDLY

17

ETH_RXD3 RXD2/AN0 48

18 REG_OUT

ETH_RXCTL RXD3/AN1

13

ETH_RXC RXCTL/PHY_AD2

19

RXC

MDI[0]+

1 A-TX0P

A-TX0N

NET PART

R57

2

ETH_TXD0 23 MDI[0]-

ETH_TXD1 24 TXD0 A-TX1P

4

ETH_TXD2 25 TXD1 MDI[1]+ A-TX1N J3

5

C

DVDD33 ETH_TXD3 26 TXD2 MDI[1]- C

4.7k

R455 ETH_TXCTL27 TXD3 A-TX2P A-TX0P

7 2 A

ETH_TXC 22 TXCTL MDI[2]+ A-TX2N A-TX0N TD0+ SHIELD1

8 3

DVDD33 TXC MDI[2]- DVDD33 A-TX1P TD0- R63 0R

4 B

1.5K A-TX3P A-TX1N TD1+ SHIELD2

10 7

ETH_MDIO 31 MDI[3]+ A-TX3N A-TX2P TD1-

11 5

R52 ETH_MDC MDIO MDI[3]- R58 R59 A-TX2N TD2+

30 6

MDC A-TX3P TD2-

8

A-TX3N TD3+ 1

9 P1

10k ETH_INT 4.7k 4.7k TD3-

20

INTB 34 ETH_LED0 ETH_LED1 R62 330R 10

33 LED0/PHY_AD0 11 P10

PHYRSTB PMEB 35 ETH_LED1 LED_G+ C678

29 LED1/PHY_AD1 12

PHYRSTB 32 ETH_LED2 LED_G-

38 LED2/RXDLY 0.1uf

ENSWREG

DVDD33 14

C670 R60 ETH_LED0 R61 330R LED_Y+

13

X4 LED_Y-

42

1UF CKXTAL1 39

43 RSET

1 2 CKXTAL2 4.7k

46 HR911130A

CLK125 12 R39

NC

E_PAD

4 3

GND

C680

25Mhz C681 2.49k

27pf

27pf

47

49

B B

U24

VCC3V3

AVDD33

HELLOFPGA.COM

C672 C673 C679 C674 C675

22uf 0.1uf 0.1uf 0.1uf 0.1uf

DVDD33

C676 C677

A 0.1uf 0.1uf A

Title

HELLOFPGA.COM

Size Document Number Rev

B <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

QSPI FLASH EEPROM

VCC3V3 VCC3V3 VCC3V3

C48

PL CLK

R151 4.7k

C18

D U10 0.1uf VCC3V3 VCC3V3 D

0.1uf 1 8 X2

J2 2 A0 VCC 7 4 3 CLK_50M

QSPI_CS 3 A1 WP 6 EEPROM_SCL R33 10K C310 VCC OUT 22R R132

1 8

SPI_DQ1/MIO3 CS VCC SPI_DQ3/MIO5 4 A2 SCL 5 EEPROM_SDA R34 10K 1 2

2 7

SPI_DQ2/MIO4 DO(IO1) HOLD(IO3) SPI_SCK/MIO6 VSS SDA 0.1uf NC GND

3 6

WP(IO2) CLK SPI_DQ0/MIO2 24c02 50MHZ

4 5

GND DI(IO0)

W25Q128JVSIQTR

VCC3V3 TF CARD U11

KEY SD_D2 PS CLK

R450

R451

1

SD_D3 DAT2

2

C

SD_CMD CD/DAT3 C

3

CMD VCC3V3

4

4.7k

4.7k

VCC3V3 VDD

SD_CLK 5 X1

CLK 4 3 PS_CLK_33.333M

6

SD_D0 VSS C1 VCC OUT 22R R1

7

KEY2 SW SD_D1 DAT0 1 2

8

KEY2 10k R444 DAT1 0.1uf NC GND

VCC3V3 9

KEY1 SW DEL_SW 33.333M

P1

P2

P3

P4

KEY1 SD_CD 22R R445

TF

P1

P2

P3

P4

LED BOOT BOOT

B

LED1 BOOT S1 S2 B

LED2 SPI_DQ0/MIO2 R5 20k

SPI_DQ1/MIO3 R6 20k

R50 R51

SPI_DQ2/MIO4

SPI_DQ3/MIO5

SPI_SCK/MIO6

R146

R147

R7

20k

20k

20k

R447 1k

R148 1k

VCC3V3

VCC3V3

JTAG

VCFG0/MIO7 R8 20k

330R 330R VCFG1/MIO8 R9 20k

4

GREEN GREEN J30 QSPI

3

4

LED1 LED2 SWAP

S2 S1

SD

2

1

2

A HELLOFPGA.COM A

Title

HELLOFPGA.COM

Size Document Number Rev

B <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

5V_DC

VCC1V5 VCC1V8 VCC1V0

C166 0.1uf C167 0.1uf 5V_DC C172 0.1uf

5V_DC

R169

U16 U17 U18

VCC1V5 VCC1V8 R160 VCC1V0

1 6 20k R157 1 6 10k R159 1 6 R162

GND VBST GND VBST GND VBST

9.53k 27k 3k

L3 2.2uh 2a 2 5 L7 2.2uh 2a 2 5 L8 2.2uh 2a 2 5

SW EN C184 SW EN SW EN 10k R163

5V_DC 3 4 5V_DC 3 4 5V_DC 3 4

C162 C163 VIN VFB 0.1uf C168 C169 VIN VFB C173 C174 VIN VFB

C164 C165 R158 C170 C171 R161 C175 C176 R164

22uf 22uf TPS563201_3A 10k 22uf 22uf TPS563201_3A C182 20k 22uf 22uf TPS563201_3A 10k

D D

10uf/10V

10uf/10V 10uf/10V

10uf/10V 0.1uf 10uf/10V

10uf/10V

5V_DC

VCCIO_ADJ 5V_DC

C177 0.1uf VCC3V3

R166 C682 0.1uf

R459

U19

VCCIO_ADJ 20k VCC3V3

U27

1 6 RA VCC3V3 20k

GND VBST R460

33k 1 6

L9 2.2uh 2a GND VBST

2 5 33k

U32 SW EN R452 L10 2.2uh 2a 2 5

SW EN

1 5V_DC 3 4

VCC C178 C179 VIN VFB 330R 5V_DC 3 4

C180 C181 RB C683 C684 VIN VFB

2

GND 22uf 22uf TPS563201_3A C183 RED C685 C686 R462

10k

HEADER 2X1 10uf/10V

10uf/10V LED4 22uf 22uf TPS563201_3A C687 10k

0.1uf 10uf/10V

10uf/10V

0.1uf

Default Vadj = 3.3V POWER

HELLOFPGA.COM

C C

U7

USB_DP 1 8

UD+ V3 VCC3V3

USB_POWER 5V_DC USB_DN 2 7 CH340_UART_RX

UD- RXD CH340_UART_TX

3 6

U14 D22 SS24 GND TXD

4 5 VCC3V3

RTS# VCC

1 CH340N

GND C191

2

VBUS 0.1uf VCC3V3

3

SBU2 J15

4

CC1 USB_DN FPGA_TCK 1 2

P1 5

P1 DN2 FPGA_TDO 3 TCK GND_1 4

P2 6

P2 DP1 FPGA_TMS 5 TDO VCC_1 6 C309

P3 7

P3 DN1 USB_DP 7 TMS NC_3 8

P4 8

P4 DP2 FPGA_TDI 9 NC_1 NC_2 10 10uf/10V

9

SBU1 U30 TDI GND_2

10

CC2

11 JTAG

VBUS_2

R448 5.1k

R449 5.1k

12 1 10

GND_2 CH1 NC_4

2 9

CH2 NC_3

TYPEC 3 8

B GND_1 GND_2 B

USB_DP 4 7 USB_DP

USB_DN CH3 NC_2 USB_DN

5 6

CH4 NC_1

PUSB3FR4 JTAG

TYPE C & UART

A A

Title

HELLOFPGA.COM

Size Document Number Rev

C <Doc> <RevCode>

Date: Wednesday, May 10, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

D VCC3V3 D

C29 C34 C701

U33I

VCC1V5 22uf 0.1uf 10uf

V1 R12

VCCO_DDR_502_9 VCCO_0

C30

C35

C31

C36

C32

C37

C41

C33

R2

VCCO_DDR_502_8 VCC3V3

N6

VCCO_DDR_502_7

M3 AA10

VCCO_DDR_502_6 VCCO_13_1 C38 C39 C40 C722 C723 U33H

K7 AB3

1uf

1uf

100uf

10uf

10nf

0.1uf

0.1uf

0.1uf

VCCO_DDR_502_5 VCCO_13_2

J4 T5

VCCO_DDR_502_4 VCCO_13_3 100uf 10uf 0.1uf 10uf 0.1uf

H1 U8 Y22 A5

VCC1V0 VCCO_DDR_502_3 VCCO_13_4 GND_63 GND_1

F5 V11 Y12 A15

VCCO_DDR_502_2 VCCO_13_5 GND_62 GND_2

E2 W4 Y2 AA5

VCCO_DDR_502_1 VCCO_13_6 GND_61 GND_3

C712

C713

C714

C715 Y7 W19 AA15

VCCO_13_7 GND_60 GND_4

W9 AB8

VCCIO_ADJ GND_59 GND_5

J10 V16 AB18

VCCBRAM_2 GND_58 GND_6

H11 AA20 V6 B8

10uf

10uf

100uf

0.1uf

VCCBRAM_1 VCCO_33_1 GND_57 GND_7

C717

C718

C719

C720

C721

AB13 U13 B18

VCC3V3 VCCO_33_2 GND_56 GND_8

U18 U3 C1

VCCO_33_3 GND_55 GND_9

C6 V21 T20 C11

VCCO_MIO0_500_2 VCCO_33_4 GND_54 GND_10

C52

C53

B3 W14 R17 C21

10uf

10uf

100uf

0.1uf

0.1uf

C VCCO_MIO0_500_1 VCCO_33_5 GND_53 GND_11 C

Y17 R13 D4

VCCO_33_6 GND_52 GND_12

R11 D14

VCC3V3 GND_51 GND_13

C60

C61

C62

E12 R9 E7

10uf

0.1uf

VCC3V3 VCCO_MIO1_501_4 GND_50 GND_14

D9 K17 P14 E17

VCCO_MIO1_501_3 VCCO_34_1 GND_49 GND_15

C45

C46

C49

C50

C195

B13 L20 P12 F10

VCCO_MIO1_501_2 VCCO_34_2 GND_48 GND_16

A10 N16 P10 F20

10uf

10uf

0.1uf

VCCO_MIO1_501_1 VCCO_34_3 GND_47 GND_17

P19 P8 G3

VCC1V0 VCCO_34_4 GND_46 GND_18

R22 P4 H6

10uf

10uf

100uf

0.1uf

0.1uf

VCCO_34_5 GND_45 GND_19

C63

C196

C67

C68

R8 T15 N21 H8

VCCPINT_6 VCCO_34_6 GND_44 GND_20

N8 N13 H12

VCCPINT_5 VCC3V3 GND_43 GND_21

L8 N9 H14

VCCPINT_4 GND_42 GND_22

J8 A20 N1 H16

100uf

10uf

0.1uf

0.1uf

VCCPINT_3 VCCO_35_1 GND_41 GND_23

C54

C55

C194

C58

C59

H9 C16 M18 J9

VCCPINT_2 VCCO_35_2 GND_40 GND_24

G8 D19 M14 J11

VCCPINT_1 VCCO_35_3 GND_39 GND_25

E22 M10 J13

VCC1V8 VCCO_35_4 GND_38 GND_26

F15 M8 J19

10uf

10uf

100uf

0.1uf

0.1uf

VCCO_35_5 GND_37 GND_27

C74

C705

C706

C707

T9 G18 L15 K2

VCCPAUX_4 VCCO_35_6 GND_36 GND_28

P9 H21 L13 K8

VCCPAUX_3 VCCO_35_7 GND_35 GND_29

M9 L9 K10

VCCPAUX_2 VCC1V8 GND_34 GND_30

K9 L5 K14

10uf

100uf

0.1uf

0.1uf

VCCPAUX_1 GND_33 GND_31

L10 K22

VCC1V8 VCCAUX_1 GND_32

C69

C710

C708

C709

N10

FB2 BLM18SG121TN1D VCCAUX_2

H10 P11

VCCPLL VCCAUX_3

C704

C81

B R10 XC7Z020_CLG484 B

VCCAUX_4

10uf

10uf

0.1uf

0.1uf

G9 J12

C716 10uf

0.1uf

VCCBATT_0 VCCINT_1 VCC1V0

J14

VCCINT_2

VCC1V8 K13

VCCINT_3

C75

C76

C79

C80

C197

L14

VCCINT_4

VCCINT_5

M13

N14

HELLOFPGA.COM

0.1uf

VCCINT_6

P13

10uf

10uf

100uf

0.1uf

0.1uf

VCCINT_7

R14

VCCINT_8

XC7Z020_CLG484

A A

Title

HELLOFPGA.COM

Size Document Number Rev

B <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 1

5 4 3 2 1

5 4 3 2 1

D D

BANK 33 BANK 35

U12 U13

5V_DC 5V_DC 5V_DC 5V_DC

VCC3V3 VCC3V3

VCC3V3 40 39 VCC3V3 40 39

40 39 40 39

38 37 38 37

38 37 38 37

36 35 36 35

GPIO_V14_L19P 34 36 35 GPIO_V15_L19N GPIO_G16_L4N 36 35 GPIO_G15_L4P

33 34 33

GPIO_AA14_L22N 32 34 33 GPIO_Y14_L22P GPIO_F16_L1P 34 33 GPIO_E16_L1N

C 31 32 31 C

GPIO_Y16_L14N 30 32 31 GPIO_W16_L14P GPIO_C19_L12N 32 31 GPIO_D18_L12P

29 30 29

GPIO_AB17_L17N 28 30 29 GPIO_AA17_L17P GPIO_E15_L3P 30 29 GPIO_D15_L3N

27 28 27

GPIO_W17_L13P 26 28 27 GPIO_W18_L13N GPIO_D16_L2P 28 27 GPIO_D17_L2N

25 26 25

GPIO_W13_L20N 24 26 25 GPIO_V13_L20P GPIO_C15_L7P 26 25 GPIO_B15_L7N

23 24 23

GPIO_AA13_L23N 22 24 23 GPIO_Y13_L23P GPIO_C20_L14N 24 23 GPIO_D20_L14P

21 22 21

GPIO_AB15_L24N 20 22 21 GPIO_AB14_L24P GPIO_A16_L9P 22 21 GPIO_A17_L9N

19 20 19

GPIO_AA18_L12N 18 20 19 GPIO_Y18_L12P GPIO_B16_L8P 20 19 GPIO_B17_L8N

17 18 17

GPIO_AA16_L18P 16 18 17 GPIO_AB16_L18N GPIO_B21_L18P 18 17 GPIO_B22_L18N

15 16 15

GPIO_Y19_L11P 14 16 15 GPIO_AA19_L11N GPIO_C22_L16N 16 15 GPIO_D22_L16P

13 14 13

GPIO_AB20_L10N 12 14 13 GPIO_AB19_L10P GPIO_E19_L21P 14 13 GPIO_E20_L21N

11 12 11

GPIO_AA21_L8P 10 12 11 GPIO_AB21_L8N GPIO_F19_L20N 12 11 GPIO_G19_L20P

9 10 9

GPIO_AA22_L7P 8 10 9 GPIO_AB22_L7N GPIO_C18_L11N 10 9 GPIO_C17_L11P

7 8 7

GPIO_Y20_L9P 8 7 GPIO_Y21_L9N GPIO_G17_L6P 8 7 GPIO_F17_L6N

6 5 6 5

GPIO_V22_L3P 6 5 GPIO_W22_L3N GPIO_F18_L5P 6 5 GPIO_E18_L5N

4 3 4 3

GPIO_T22_L2P 4 3 GPIO_U22_L2N GPIO_H20_L19N 4 3 GPIO_H19_L19P

2 1 2 1

2 1 2 1

B B

HEADER 20x2 HEADER 20x2

VCCIO :VADJ

Default Vadj = 3.3V VCCIO :3.3V

A A

Title

HELLOFPGA.COM

Size Document Number Rev

A <Doc> <RevCode>

Date: Monday, May 01, 2023 Sheet 1 of 3

5 4 3 2 1

5 4 3 2 1

D D

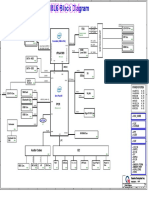

GigE phy

KEY & LED ETH TD0 E21

KEY1 K21

ETH TD1 F21

UART KEY2 J20

ZYNQ_TX L17 ETH TD2 F22

LED1 P20

ZYNQ_RX M17 ETH TD3 G20

LED2 P21

ETH TX_CTL G22

C C

ETH TXC D21

EEPROM ETH RD0 A22

SCL R20 HDMI ETH RD1 A18

SDA R21 CLK N22

ETH RD2 A19

D0 M21

ETH RD3 B20

D1 L21

ETH RX_CTL A21

50M CLOCK D2 J21

CLK M19 ETH RXC B19

B

ETH MDIO H22 B

HELLOFPGA.COM ETH MDC G21

ETH INT H18

A A

Title

HELLOFPGA.COM

Size Document Number Rev

C <Doc> <RevCode>

Date: Wednesday, May 10, 2023 Sheet 1 of 1

5 4 3 2 1

También podría gustarte

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Smart Zynq SP v1 0 20230501Documento11 páginasSmart Zynq SP v1 0 20230501Satvik HardatAún no hay calificaciones

- Curso de Laptops Nivel BasicoDocumento62 páginasCurso de Laptops Nivel Basicomagomix25Aún no hay calificaciones

- Iniciación al diseño de circuitos impresos con Altium DesignerDe EverandIniciación al diseño de circuitos impresos con Altium DesignerAún no hay calificaciones

- Gigabyte Ga-6veml - Rev 1.0Documento26 páginasGigabyte Ga-6veml - Rev 1.0Victor AlvarezAún no hay calificaciones

- Acer Aspire 7740G - WISTRON JV70-CP - REV - 1 PDFDocumento67 páginasAcer Aspire 7740G - WISTRON JV70-CP - REV - 1 PDFLos QuilmesAún no hay calificaciones

- Asus A8n A8dDocumento57 páginasAsus A8n A8dWilfredoAún no hay calificaciones

- Acer Aspire 2920 Wistron Calado PDFDocumento39 páginasAcer Aspire 2920 Wistron Calado PDFNang PoDolAún no hay calificaciones

- SunSet E20c - Movistar - VenezuelaDocumento153 páginasSunSet E20c - Movistar - VenezuelaJESUS45Aún no hay calificaciones

- HP 14-Q070NR Quanta A23 (Y01 DA0Y01MBAC0) R1a 20082013Documento42 páginasHP 14-Q070NR Quanta A23 (Y01 DA0Y01MBAC0) R1a 20082013Fidel GuzmanAún no hay calificaciones

- Quanta ZL8 - Rev 2aDocumento26 páginasQuanta ZL8 - Rev 2aSilvio RodriguesAún no hay calificaciones

- Curso de LaptopsDocumento53 páginasCurso de LaptopsFERNANDO R. RAún no hay calificaciones

- Ejem. de Etiquetado Cables de Sincronia N0500208A3Documento3 páginasEjem. de Etiquetado Cables de Sincronia N0500208A3MONTBLACAAún no hay calificaciones

- Curso de Ecus MasterDocumento90 páginasCurso de Ecus Masteralex100% (2)

- CSL58MW4VA200DDocumento1 páginaCSL58MW4VA200DI vastec IvaAún no hay calificaciones

- Intel H67 1155 MS-7680Documento37 páginasIntel H67 1155 MS-7680LILYAún no hay calificaciones

- 731 - ZRV Da0zrvmb6d0 Zrva - 1aDocumento44 páginas731 - ZRV Da0zrvmb6d0 Zrva - 1ajorgeAún no hay calificaciones

- Schematics Laptop Toshiba Satellite l645 l650 Quanta Bl6Documento43 páginasSchematics Laptop Toshiba Satellite l645 l650 Quanta Bl6Ain SmuleAún no hay calificaciones

- Quanta X61 Da0x61mb6g0 Rev 1a (HP Probook 430)Documento65 páginasQuanta X61 Da0x61mb6g0 Rev 1a (HP Probook 430)cof20Aún no hay calificaciones

- Ldo Baclaith Mipi OvpDocumento25 páginasLdo Baclaith Mipi OvpWALTER CABRERAAún no hay calificaciones

- CSH7GMW4VA202B: Especifi CacionesDocumento1 páginaCSH7GMW4VA202B: Especifi CacionesAdquisiciones Division de abastecimientoAún no hay calificaciones

- Instalacion SF101Documento8 páginasInstalacion SF101Alejandro MartillAún no hay calificaciones

- Circuitos Digitales 3Documento3 páginasCircuitos Digitales 3juan pabloAún no hay calificaciones

- CMP7GMW5VA206RDocumento1 páginaCMP7GMW5VA206RI vastec IvaAún no hay calificaciones

- Lenovo Thinkpad x200t Table Da0khamb6d0 (Diagramas - Com.br)Documento62 páginasLenovo Thinkpad x200t Table Da0khamb6d0 (Diagramas - Com.br)herman yauckAún no hay calificaciones

- Presentacion para Disertacion ElementosDocumento14 páginasPresentacion para Disertacion ElementosSebastian Oyarzo CarcamoAún no hay calificaciones

- Identificación de La Placa BaseDocumento8 páginasIdentificación de La Placa BaseBubuna EdúAún no hay calificaciones

- Universidad Politecnica SalesianaDocumento3 páginasUniversidad Politecnica SalesianaEddy MorilloAún no hay calificaciones

- Universidad Politecnica SalesianaDocumento3 páginasUniversidad Politecnica SalesianaEddy MorilloAún no hay calificaciones

- Universidad Politecnica SalesianaDocumento3 páginasUniversidad Politecnica SalesianaEddy MorilloAún no hay calificaciones

- AOPEN WB5500 I7-7500u OPSDocumento2 páginasAOPEN WB5500 I7-7500u OPSMarisa García CulpiánAún no hay calificaciones

- Tabla ComparativaDocumento1 páginaTabla Comparativaricardo jimenezAún no hay calificaciones

- Toshiba Setellite l650655 Quantate2dDocumento43 páginasToshiba Setellite l650655 Quantate2dJULIAN TORRES ZABALAAún no hay calificaciones

- Quanta Tz1c Rev B2a - Toshiba Qosmio x505Documento43 páginasQuanta Tz1c Rev B2a - Toshiba Qosmio x505Da El100% (1)

- Cuadro ComparativoDocumento3 páginasCuadro Comparativojuan pabloAún no hay calificaciones

- Caracteristicas Principales de Los PLC P PDFDocumento6 páginasCaracteristicas Principales de Los PLC P PDFJhatio UtrillaAún no hay calificaciones

- Curso De-Ecus MasterDocumento90 páginasCurso De-Ecus Masteralex100% (2)

- MBI5025 en EsDocumento18 páginasMBI5025 en EsJOSEPH GOMEZ SAENZAún no hay calificaciones

- Relés de Protección para Distribución Primaria y SecundariaDocumento4 páginasRelés de Protección para Distribución Primaria y SecundariaVEMATELAún no hay calificaciones

- La Familia de Microcontroladores PICDocumento43 páginasLa Familia de Microcontroladores PICcarlitosvoley100% (1)

- CMH5GQW4VA202H: Especifi CacionesDocumento1 páginaCMH5GQW4VA202H: Especifi CacionesSAMUEL GILBER ORTIZ JAIMESAún no hay calificaciones

- Diseño de Un Amplificador de Sonido A 30W PDFDocumento5 páginasDiseño de Un Amplificador de Sonido A 30W PDFAmilkar Vargas SullcaAún no hay calificaciones

- Diseño de Un Amplificador de Sonido A 30wDocumento5 páginasDiseño de Un Amplificador de Sonido A 30wAmilkar Vargas SullcaAún no hay calificaciones

- ES FANOXTD FICHA SIA OCEFDistSecundaria SIAC GC17 R02Documento8 páginasES FANOXTD FICHA SIA OCEFDistSecundaria SIAC GC17 R02Alejandro Solis GomezAún no hay calificaciones

- Calculo de CircuitosDocumento2 páginasCalculo de CircuitosPablo Marin HuamanAún no hay calificaciones

- Quanta Y11c Dis Lay-Vine R1a 20140902 SchematicsDocumento45 páginasQuanta Y11c Dis Lay-Vine R1a 20140902 SchematicsRicardo Banda BocanegraAún no hay calificaciones

- Td3cap 2Documento20 páginasTd3cap 2Andres Raul Bruno SaraviaAún no hay calificaciones

- Gamas MicrosDocumento14 páginasGamas MicrosDanilo PuninaAún no hay calificaciones

- Quanta Y11c Dis Lay-Vine R1a 20140514 SchematicsDocumento45 páginasQuanta Y11c Dis Lay-Vine R1a 20140514 SchematicsRicardo Banda BocanegraAún no hay calificaciones

- Chevy ConfortDocumento31 páginasChevy ConfortReinaldo ArrivillagaAún no hay calificaciones

- Catálogo Bitt Electronics OctubreDocumento14 páginasCatálogo Bitt Electronics OctubreGaston Yampara VargasAún no hay calificaciones

- Franco Gamboa Wilberth Ricardo 3A MT TAREA 1 PLCDocumento4 páginasFranco Gamboa Wilberth Ricardo 3A MT TAREA 1 PLCJavier Fernando Ventura ZuñigaAún no hay calificaciones

- Acosta Pérez Álvaro MME02 TareaDocumento5 páginasAcosta Pérez Álvaro MME02 Tareaalvarodel89Aún no hay calificaciones

- La Plataforma Arruinó Se Podría Decir Que Es Una Minicomputadora Que Se Puede Conectar A Sensores o Actuadores para Poder Crear ProyectosDocumento4 páginasLa Plataforma Arruinó Se Podría Decir Que Es Una Minicomputadora Que Se Puede Conectar A Sensores o Actuadores para Poder Crear ProyectosMiguel Adolfo Quevedo SerranoAún no hay calificaciones

- ControlDocumento1 páginaControlnigelAún no hay calificaciones

- CBM209X Flash Support List (2020!3!16)Documento26 páginasCBM209X Flash Support List (2020!3!16)stone.piedra476Aún no hay calificaciones

- Ejercicios Gestión Del TiempoDocumento5 páginasEjercicios Gestión Del TiempoCarlos Correa Flore100% (1)

- Rodamientos Motor 75 HP WEGDocumento4 páginasRodamientos Motor 75 HP WEGMario Alexander Sinisterra BautistaAún no hay calificaciones

- Manual Practico Equipo Ondas Escalares de Nikola TeslaDocumento35 páginasManual Practico Equipo Ondas Escalares de Nikola TeslaIvan Ugidos Martinez100% (6)

- Curso WordpadDocumento38 páginasCurso WordpadJoseph Sedano PeralesAún no hay calificaciones

- Saberes Fisica 10 Funcion LinealDocumento2 páginasSaberes Fisica 10 Funcion LinealLaura PintoAún no hay calificaciones

- Funcion de La LogisticaDocumento7 páginasFuncion de La LogisticaMon MagañaAún no hay calificaciones

- Manual JavaCCDocumento8 páginasManual JavaCCMisael CruzAún no hay calificaciones

- Paper-Estudio de MedicamentosDocumento58 páginasPaper-Estudio de MedicamentosGabriel EstebanAún no hay calificaciones

- Primera Entrega Gestion de La SeguridadDocumento13 páginasPrimera Entrega Gestion de La Seguridaddeiner100% (1)

- Qué Es La EstadísticaDocumento3 páginasQué Es La EstadísticaEdison GarciaAún no hay calificaciones

- Certificado DcsDocumento8 páginasCertificado DcsLuis AngelAún no hay calificaciones

- Manual Rapido Tso ZosmenuDocumento15 páginasManual Rapido Tso ZosmenuFrancisco de Assis Domingos PenhaAún no hay calificaciones

- DescargaDocumento2 páginasDescargaCopicentro CobanAún no hay calificaciones

- Normativa PeruanaDocumento29 páginasNormativa PeruanaJosephPierreAnayaVelaAún no hay calificaciones

- Cómo Enviar Un Beso Con Un Mensaje de TextoDocumento11 páginasCómo Enviar Un Beso Con Un Mensaje de TextoPedroGutierezSaenzAún no hay calificaciones

- Reseña Historica 2023Documento6 páginasReseña Historica 2023Miletza AnguloAún no hay calificaciones

- Diseño Factorial de Dos FactoresDocumento6 páginasDiseño Factorial de Dos Factoresjeyleen diaz100% (1)

- ETB - Términos y Condiciones SERVICIO MÓVIL 20160906v2Documento44 páginasETB - Términos y Condiciones SERVICIO MÓVIL 20160906v2NicolásCastilloDíazAún no hay calificaciones

- UntitledDocumento41 páginasUntitledGigi SalveminiAún no hay calificaciones

- f5.p21.Gth Formato Autorizacion de Tratamiento de Datos Personales v2Documento1 páginaf5.p21.Gth Formato Autorizacion de Tratamiento de Datos Personales v2fundaAún no hay calificaciones

- Temario - Calidad de La Energía-1Documento5 páginasTemario - Calidad de La Energía-1elmer18Aún no hay calificaciones

- Cotización Inmeditel Instalación Planta EléctricaDocumento2 páginasCotización Inmeditel Instalación Planta EléctricaalexanderAún no hay calificaciones

- Analizador SintacticoDocumento14 páginasAnalizador SintacticoElias TiñoAún no hay calificaciones

- Programa Coding Bootcamp - Plan de EstudiosDocumento4 páginasPrograma Coding Bootcamp - Plan de EstudiosAlejandroAún no hay calificaciones

- Dosier 2018 BDocumento9 páginasDosier 2018 BIVAN PEREZAún no hay calificaciones

- Funciones de Fecha y HoraDocumento3 páginasFunciones de Fecha y HoraJAIRO JIMENEZ FERNANDEZAún no hay calificaciones

- Guia de Ejercicios Prog3-Evaluacion 3Documento2 páginasGuia de Ejercicios Prog3-Evaluacion 3unrealresidentAún no hay calificaciones

- Catálogo VINNO X1 Médica Innovadora - Grupo BioimagenDocumento4 páginasCatálogo VINNO X1 Médica Innovadora - Grupo BioimagentonyAún no hay calificaciones

- Six Keys To Building New Markets by Unleashing Disruptive InnovationDocumento10 páginasSix Keys To Building New Markets by Unleashing Disruptive InnovationCelina MoretaAún no hay calificaciones

- Capítulos I - VIDocumento185 páginasCapítulos I - VILuis Andres Viracucha MasabandaAún no hay calificaciones