Documentos de Académico

Documentos de Profesional

Documentos de Cultura

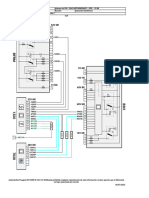

AIC Hoja 4 (Ejercicio 2)

Cargado por

Lupita Ramos0 calificaciones0% encontró este documento útil (0 votos)

6 vistas2 páginasDerechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

6 vistas2 páginasAIC Hoja 4 (Ejercicio 2)

Cargado por

Lupita RamosCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

Issue Exec Write Comm Ult fase en

Ciclo 12

LD F2, 0(R1 ) 1 2 3 4 Comm

MULTD F4, F2, F0 2 4-10 11 12 write

LD F6, 0(R2) 2 3 4 -- Write

ADDD F6, F4, F6 3 12-16 17 -- Iss

SD 0(R2), F6 4 17 -- Iss

ADDI R1, R1, #8 4 5 6 -- Write

ADDI R2, R2, #8 5 6 7 -- Write

SGTI R3, R1, done 5 7 8 -- Write

BEQZ R3, foo 6 9 Write

LD F2, 0(R1 ) 7 8 9 -- Write

MULTD F4, F2, F0 8 10-16 18 -- Iss

LD F6, 0(R2) 8 9 10 -- Write

ADDD F6, F4, F6 9 19-23 24 -- Iss

SD 0(R2), F6 10 24 -- Iss

ADDI R1, R1, #8 10 11 12 -- Exe

ADDI R2, R2, #8 11 12 13 -- Iss

SGTI R3, R1, done 11 13 14 -- Iss

BEQZ R3, foo 12 15

Estaciones de Reserva (Sólo FLP, al comienzo del ciclo 12)

Estado Opera Vj Vk Qj Qk Destino

ADD1 Ocup ADDD -- (F4) -- (F6) #2 #3 #4

ADD2 Ocup ADDD -- -- (F6) #11 #12 #13

ADD3 Libre

MUL1 Libre MULTD F2 F0 -- -- #2

MUL2 Ocup MULTD -- (F2) F0 #10 -- #11

Buffer de Reordenamiento (Al comienzo del ciclo 12)

Estado Instrucción Estado Destino Valor

1 libre LD F2,0(R1) Commit F2 M(0+(R1))

2 ocup MULTD F4,F2,F0 Write res F4 F2 x F0

3 ocup LD F6,0(R2) Write res F6 M(0+(R2))

4 ocup ADD F6,F4,F6 Issue F6 #2 + #3

5 ocup SD 0(R2), F6 Issue 0+(R2) #4

6 ocup ADDI R1,R1,#8 Write res R1 R1+8

7 ocup ADDI R2,R2,#8 Write res R2 R2+8

8 ocup SGTI R3,R1,done Write res R3 done – #6

9 ocup BEQZ Write res

10 ocup LD F2,0(R1) Write res F2 M(0+(#6))

11 ocup MULTD F4,F2,F0 Iss F4 #10 x F0

12 ocup LD F6,0(R2) Write res F6 M(0+(#7))

13 ocup ADD F6,F4,F6 Issue F6 #11 + #12

14 ocup SD 0(R2), F6 Issue 0+(R2) #13

15 ocup ADDI R1,R1,#8 Exe R1 #6+8

16 ocup ADDI R2,R2,#8 Issue R2 #7+8

17 ocup SGTI R3,R1,done Issue R3 done - #15

18 ocup BEQZ

Estado de los registros FP

F0 F2 F4 F6 F8 F10 F12 …

Buffer Nº 10 11 13

Ocupado NO SI si si NO NO no

También podría gustarte

- Maldecida Con Los Trillizos AlfaDocumento205 páginasMaldecida Con Los Trillizos AlfaLupita Ramos90% (50)

- Clase Teclado e InterrupcionDocumento12 páginasClase Teclado e InterrupcionMichael MartinezAún no hay calificaciones

- Tema3 ProbSolDocumento27 páginasTema3 ProbSolMónica Sánchez RuizAún no hay calificaciones

- AIC Hoja 3 (Ejercicio 9)Documento2 páginasAIC Hoja 3 (Ejercicio 9)Lupita RamosAún no hay calificaciones

- Esquemas Soldadora de Punto Bombillos y PotenciaDocumento3 páginasEsquemas Soldadora de Punto Bombillos y PotenciaDaniel CastelblancoAún no hay calificaciones

- 05 - FpuDocumento8 páginas05 - FpuADRIAN LUCAS MAMANI MAMANIAún no hay calificaciones

- Arquitectura MIPS SIMULADORDocumento29 páginasArquitectura MIPS SIMULADORlzAún no hay calificaciones

- Parcial 2 B Cas SolDocumento7 páginasParcial 2 B Cas Solyodos90112Aún no hay calificaciones

- Ej 3-Pipeline-7Documento3 páginasEj 3-Pipeline-7Johannes RobaynaAún no hay calificaciones

- Parcial 2 B Cas SolDocumento7 páginasParcial 2 B Cas Solyodos90112Aún no hay calificaciones

- Ejercicios Unity FBD PDFDocumento3 páginasEjercicios Unity FBD PDFVictor ChipantaxiAún no hay calificaciones

- Matriz FODADocumento1 páginaMatriz FODAMarikitafea PichaAún no hay calificaciones

- Programacion de Perro GuardianDocumento2 páginasProgramacion de Perro GuardianJuan Enrique Fernandez ColodroAún no hay calificaciones

- ArmaduraDocumento7 páginasArmaduraJuliana Mejía DAún no hay calificaciones

- GL 452 + 18 Fil RetirDocumento18 páginasGL 452 + 18 Fil RetirJimmy Bill Ramirez MontoyaAún no hay calificaciones

- GL 452 + 21 Filas 2 BDDocumento21 páginasGL 452 + 21 Filas 2 BDJimmy Bill Ramirez MontoyaAún no hay calificaciones

- Mikohn SettingsDocumento5 páginasMikohn SettingsBrian Osorio MendozaAún no hay calificaciones

- Ejercicios de PertDocumento4 páginasEjercicios de PertESTEFANY ALEXANDRA HILARIO SARMIENTOAún no hay calificaciones

- Examenfinal Micro y S Emb 2023Documento3 páginasExamenfinal Micro y S Emb 2023roberto vilcaAún no hay calificaciones

- Codigo AcDocumento1 páginaCodigo AcCristina Cruz AguileraAún no hay calificaciones

- Auto IncreibleDocumento1 páginaAuto IncreibleManuel sotoAún no hay calificaciones

- Corrector RorschachDocumento6 páginasCorrector RorschachisabelcanoAún no hay calificaciones

- Rorschach LuzDocumento4 páginasRorschach LuzcarmenAún no hay calificaciones

- Interpretacion RORSCHACH LUZDocumento4 páginasInterpretacion RORSCHACH LUZcarmenAún no hay calificaciones

- P 13-20 CengelDocumento2 páginasP 13-20 CengelJuanCruzZamoraAún no hay calificaciones

- 6 Ejercicios Amplif FETDocumento5 páginas6 Ejercicios Amplif FETDannyMárquezAún no hay calificaciones

- 6 Ejercicios Amplif FET PDFDocumento5 páginas6 Ejercicios Amplif FET PDFEstebanAún no hay calificaciones

- 6 Ejercicios Amplif FET PDFDocumento5 páginas6 Ejercicios Amplif FET PDFDavid Rivera BeltránAún no hay calificaciones

- 6 Ejercicios Amplif FET PDFDocumento5 páginas6 Ejercicios Amplif FET PDFEstebanAún no hay calificaciones

- Parcial 2 A Cas SolDocumento7 páginasParcial 2 A Cas Solyodos90112Aún no hay calificaciones

- Keller Williams PremiumDocumento55 páginasKeller Williams PremiumMarino A. Marrero BaezAún no hay calificaciones

- Red Can CCM 208Documento2 páginasRed Can CCM 208alfioAún no hay calificaciones

- PLANILLASDocumento6 páginasPLANILLASJhon kennedy Castillo castroAún no hay calificaciones

- Memoria SemiconductoraDocumento11 páginasMemoria SemiconductoraBell BonAún no hay calificaciones

- Ejercicios Rorschach CompletosDocumento8 páginasEjercicios Rorschach CompletosPablo Andrés SuarezAún no hay calificaciones

- Lista de MaterialesDocumento1 páginaLista de MaterialesJuan TiradoAún no hay calificaciones

- Opera DoresDocumento2 páginasOpera Doresdanny de andradeAún no hay calificaciones

- CRONODocumento1 páginaCRONOugartetjoseAún no hay calificaciones

- Documento RecuperadoDocumento1 páginaDocumento RecuperadougartetjoseAún no hay calificaciones

- Conexión y uso de LCD 2x16 líneas en MikroCDocumento6 páginasConexión y uso de LCD 2x16 líneas en MikroCfer poloAún no hay calificaciones

- Invepo2 GRP2Documento14 páginasInvepo2 GRP2daily ramos quintoAún no hay calificaciones

- Andreilysurbina L2Documento35 páginasAndreilysurbina L2Andreilys UrbinaAún no hay calificaciones

- Formato Informe de Laboratorio - Instrumentación 3Documento4 páginasFormato Informe de Laboratorio - Instrumentación 3Valieth SanchezAún no hay calificaciones

- CPR4 Inf5Documento9 páginasCPR4 Inf5Paul EspinosaAún no hay calificaciones

- Codigo Vmlab Ejemplos Contador ExamenDocumento3 páginasCodigo Vmlab Ejemplos Contador ExamenSteve Fernandez VilchezAún no hay calificaciones

- Ejes Locales y GlobalesDocumento25 páginasEjes Locales y GlobalesVivian Edith Ruiz MejiaAún no hay calificaciones

- Analisis Matricial de PorticosDocumento25 páginasAnalisis Matricial de Porticosupcland100% (4)

- Sesión 2Documento7 páginasSesión 2EMMA DANIELA ORTIZ RUIZAún no hay calificaciones

- 2.3 Ejem de Reg W y Programa Secuencia de LedsDocumento9 páginas2.3 Ejem de Reg W y Programa Secuencia de LedsOmar Navia CondoriAún no hay calificaciones

- PR LCDDocumento4 páginasPR LCDLeonardo Daniel VelaAún no hay calificaciones

- codigosDocumento19 páginascodigosmariana luevanoAún no hay calificaciones

- Instrucciones Del Pic16f877Documento24 páginasInstrucciones Del Pic16f877Alejandra Miranda CabrejoAún no hay calificaciones

- Informe Previo Práctica-5: Pregunta 1Documento7 páginasInforme Previo Práctica-5: Pregunta 1Bf BAún no hay calificaciones

- Parrilla AdultosDocumento3 páginasParrilla AdultosbeamoonAún no hay calificaciones

- Ubica Coordenadas en El Plano MiMoDocumento1 páginaUbica Coordenadas en El Plano MiMoYael SerranosAún no hay calificaciones

- Clase de Micro Control Adores PIC16F877Documento21 páginasClase de Micro Control Adores PIC16F877Gustavo ChaconAún no hay calificaciones

- Exámenes Resueltos de Ic2 PDFDocumento54 páginasExámenes Resueltos de Ic2 PDFkikeAún no hay calificaciones

- Examen Nacional Febrero 2012Documento206 páginasExamen Nacional Febrero 2012Geovanny ArrobaAún no hay calificaciones

- Exámenes 2012-2016 Ingeniería de Computadores II UNEDDocumento175 páginasExámenes 2012-2016 Ingeniería de Computadores II UNEDDiego RiveraAún no hay calificaciones

- La Elegida Del Vampiro AKER (Spanish... (Z-LibraryDocumento61 páginasLa Elegida Del Vampiro AKER (Spanish... (Z-LibraryLupita Ramos100% (1)

- CPU Cache TLB CPIDocumento25 páginasCPU Cache TLB CPILupita RamosAún no hay calificaciones

- Simulador WinDLXDocumento33 páginasSimulador WinDLXLupita RamosAún no hay calificaciones

- Win DLXDocumento52 páginasWin DLXLupita RamosAún no hay calificaciones

- Practica 1 AtyagiDocumento14 páginasPractica 1 AtyagiLupita RamosAún no hay calificaciones