Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Teoria 5

Cargado por

Mauro CerezoDescripción original:

Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Teoria 5

Cargado por

Mauro CerezoCopyright:

Formatos disponibles

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 27

1.5 – DESCRIPCIÓN DEL FLUJO DE DATOS O RTL DE LA ARQUITECTURA

La descripción por flujo de datos o RTL (Registred Transfer Level) indica la forma en que los datos se

pueden transferir de una señal a otra, ya sea utilizando instrucciones concurrentes, o bien mediante

ecuaciones booleanas. En este tipo de descripción, no se utilizan declaraciones secuenciales IF.

Este tipo de descripción permite definir el flujo que tomarán los datos entre módulos encargados de

realizar operaciones.

En VHDL existen tres tipos de declaraciones concurrentes:

Declaraciones condicionales asignadas a una señal(when-else )

Declaraciones concurrentes asignadas a señales

Selección de una señal (with-select-when )

1.5.1 – RTL mediante declaraciones condicionales asignadas a una señal (WHEN ELSE)

Su sintaxis:

La sentencia WHEN-ELSE se utiliza para asignar

<señal> <= <asignación1> WHEN <condición1> ELSE

valores a una señal, determinando así la ejecución de <asignación2> WHEN <condición2> ELSE

una condición propia del diseño; se trata de una ...

sentencia de selección múltiple. En hardware es <asignaciónN> WHEN <condiciónN> ELSE

necesario incluir todas las opciones posibles. En este <asignaciónM>;

caso es obligatorio siempre acabar la expresión con

un ELSE. Ej2: descripción RTL de un comparador de 2

palabras de 2 bits (con When-else)

Ej1: Descripción de flujo de datos de un Multiplexor de

2 a 1 (con When-else). “En c se asigna 1

cuando a=b, caso

“En Z se asigna A cuando S0 es igual a 0, caso contrario se asigna B” contrario se asigna 0”

ENTITY mux2a1 ENTITY comp

PORT(A, B, S0: IN BIT; Z: OUT BIT); PORT(a, b: IN BIT_VECTOR(1 DOWNTO 0);

END mux2a1; c: OUT BIT);

END comp;

ARCHITECTURE mux2a1_datos OF mux2a1 IS

BEGIN ARCHITECTURE comp_datos OF comp IS

Z <= A WHEN (S0 = ‘0’) ELSE B; BEGIN

END mux2a1_datos; c <= ‘1’ WHEN (a = b) ELSE ‘0’;

END comp_datos;

Ej3: descripción flujo de datos de la compuerta AND

(con When-else). Ej4: descripción flujo de datos de la compuerta OR

(con When-else).

“En fl se asigna 1

cuando a=1 y b=1, “En fl se asigna 0

caso contrario se asigna 0”

cuando a=0 y b=0,

caso contrario se asigna 1”

ENTITY comp_and

PORT(a, b: IN BIT; fl: OUT BIT);

END comp_and; ENTITY comp_or

PORT(a, b: IN BIT; fl: OUT BIT);

ARCHITECTURE comp_and__datos OF comp_and IS END comp_or;

BEGIN

fl <= 1 WHEN (a = '1') and (b = '1') ELSE 0; ARCHITECTURE comp_or__datos OF comp_or IS

END comp_and_datos; BEGIN

fl <= 0 WHEN (a = '0') and (b = '0') ELSE 1;

END comp_or_datos;

Cartilla de la materia - Ing. Dora Mendoza

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 28

Ej5: Descripción de flujo de datos de un Multiplexor de 4 a 1 (con When-else).

ENTITY mux4a1 “En M se asigna A cuando S es igual a 00, sino

En M se asigna B cuando S es igual a 01, sino

PORT(A, B, C, D: IN BIT; S: IN BIT_VECTOR(1 DOWNTO 0); En M se asigna C cuando S es igual a 10, sino

M: OUT BIT); se asigna D”

END mux4a1;

ARCHITECTURE mux4a1_datos OF mux2a1 IS

BEGIN

M <= A WHEN (S0 = “00”) ELSE

B WHEN (S0 = “01”) ELSE

C WHEN (S0 = “10”) ELSE

D;

END mux4a1_datos;

Ej6: Descripción de flujo de datos de una función f a partir de su tabla

ENTITY funcion x y z f

PORT(x, y, z: IN BIT; f: OUT BIT); 0 0 0 0

END funcion; 0 0 1 0

ARCHITECTURE funcion_datos OF funcion IS 0 1 0 1

0 1 1 1

BEGIN

1 0 0 0

f <= ‘1’ WHEN (x = ‘0’ AND y =’1’ AND z = ‘0’) ELSE

1 0 1 1

‘1’ WHEN (x = ‘0’ AND y =’1’ AND z = ‘1’) ELSE

1 1 0 1

‘1’ WHEN (x = ‘1’ AND y =’0’ AND z = ‘1’) ELSE 1 1 1 0

‘1’ WHEN (x = ‘1’ AND y =’1’ AND z = ‘0’) ELSE

‘0’;

END funcion_datos;

1.5.2 – RTL mediante ecuaciones booleanas

Mediante ecuaciones booleanas se puede describir el comportamiento de cada una de las

compuertas del sistema. Se trata de declaraciones concurrentes asignadas a señales.

Ej1: Descripción de flujo de datos de un Multiplexor de 2 a 1 (con ecuaciones booleanas).

Y = I0. 𝑆0 + I1.S0 I0

ENTITY mux2a1 Y

I1

PORT(I0, I1, S0: IN BIT; Y: OUT BIT);

END mux2a1;

MUX 2 a 1

ARCHITECTURE mux2a1_datos _eb OF mux2a1 IS

SIGNAL int1, int2, int3: BIT; S0 Diagrama lógico

BEGIN

int1 <= NOT S0; -- o bien podría ser

int2 <= I0 AND int1; ARCHITECTURE mux2a1_datos _eb2 OF mux2a1 IS

int3 <= I1 AND S0; BEGIN

Y <= int2 OR int3; Y <= ((I0 AND NOT (S0)) OR (I1 AND S0)) ;

END mux2a1_datos_eb; END mux2a1_datos_eb;

Cartilla de la materia - Ing. Dora Mendoza

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 29

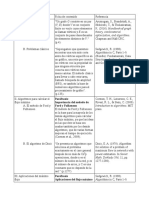

Ej2: descripción del flujo de datos de un comparador Ej3: descripción del flujo de datos con ec. Bool.

de 2 palabras de 2 bits (con ecuac. Booleanas)

f= (𝑎 + 𝑏) ⨁ 𝑐. 𝑑 )

c= (𝑎1⨁ 𝑏1) . (𝑎0 ⨁ 𝑏0) ENTITY fb

PORT(a, b, c, d: IN BIT; f: OUT BIT);

ENTITY comp

END fb;

PORT(a, b: IN BIT_VECTOR(1 DOWNTO 0); c: OUT BIT);

END comp; ARCHITECTURE fb_eb OF fb IS

BEGIN

ARCHITECTURE comp_eb OF comp IS f <= ( (a OR b) XNOR (c AND d) );

BEGIN END fb_eb;

c <= ( (a(1) XNOR b(1) ) AND (a(0) XNOR b(0) ) );

END comp_eb;

Ej4: descripción del flujo de datos con ec. Bool.

f1= (𝑎⨁𝑏)

f2 = ((𝑎⨁𝑏) + 𝑐. 𝑑). ((𝑐. 𝑑). (𝑒⨁𝑓))

f3 = (c.d).(e⨁f)

ENTITY fvarias

PORT(a, b, c, d, e, f: IN BIT; f1, f2, f3: OUT BIT);

END fvarias;

ARCHITECTURE fvarias_eb OF fb IS

BEGIN

f1 <= (a XNOR b);

f2 <=( ( (a XNOR b) OR (c AND d) ) NAND ( (c AND d) AND (e XNOR f) ) );

f3 <= (c AND d) AND (e XNOR f) ;

END fvarias_eb;

1.5.3 – RTL mediante Selección de una señal (con WITH-SELECT)

Ej1: descripción del flujo de datos de un comparador de 2

Su sintaxis:

WITH <señal1> SELECT palabras de 2 bits (con WITH)

a(1) a(0) c

<señal2> <= <expr1> WHEN <condición1>, 0 0 1

<expr2> WHEN <condición2>,

ENTITY circuito 0 1 0

...

<exprN> WHEN OTHERS; PORT(a: IN BIT_VECTOR(1 DOWNTO 0); 1 0 1

c: OUT BIT); 1 1 0

Se utiliza para asignar un valor a una señal END circuito;

con base en el valor de otra señal ARCHITECTURE circuito_datos OF circuito IS

previamente seleccionada.

BEGIN

WITH a SELECT

La cláusula WHEN OTHERS especifica c <= ‘1’ WHEN “00”,

todos los demás valores que no han sido ‘0’ WHEN “01”,

contemplados. También es posible utilizar ‘1’ WHEN “10”,

la opción que se contempló en el caso ‘0’ WHEN OTHERS;

anterior (UNAFFECTED). END circuito_datos;

Cartilla de la materia - Ing. Dora Mendoza

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 30

Ej2: descripción del flujo de datos de un circuito que

detecta números primos (con WITH)

a(3) a(2) a(1) a(0) p

0 0 0 0 0

ENTITY primo 0 0 0 1 0

PORT(a: IN BIT_VECTOR(3 DOWNTO 0); 0 0 1 0 1

p: OUT BIT); 0 0 1 1 1

END primo; 0 1 0 0 0

0 1 0 1 1

ARCHITECTURE primo_datos OF circuito IS

BEGIN 0 1 1 0 0

WITH a SELECT 0 1 1 1 1

p <= ‘1’ WHEN “0010”, 1 0 0 0 0

‘1’ WHEN “0011”, 1 0 0 1 0

‘1’ WHEN “0101”, 1 0 1 0 0

‘1’ WHEN “0111”,

1 0 1 1 1

‘1’ WHEN “1011”,

‘1’ WHEN “1101”, 1 1 0 0 0

‘0’ WHEN OTHERS; 1 1 0 1 1

END primo_datos; 1 1 1 0 0

1 1 1 1 0

Sentencia BLOCK Su sintaxis:

[block_id;]

En ocasiones interesa agrupar un conjunto de sentencias en bloques. BLOCK [expresión de guardia]

Estos bloques permiten dividir el sistema en cabecera

módulos, estos módulos pueden estar Ejemplo: declaraciones

compuestos de otros módulos. latch: BLOCK(clk='1') BEGIN

BEGIN sentencias concurrentes

q <= GUARDED d; END BLOCK block_id;

END BLOCK latch;

1.6 – DESCRIPCIÓN ESTRUCTURAL

La descripción estructural hace referencia a modelos lógicos establecidos (compuertas, sumadores,

contadores, etc). Estos pueden ser guardados para usos posteriores.

En una descripción estructural se descompone la descripción del sistema a diseñar en elementos

más simples: COMPONENTES.

Para ello:

Se definen los componentes del sistema, puede ser en una librería externa o en el mismo diseño

luego se los declara dentro de la arquitectura, usando la sentencia COMPONENT

Finalmente se los “instancia”, es decir, se asocian las señales de entrada y de salida dentro de la

arquitectura, definiendo las interconexiones entre ellos.

Sintaxis de la declaración:

COMPONENT nombre_componente IS

1.6.1 - Sentencia COMPONENT [GENERIC(lista_parametros);]

PORT (

Declaración de la sentencia Nbre_señal1: dirección tipo;

Nbre_señal2: dirección tipo;

….

Los componentes se declaran dentro de la ARQUITECTURA antes

);

de la sentencia BEGIN de la misma. La declaración es similar a la END COMPONENT nombre_componente;

de una ENTIDAD, no se define el comportamiento, sólo los

Sintaxis de la Instanciación:

puertos.

Etiqueta: nombre_componente

PORT MAP (lista_asociación_ puertos);

Cartilla de la materia - Ing. Dora Mendoza

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 31

Instanciación Puerta NAND a partir de una AND y una INV definidas en

el mismo archivo:

PORT MAP asocia los puertos del componente con -- se describe el circuito AND

señales en la arquitectura desde la que se instancia ENTITY mi_and IS

2 estilos: por posición o explícito. PORT(X, Y: IN BIT; Z: OUT BIT);

END mi_and;

Ejemplo de instanciación por posición: ARCHITECTURE circuito_miand OF mi_and IS

BEGIN

Z = X AND Y;

END circuito_miand;

-- se describe el circuito INV

Ejemplo de instanciación explícita: ENTITY mi_inv IS

U0: AND2 PORT MAP (I0=>X, I1=> Y, O =>S); PORT(X: IN BIT; Z: OUT BIT);

U1: INV PORT MAP (I=>S, O =>Z); END mi_inv;

ARCHITECTURE circuito_miinv OF mi_inv IS

BEGIN

Ej1: Descripcion estructural de una compuerta NAND Z = NOT X;

END circuito_miinv;

Puerta NAND a partir de una AND y una INV definidas en

una librería tecnológica (se incorpora automáticamente): -- se describe el circuito NAND utilizando como componentes

-- los circuitos mi_and y mi_inv

ENTITY nand2 IS Con componentes ENTITY mi_nand IS

PORT(X, Y: IN BIT; Z: OUT BIT); definido en una PORT(X, Y: IN BIT; Z: OUT BIT);

END nand2; librería externa END mi_nand;

ARCHITECTURE circuito_minand OF mi_nand IS

ARCHITECTURE circuito_nand2 OF nand2 IS

COMPONENT mi_and

SIGNAL S: BIT;

PORT (X, Y: IN BIT; Z: OUT BIT);

COMPONENT AND2 -- va a una librería tecnológica Con componentes

END COMPONENT;

PORT (I0, I1: IN BIT; O OUT BIT); definidos en el

COMPONENT mi_inv

END COMPONENT; mismo diseño

PORT (X: IN BIT; Z: OUT BIT);

COMPONENT INV -- va a una librería tecnológica END COMPONENT;

PORT (I: IN BIT; O OUT BIT);

SIGNAL Z1: BIT;

END COMPONENT;

BEGIN

BEGIN U1: mi_and PORT MAP (X, Y, Z1);

U0: AND2 PORT MAP (I0=>X, I1=> Y, O =>S); U2: mi_inv PORT MAP (Z1, Z);

U1: INV PORT MAP (I=>S, O =>Z); END circuito_minand;

END circuito_nand2;

Cartilla de la materia - Ing. Dora Mendoza

Universidad Nacional de Salta – Sede Regional Orán Asignatura: Electrónica Digital III - TEU 32

Ej2: descripción estructural de un multiplexor 2 a 1 componentes

I0

Y

I1

MUX 2 a 1

S0 Diagrama lógico

-- diseño de la estructura “inversor”

ENTITY inve

PORT(e1: IN BIT; s1: OUT BIT); -- diseño del multiplexor

END inve;

ENTITY mux2a1

ARCHITECTURE inv_estr OF inve IS PORT(S0, I0, I1: IN BIT; Y: OUT BIT);

BEGIN END mux2a1;

s1<= not e1;

END inv_estr; ARCHITECTURE mux_estructural OF mux2a1 IS

SIGNAL int1, int2, int3: bit;

-- diseño de la estructura “and2” COMPONENT inve

ENTITY and2 PORT(e1: IN BIT; s1: OUT BIT);

PORT(e1, e2: IN BIT; s1: OUT BIT); END COMPONENT;

END and2;

COMPONENT and2

ARCHITECTURE and2_estr OF and2 IS PORT(e1, e2: IN BIT; s1: OUT BIT);

BEGIN END COMPONENT;

s1<= e1 and e2;

END and2_estr; COMPONENT or2

PORT(e1, e2: IN BIT; s1: OUT BIT);

-- diseño de la estructura “or2” END COMPONENT;

ENTITY or2

PORT(e1, e2: IN BIT; s1: OUT BIT); BEGIN

END or2; U0: inve PORT MAP(S0, int1);

U1: and2 PORT MAP(I0, int1, int2);

ARCHITECTURE or2_estr OF or2 IS

U2: and2 PORT MAP(I1, S0, int3);

BEGIN

U3: or2 PORT MAP(int2, int3, Y);

s1<= e1 or e2;

END mux_estructural;

END or2_estr;

Conclusión

El tipo de descripción a utilizar depende del diseñador y de la complejidad del proyecto. Por ejemplo,

un diseño puede describirse por medio de ecuaciones booleanas, pero si es muy extenso quizá sea

más apropiado emplear estructuras jerárquicas para dividirlo; ahora bien, si se requiere diseñar un

sistema cuyo funcionamiento dependa solo de sus entradas y salidas, es conveniente utilizar la

descripción funcional, la cual presenta la ventaja de requerir menos instrucciones y el diseñador no

necesita un conocimiento previo de cada componente del circuito.

Ver video

https://www.youtube.com/watch?v=3N_R_SNnC60

https://www.youtube.com/watch?v=ozEm_OHvvgM

https://www.youtube.com/watch?v=9D6fCuQB_Wk

Cartilla de la materia - Ing. Dora Mendoza

También podría gustarte

- .4 - Descripción Del Comportamiento o Funcional de La ArquitecturaDocumento5 páginas.4 - Descripción Del Comportamiento o Funcional de La ArquitecturaMauro CerezoAún no hay calificaciones

- Programas VHDLDocumento4 páginasProgramas VHDLErikson Barreda LopezAún no hay calificaciones

- FDP Volumen 2Documento13 páginasFDP Volumen 2Proyectos DecimatensionAún no hay calificaciones

- Compuerta and o MultiplicadoraDocumento14 páginasCompuerta and o Multiplicadoragerman ramosAún no hay calificaciones

- Circuitos Combinacionales VHDLDocumento20 páginasCircuitos Combinacionales VHDLNick CohechaAún no hay calificaciones

- Informe #2 Sistemas Digitales 1Documento5 páginasInforme #2 Sistemas Digitales 1Juan Sebastian Chicangana MontoyaAún no hay calificaciones

- Circuitos MsiDocumento27 páginasCircuitos MsiemerAún no hay calificaciones

- APUNTES PROGRAMACION TIA PORTAL (Autoguardado)Documento19 páginasAPUNTES PROGRAMACION TIA PORTAL (Autoguardado)Tomas CabreraAún no hay calificaciones

- Tarea 1 - Jose Elias ArandaDocumento11 páginasTarea 1 - Jose Elias ArandaJose Elias Aranda MendezAún no hay calificaciones

- Tarea de Discretas Compuertas LogicasDocumento7 páginasTarea de Discretas Compuertas LogicasBryanAún no hay calificaciones

- Multiplexor 8 A 1 VHDLDocumento2 páginasMultiplexor 8 A 1 VHDLWilmer Patricio0% (1)

- Ejercicios Resueltos VHDLDocumento13 páginasEjercicios Resueltos VHDLAnonymous VC5mhPT2GAún no hay calificaciones

- Programacion Deber#1Documento12 páginasProgramacion Deber#1Frey SebastianAún no hay calificaciones

- Características Físicas de Las Compuertas LógicasDocumento5 páginasCaracterísticas Físicas de Las Compuertas LógicasJuan CifuentesAún no hay calificaciones

- Logica Mixta PDFDocumento5 páginasLogica Mixta PDFanon_170968622Aún no hay calificaciones

- 5.1 Descripción Circuital VHDLDocumento5 páginas5.1 Descripción Circuital VHDLCarlos Andres FigueroaAún no hay calificaciones

- Compuertas LogicasDocumento10 páginasCompuertas LogicasSantiago BustamanteAún no hay calificaciones

- TP1 Parte 2 UALDocumento3 páginasTP1 Parte 2 UALFacundo Dufrechou100% (1)

- Taller "Identificar Las Compuertas Lógicas en Los Diseños de Circuitos".Documento13 páginasTaller "Identificar Las Compuertas Lógicas en Los Diseños de Circuitos".Manuel ContrerasAún no hay calificaciones

- S7 Programación Avanzada 1Documento7 páginasS7 Programación Avanzada 1TatsuDOAún no hay calificaciones

- ISLD Cursada 2020. Ejemplos de Diseño en VHDL. Anexo para PARTE 1 y 2Documento14 páginasISLD Cursada 2020. Ejemplos de Diseño en VHDL. Anexo para PARTE 1 y 2Dward NoizeAún no hay calificaciones

- Informe Desarrollo Diagramas de Contacto en Las PLC PDFDocumento18 páginasInforme Desarrollo Diagramas de Contacto en Las PLC PDFpedro jjenney pulido puinAún no hay calificaciones

- C3 - Logica Digital-1Documento43 páginasC3 - Logica Digital-1Alexander IbarraAún no hay calificaciones

- Apunte3 Organizacion de Computadoras Informatica UNLPDocumento6 páginasApunte3 Organizacion de Computadoras Informatica UNLPJonnyBirraAún no hay calificaciones

- Circuitos Digitales Tema3Documento27 páginasCircuitos Digitales Tema3Andrea AsisAún no hay calificaciones

- Curso VHDLDocumento27 páginasCurso VHDLedsonAún no hay calificaciones

- Luis Amaris 30Documento12 páginasLuis Amaris 30Karen Yiseth Salas AsprillaAún no hay calificaciones

- Trabajo BodeDocumento11 páginasTrabajo BodeEdixon PiñaAún no hay calificaciones

- Compuertas LogicasDocumento4 páginasCompuertas LogicasMikeAún no hay calificaciones

- Resumen ArquitecturaDocumento12 páginasResumen ArquitecturaLuca NicolÁs OrellanaAún no hay calificaciones

- Reglas Básicas de Programación en VHDLDocumento4 páginasReglas Básicas de Programación en VHDLCesar David Arango OsorioAún no hay calificaciones

- PreTarea Oscar Bahoz 243004 4Documento10 páginasPreTarea Oscar Bahoz 243004 4Oscar BahozAún no hay calificaciones

- Tarea 4Documento6 páginasTarea 4Samuel AcostapichardoAún no hay calificaciones

- Lenguajes Máquina y EnsambladorDocumento29 páginasLenguajes Máquina y EnsambladorLuisdceo LggAún no hay calificaciones

- Transformada de LaplaceDocumento58 páginasTransformada de LaplaceAlvin YaquitoryAún no hay calificaciones

- InvestigaciónDocumento17 páginasInvestigacióncamila ramirezAún no hay calificaciones

- Fundamentos Algebra BoleanaDocumento58 páginasFundamentos Algebra BoleanaAlvaro BeltranAún no hay calificaciones

- Circuitos Lógicos y Álgebra BooleanaDocumento6 páginasCircuitos Lógicos y Álgebra BooleanaJohansenAún no hay calificaciones

- Funciones Booleanas y Sus PropiedadesDocumento11 páginasFunciones Booleanas y Sus PropiedadesSara juliana Varela GutiérrezAún no hay calificaciones

- Tema 3. - Práctica 1 SumadorDocumento8 páginasTema 3. - Práctica 1 SumadorDanny PérezAún no hay calificaciones

- Compuertas Lógicas Con BJT.Documento5 páginasCompuertas Lógicas Con BJT.ElSantoAún no hay calificaciones

- Familias Logicas TTL y CMOSDocumento8 páginasFamilias Logicas TTL y CMOSLeslie MedinaAún no hay calificaciones

- 2 - Diseno Logico Combinacional Mediante VHDLDocumento21 páginas2 - Diseno Logico Combinacional Mediante VHDLGenus ArangurenAún no hay calificaciones

- TALLER 1 DIGITALES II - VDocumento8 páginasTALLER 1 DIGITALES II - VJose Elias Perafan LealAún no hay calificaciones

- 2020.06.15.examen IC3.Aula Virtual de Examen. UNED PDFDocumento2 páginas2020.06.15.examen IC3.Aula Virtual de Examen. UNED PDFDon LimonAún no hay calificaciones

- 2020.06.15.examen IC3.Aula Virtual de Examen. UNEDDocumento2 páginas2020.06.15.examen IC3.Aula Virtual de Examen. UNEDDon LimonAún no hay calificaciones

- Practica 6Documento12 páginasPractica 6hector blancoAún no hay calificaciones

- 2b Tipos de Descripcion VHDLDocumento13 páginas2b Tipos de Descripcion VHDLalejandro delgadoAún no hay calificaciones

- Actividad 1 - Compuertas Lógicas PDFDocumento5 páginasActividad 1 - Compuertas Lógicas PDFJohn Harold BenavidesAún no hay calificaciones

- Actividad 1 - Compuertas Lógicas PDFDocumento5 páginasActividad 1 - Compuertas Lógicas PDFJohn Harold BenavidesAún no hay calificaciones

- Compuertas LogicasDocumento5 páginasCompuertas Logicasmarioromo100% (3)

- Practica 06 Espacio-EstadoDocumento16 páginasPractica 06 Espacio-EstadoRogelio Diaz BravoAún no hay calificaciones

- TallerIdentificar Las Compuertas Lógicas en Los Diseños de circuitosGeisembergZamoraDocumento9 páginasTallerIdentificar Las Compuertas Lógicas en Los Diseños de circuitosGeisembergZamoraGeisemberg ZamoraAún no hay calificaciones

- Clase11 - Electronica II - Unidad - 2Documento18 páginasClase11 - Electronica II - Unidad - 2Pablo Carrasco ContrerasAún no hay calificaciones

- Sistemas DigitalesDocumento9 páginasSistemas DigitalesBelen MenesAún no hay calificaciones

- Ejericios Propuestos VHDLDocumento8 páginasEjericios Propuestos VHDLShaadAún no hay calificaciones

- Taller para EnviarDocumento9 páginasTaller para EnviarKevin Pinto Vencedores SemillasAún no hay calificaciones

- 19A Conceptos Iniciales para Armar Un ContadorDocumento9 páginas19A Conceptos Iniciales para Armar Un ContadorGastón CapdevilaAún no hay calificaciones

- 1.7 - Diseño Logico Secuencial en VHDLDocumento5 páginas1.7 - Diseño Logico Secuencial en VHDLMauro CerezoAún no hay calificaciones

- 1.3 - Fundamentos Del Lenguaje VHDLDocumento7 páginas1.3 - Fundamentos Del Lenguaje VHDLMauro CerezoAún no hay calificaciones

- Estudio de Caso: Fpga de XilinxDocumento7 páginasEstudio de Caso: Fpga de XilinxMauro CerezoAún no hay calificaciones

- Procesadores DigitalesDocumento7 páginasProcesadores DigitalesMauro CerezoAún no hay calificaciones

- Programming Software Plus 7.7 User GuideDocumento94 páginasProgramming Software Plus 7.7 User GuideJhony SFAún no hay calificaciones

- LAB 006 Activity Create LoopsDocumento10 páginasLAB 006 Activity Create LoopsJUAN JOSE REYES CUEROAún no hay calificaciones

- Teclado InformaticaDocumento8 páginasTeclado InformaticaLordgatito BerracoAún no hay calificaciones

- Tipos de Diagramas BPMNDocumento9 páginasTipos de Diagramas BPMNVictorCotaQuinteroAún no hay calificaciones

- Clase 01 - Excel Basico (Autoguardado)Documento21 páginasClase 01 - Excel Basico (Autoguardado)Vannesa GtAún no hay calificaciones

- 1 Procedimiento Administración de SoftwareDocumento18 páginas1 Procedimiento Administración de Softwareedwin valenciaAún no hay calificaciones

- Instala Modem Internet en Casa v3Documento1 páginaInstala Modem Internet en Casa v3julio cesar zamoaAún no hay calificaciones

- Clase Magistral 03 Mar 2021Documento12 páginasClase Magistral 03 Mar 2021Isabella FerreiraAún no hay calificaciones

- Foro de EstructuraDocumento3 páginasForo de EstructuragatoKENAún no hay calificaciones

- Actividad 4-Metodos Web Que Retornan Data JSONDocumento3 páginasActividad 4-Metodos Web Que Retornan Data JSONprimer cuentaAún no hay calificaciones

- Laboratorio 04Documento32 páginasLaboratorio 04hatun_nanAún no hay calificaciones

- Datasheet Cerbo GX GX Touch ESDocumento2 páginasDatasheet Cerbo GX GX Touch ESDavid BenaventeAún no hay calificaciones

- Eficiencia de AlgoritmosDocumento9 páginasEficiencia de AlgoritmosAlejandro CipamochaAún no hay calificaciones

- Poo Final PracticoDocumento14 páginasPoo Final PracticoTomas Carrillo ZuletaAún no hay calificaciones

- TP RAID InfoDocumento5 páginasTP RAID InfoMaria Quimey BuczyñskiAún no hay calificaciones

- AaaDocumento10 páginasAaaIgnacioo QuezadaAún no hay calificaciones

- Automatas y Lenguajes FormalesDocumento6 páginasAutomatas y Lenguajes FormalesJepe TorresAún no hay calificaciones

- Reporte de Practica 2 YaskawuaDocumento7 páginasReporte de Practica 2 YaskawuaAngel RiveraAún no hay calificaciones

- Ejemplos de Procesos de Modelos de SoftwareDocumento3 páginasEjemplos de Procesos de Modelos de Softwarejate29Aún no hay calificaciones

- Datos Del Docente Nombre Y Apellido Cédula Teléfono Correo ElectrónicoDocumento1 páginaDatos Del Docente Nombre Y Apellido Cédula Teléfono Correo ElectrónicoEduardo SalazarAún no hay calificaciones

- Proyecto 1-Explorando La Integridad en Ciberespacio RespuestaDocumento7 páginasProyecto 1-Explorando La Integridad en Ciberespacio RespuestaEli kiotoAún no hay calificaciones

- Practica 2 AB 2022-1Documento10 páginasPractica 2 AB 2022-1Adrian Aaron Medrano VargasAún no hay calificaciones

- 5s Herramientas Informaticas OnceDocumento1 página5s Herramientas Informaticas OnceAndrés LagosAún no hay calificaciones

- Formularios en HTMLDocumento10 páginasFormularios en HTMLAndroid AppsAún no hay calificaciones

- Pyton Basico TemarioDocumento4 páginasPyton Basico TemarioGabriel Alexander Guillerhua MalpartidaAún no hay calificaciones

- Práctica de Laboratorio NETSTATDocumento4 páginasPráctica de Laboratorio NETSTATIngRichard Inoa JimenezAún no hay calificaciones

- Ejemplos de Fichas de ContenidoDocumento2 páginasEjemplos de Fichas de ContenidoEduardo Augusto MayorgaAún no hay calificaciones

- MF0492 3-Uf1846Documento65 páginasMF0492 3-Uf1846Francisco Jose Nieto GarciaAún no hay calificaciones

- ch03 TodoDocumento17 páginasch03 TodoJOSE TOMAS CHINER PUCHADESAún no hay calificaciones

- Cómo Programar Un PicDocumento16 páginasCómo Programar Un PicKarla Sandoval GarciaAún no hay calificaciones