Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CPLD

Cargado por

Adriana Elorza Ramos0 calificaciones0% encontró este documento útil (0 votos)

11 vistas6 páginasUn CPLD (Dispositivo Lógico Programable Complejo) contiene múltiples bloques lógicos similares a PLDs que se comunican a través de una matriz programable de interconexiones. Los CPLDs permiten implementar sistemas más eficientes que utilizan menos espacio y reducen costos en comparación con PLDs. Los CPLDs consisten en bloques lógicos, macroceldas, y una matriz de interconexiones programables que conecta las entradas, salidas y bloques lógicos.

Descripción original:

Complex PLD's

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoUn CPLD (Dispositivo Lógico Programable Complejo) contiene múltiples bloques lógicos similares a PLDs que se comunican a través de una matriz programable de interconexiones. Los CPLDs permiten implementar sistemas más eficientes que utilizan menos espacio y reducen costos en comparación con PLDs. Los CPLDs consisten en bloques lógicos, macroceldas, y una matriz de interconexiones programables que conecta las entradas, salidas y bloques lógicos.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

11 vistas6 páginasCPLD

Cargado por

Adriana Elorza RamosUn CPLD (Dispositivo Lógico Programable Complejo) contiene múltiples bloques lógicos similares a PLDs que se comunican a través de una matriz programable de interconexiones. Los CPLDs permiten implementar sistemas más eficientes que utilizan menos espacio y reducen costos en comparación con PLDs. Los CPLDs consisten en bloques lógicos, macroceldas, y una matriz de interconexiones programables que conecta las entradas, salidas y bloques lógicos.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 6

Dispositivos Programables Complejo (CPLD)

INTRODUCCION

Un CPLD (del acrónimo inglés Complex Programmable Logic Device) es un dispositivo

electrónico. Extienden el concepto de un PLD (del acrónimo inglés Programmable Logic

Device) a un mayor nivel de integración ya que permite implementar sistemas más eficaces, ya

que utilizan menor espacio, mejoran la fiabilidad del diseño, y reducen costos. Un CPLD se

forma con múltiples bloques lógicos, cada uno similar a un PLD. Los bloques lógicos se

comunican entre sí utilizando una matriz programable de interconexiones, lo cual hace más

eficiente el uso del silicio, conduciendo a una mejor eficiencia a menor costo.

Las PAL y PLA son útiles para implementar una gran variedad de pequeños/medianos circuitos

digitales (Entradas más salidas que no superen el numero de 32). Cuando se requiere mayor

cantidad de entradas/salidas se recurre a un CPLD (Complex Programmable Logic Devices)

¿Qué es un PAL y PLA?

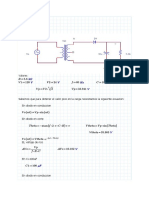

Basada en la idea de que una función lógica puede ser realizada como una suma de productos,

una PLA, comprende un conjunto (arreglo – array) de compuertas AND que alimentan un

arreglo de compuertas OR – Un esquema circuital se muestra en la Fig.3. En esta figura se

observa que cada entrada a la compuerta AND se puede programar (conectar o nó).

Como hemos visto en las PLAs ambos arreglos (planos AND y OR) son programables. Esto

tiene dos dificultades para el fabricante. En primer lugar, es de fabricación compleja por la

cantidad de llaves, por otro lado, son poco veloces. Este problema los llevo a mejorar el diseño

y desarrollaron un dispositivo de arreglo AND programable y OR fijo. Esta estructura se

denomina Programmable Array Logic. La PAL ofrece menos flexibilidad que la PLA debido a

que tiene un arreglo fijo (OR). La PLA permite hasta 4 términos producto por compuerta OR,

mientras que la PAL solo 2.

¿Cómo funciona un CPLD?

Un CPLD en el fondo no es más que una versión mejorada y por tanto más compleja de un

dispositivo PLD. ¿Qué son los dispositivos PLD? Los hemos dicho antes y son los que en su

día eran conocidos como PLA.

Un CPLD no es más que una serie de PLA como función de entrada, pero sus puertas OR no

generan una salida, sino que su salida es distribuida a través de una matriz que conecta con

otra serie de funciones PLA, las cuales pueden dar un resultado de salida o retroalimentar en

dirección contraria.

En un CPLD por tanto, todas las funciones lógicas posibles se encuentran codificadas en los

diferentes PLA que se van combinando para conseguir así la función final que se quiere

obtener. En general en diseño de nuevos procesadores los CPLD se utilizan tanto para simular

la lógica combinacional como la función fija, mientras que los FPGA se utilizan para la lógica

secuencial y elementos más complejos como son por ejemplo las ALUs. Como curiosidad, las

unidades de descodificación instrucciones de CPUs y GPU se suelen implementar primero en

CPLD, dado que en el fondo no son más que circuitos combinacionales.

¿Qué es un CPLD y cómo se compara con un FPGA?

Los FPGA están mejor preparados para simular hardware que depende del tiempo,

ciclos de reloj, mientras que un CPLD está más pensado para lo que con circuitos

combinacionales y que por tanto no dependen de una secuencia de pasos por ciclo.

En un CPLD el tiempo que tarda una función sintetizada en el mismo será siempre el

mismo, en un FPGA no. De ahí a que se utilicen los CPLD para diseñar circuitería

combinacional.

Los FPGA están pensados como productos de muy alta gama y por tanto con un alto

coste. Los CPLD al contrario.

Los FPGA pueden funcionar a velocidades de reloj mucho más altas que un CPLD.

Un FPGA necesita ser reprogramado cada vez que es encendido, ya que se

desprograma al apagarse, un CPLD funciona como una ROM y no va a perder su

configuración al apagarse el dispositivo. Esto significa que los FPGA se basan en

memoria RAM en su arquitectura y los CPLD en memoria ROM.

Por lo que nunca vamos a ver algo complejo como una CPU implementado en un CPLD, dado

que no están pensados para ello. A día de hoy los CPLD se suelen integrar dentro de placas de

desarrollo FPGA, por lo que es común combinar ambos tipos de circuitería programable.

Caracteristicas

CPLDS contiene el equivalente de varios PALs/ GALs

connectados por interconnecciones programmables.

CPLDs pueden reemplazar miles o cientos de miles compuertas lógicas.

El tiempo de E/S del CPLD es predecible debido a su simple

estructura de interconecciones

CPLDs contienen 16-1024 macroceldas

cada macrocelda equivale a unas 20/40 compuertas (incluyendo un Flip/Flop

programable)

puede tener desde 20 hasta 381 I/Os

hay un trade-off entre el espacio para las macroceldas y el

espacio para las interconecciones

Programación de los CPLDs

Opciones de Programación:

one-time programmable:

el dispositivo es programado una vez y mantiene su

programación para siempre

usualmente usa fusible para crear/romper una unión de

interconección

no se puede re-programar, pero normalmente es muy

barato

si se debe hacer alguna modificación a la lógica interna

del CPLD, el dispositivo se descarta y se usa uno nuevo

(no programado)

Borrable por UV:

la programación del CPLD es borrada por emisión UV

tiene un encapsulado cerámico con una ventana arriba del área del chip

este encapsulado especial es bastante caro

normalmente se debe remover el CPLD del zócalo para borrarlo/reprogramarlo

programación es retenida después de cortar Vcc (no-volatile)

programación/borrado es limitada a unos 1000s ciclos

Borrable eléctricamente:

borrado y programado del CPLD se hace con una corriente eléctrica

el CPLD puede ser programado/borrado en el PCB, no es necesario encapsulado

especial o zócalo

tiempo de borrado es mucho menor que el borrado UV

no-volatile

programación/borrado es limitada a unos 1000s ciclos

CLASIFICACIÓN DE LOS PLD (ARQUITECTURA) :

PROM (Memoria programable de sólo

lectura)

PLA (Arreglo lógico programable)

PAL (Lógica de arreglos programables)

GAL (Arreglo lógico genérico)

CPLD (Dispositivo lógico programable

complejo)

FPGA (Arreglos de compuertas

programables mediante campos)

Arquitectura

Matriz de Interconexiones Programables[editar]

Procesador de un CPLD de la marca Altera.

La matriz de interconexiones programables (PIM) permiten unir los pines de entrada/salida a

las entradas del bloque lógico, o las salidas del bloque lógico a las entradas de otro bloque

lógico o inclusive a las entradas del mismo. La mayoría de los CPLDs usan una de dos

configuraciones para esta matriz: interconexión mediante bloques o interconexión

mediante multiplexores.

El primero se basa en una matriz de filas y columnas con una celda programable de conexión

en cada intersección. Al igual que en las GAL esta celda puede ser activada para

conectar/desconectar la correspondiente fila y columna. Esta configuración permite una total

interconexión entre las entradas y salidas del dispositivo o bloques lógicos. Sin embargo, estas

ventajas provocan que disminuya el rendimiento del dispositivo, además de aumentar el

consumo de energía y el tamaño del componente.

En la interconexión mediante multiplexores, existe un multiplexor por cada entrada al bloque

lógico. Las vías de interconexión programables son conectadas a las entradas de un número

de multiplexores por cada bloque lógico. Las líneas de selección de estos multiplexores son

programadas para permitir que sea seleccionada únicamente una vía de la matriz de

interconexión por cada multiplexor la cual se propagara a hacia el bloque lógico. Cabe

mencionar que no todas las vías son conectadas a las entradas de cada multiplexor. La

rutabilidad se incrementa usando multiplexores de mayor tamaño, permitiendo que cualquier

combinación de señales de la matriz de interconexión pueda ser enlazada hacia cualquier

bloque lógico. Sin embargo, el uso de grandes multiplexores incrementa el tamaño de

dispositivo y reduce su eficiencia.

Bloques Lógicos

Un bloque lógico es similar a un PLD, cada uno pose un bloque de compuertas AND y OR en

forma de suma de productos, una configuración para la distribución de estas sumas de

productos, y macroceldas. El tamaño del bloque lógico es una medida de la capacidad del

CPLD, ya que de esto depende el tamaño de la función booleana que pueda ser implementada

dentro del bloque. Los bloques lógicos usualmente tienen de 4 a 20 macroceldas.

Macroceldas

Las macroceldas de un CPLD son similares a las de un PLD. Estas también están provistas

con registros, control de polaridad, y buffers para salidas en alta impedancia. Por lo general un

CPLD tiene macroceldas de entrada/salida, macroceldas de entrada y macroceldas internas u

ocultas (buried macrocells), en tanto que un 22V10 tiene solamente macroceldas de

entrada/salida. Una macrocelda interna es similar a una macrocelda de entrada/salida, solo que

esta no puede ser conectada directamente a un pin de salida. La salida de una macrocelda

interna va directamente a la matriz de interconexión programable.

Celda de entrada/salida

La función de una celda de entrada/salida es permitir el paso de una señal hacia dentro o hacia

el exterior del dispositivo. Dependiendo del fabricante y de la arquitectura del CPLD estas

celdas pueden o no ser consideradas parte del bloque lógico.

ARQUITECTURA DE LOS CPLDS DE ALTERA

CPLD MAX 7000

Su Arquitectura de un CPLD es la forma en que están organizados y a la disposición a los

elementos internos del dispositivo. Son similares al diagrama de bloque de un CPLD genérico,

Teniendo la estructura clásica PAL/GAL que nos permite generar las funciones suma de

producto. Su densidad varía entre dos bloques LAB y 16 bloques LAB, dependiendo del

dispositivo concreto de la serie que se vaya a utilizar.1

Un bloque LAB es similar a un SPLD y que el tamaño de los encapsulados varía entre 44 y 208

pines, cabe mencionar que utilizan una tecnología de proceso basada en EEPROM. Las

versiones que se pueden programar dentro del sistema para ello se utilizan la interfaz estándar

JTAG.

*EJEMPLOD DEL PDF CPLDS

También podría gustarte

- CPLDDocumento27 páginasCPLDKevin Maldonado100% (1)

- P Rogramcion en CPLD Con PLDDocumento27 páginasP Rogramcion en CPLD Con PLDfrandyAún no hay calificaciones

- Las CPLDDocumento4 páginasLas CPLDEvelyn MoranAún no hay calificaciones

- CPLD IntroduccionDocumento12 páginasCPLD IntroduccionJared Barrera ParedesAún no hay calificaciones

- Dispositivos Lógicos Programables (PLD)Documento4 páginasDispositivos Lógicos Programables (PLD)DAVID ALEJANDRO JUAREZ AGUAYOAún no hay calificaciones

- FPGADocumento28 páginasFPGAjosedavid0115Aún no hay calificaciones

- PLDDocumento4 páginasPLDJuan Camilo GarzonAún no hay calificaciones

- P3 - PLD, CPLD Y FPGA'sDocumento20 páginasP3 - PLD, CPLD Y FPGA'sReséndiz Nieto Melanie GabrielaAún no hay calificaciones

- Jorland Arias Lopez 223228Documento9 páginasJorland Arias Lopez 223228Jorland AriasAún no hay calificaciones

- Dispositivos Logicos ProgramablesDocumento15 páginasDispositivos Logicos ProgramablesjcolmenaresrAún no hay calificaciones

- 1programación de FPGA SDocumento28 páginas1programación de FPGA SHIGH SAPIENSAún no hay calificaciones

- 2programación de FPGA S o CpldsDocumento28 páginas2programación de FPGA S o CpldsHIGH SAPIENSAún no hay calificaciones

- Compuertas DigitalesDocumento4 páginasCompuertas DigitalesBRAYAN ANDRES RODRIGUEZ ACOSTAAún no hay calificaciones

- Dispositivos Lógicos ProgramablesDocumento4 páginasDispositivos Lógicos ProgramablesEspinosa L EriickAún no hay calificaciones

- PLDDocumento16 páginasPLDDeyvis Luque ApazaAún no hay calificaciones

- Que Es Una CPLDDocumento2 páginasQue Es Una CPLDEsteban Eduardo EcAún no hay calificaciones

- Electronica Digital para El Mapa MentalDocumento7 páginasElectronica Digital para El Mapa MentalMaria BeltranAún no hay calificaciones

- Caracteristicas de Dispositivos Logicos ProgramablesDocumento9 páginasCaracteristicas de Dispositivos Logicos ProgramablesAntonio GamboaAún no hay calificaciones

- Sistemas Digitales Programables (PLD)Documento9 páginasSistemas Digitales Programables (PLD)andyAún no hay calificaciones

- 4.1.2 Forma de Programar Los PLD S. Rios HernandezDocumento3 páginas4.1.2 Forma de Programar Los PLD S. Rios HernandezJazziel Issui Rios HernandezAún no hay calificaciones

- Dispositivos Lógicos ProgramablesDocumento13 páginasDispositivos Lógicos ProgramablesNestor Victoria SantiagoAún no hay calificaciones

- Investigacion Circuitos Digitales ArmandoDocumento5 páginasInvestigacion Circuitos Digitales ArmandoDavid PerezAún no hay calificaciones

- Dig - 1-Logica ProgramableDocumento92 páginasDig - 1-Logica ProgramableENIC-AITCGAún no hay calificaciones

- Dispositivos ProgramablesDocumento5 páginasDispositivos ProgramablesWilsen HernandezAún no hay calificaciones

- GalDocumento17 páginasGalMox HernandezAún no hay calificaciones

- CPDL y FpgaDocumento8 páginasCPDL y FpgaLeonel López Romero100% (1)

- Caracteristicas - de - Los - PLD - S.PDF Filename UTF-8''Caracteristicas de Los PLD - S PDFDocumento31 páginasCaracteristicas - de - Los - PLD - S.PDF Filename UTF-8''Caracteristicas de Los PLD - S PDFcristoferAún no hay calificaciones

- Dispositivos Logicos Programables (PLDS)Documento16 páginasDispositivos Logicos Programables (PLDS)Yhony LuqueAún no hay calificaciones

- Unidad 4 Principios ElectricosDocumento16 páginasUnidad 4 Principios ElectricosUriel Guerrero PerezAún no hay calificaciones

- GAL y PLDDocumento24 páginasGAL y PLDpreguntonmilAún no hay calificaciones

- Donde Se Utiliza Un PLDDocumento2 páginasDonde Se Utiliza Un PLDCarlos MontoyaAún no hay calificaciones

- CPLD (Monografia)Documento20 páginasCPLD (Monografia)Isaías Daniel CabanaAún no hay calificaciones

- A8Documento15 páginasA8fer6669993Aún no hay calificaciones

- 1.6 Programación de FPGA o CPLD en Diferentes AplicacionesDocumento4 páginas1.6 Programación de FPGA o CPLD en Diferentes AplicacionesEL JEFAZO0Aún no hay calificaciones

- Contador de Personas Sistemas EmbebidosDocumento24 páginasContador de Personas Sistemas EmbebidosJuan Carlos Cornejo Castro100% (1)

- CPLDDocumento19 páginasCPLDAle EvnAún no hay calificaciones

- Arquitectura PLDDocumento11 páginasArquitectura PLDAlejandro RodríguezAún no hay calificaciones

- PLDDocumento3 páginasPLDRoberto MartinezAún no hay calificaciones

- Fpga y PLD, VHDL y VerilogDocumento6 páginasFpga y PLD, VHDL y VerilogLuis PintadoAún no hay calificaciones

- Electronica Digital FPGAsDocumento6 páginasElectronica Digital FPGAsHerver GustavoAún no hay calificaciones

- Dispositivos Lógicos Programables (PLD)Documento21 páginasDispositivos Lógicos Programables (PLD)peralesperalesAún no hay calificaciones

- Exposicion PLDSDocumento46 páginasExposicion PLDSJaime Almeyda RuedaAún no hay calificaciones

- VillalobosDocumento12 páginasVillalobosBrandon FuentesAún no hay calificaciones

- VHDL para La Simulacion de Circuitos SecuencialesDocumento2 páginasVHDL para La Simulacion de Circuitos SecuencialesfrandyAún no hay calificaciones

- Lógica ProgramadaDocumento6 páginasLógica ProgramadaJOSE MARIA CAHUANA HUANCAAún no hay calificaciones

- PLD SDocumento23 páginasPLD SMario Caleb Alvarez OlivasAún no hay calificaciones

- 1 FpgaDocumento25 páginas1 FpgaJuan David MurilloAún no hay calificaciones

- Dispositivos Lógicos ProgramablesDocumento15 páginasDispositivos Lógicos ProgramablesPaloma RodriguezAún no hay calificaciones

- 4.1.2 Forma de Programar Los PLD S. Rios HernandezDocumento4 páginas4.1.2 Forma de Programar Los PLD S. Rios HernandezJazziel Issui Rios HernandezAún no hay calificaciones

- PLDDocumento3 páginasPLDLeon CasanovaAún no hay calificaciones

- Dispositivos Logicos ProgramablesDocumento16 páginasDispositivos Logicos ProgramablesNicolas CastilloAún no hay calificaciones

- PdlsDocumento8 páginasPdlsAlejandra HernándezAún no hay calificaciones

- Tarea N°1Documento12 páginasTarea N°1Nicolas UribeAún no hay calificaciones

- PLDDocumento31 páginasPLDFreddy JesusAún no hay calificaciones

- PLD's Dispositivos Programables EnsayoDocumento7 páginasPLD's Dispositivos Programables EnsayoDanielAún no hay calificaciones

- Qué Es Un PLDDocumento16 páginasQué Es Un PLDJezzi GL100% (1)

- CUESTIONARIO - Estado Actual de La Lógica Programable 2.0Documento2 páginasCUESTIONARIO - Estado Actual de La Lógica Programable 2.0Cesar Gerardo Del Angel De La CruzAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Prácticas de redes de datos e industrialesDe EverandPrácticas de redes de datos e industrialesCalificación: 4 de 5 estrellas4/5 (5)

- Reporte de LecturaDocumento5 páginasReporte de LecturaAdriana Elorza RamosAún no hay calificaciones

- Practica 5 NeumaticaDocumento13 páginasPractica 5 NeumaticaAdriana Elorza RamosAún no hay calificaciones

- Propuesta Micrcontroladores FinalDocumento4 páginasPropuesta Micrcontroladores FinalAdriana Elorza RamosAún no hay calificaciones

- Vibraciones Practica 1Documento23 páginasVibraciones Practica 1Adriana Elorza RamosAún no hay calificaciones

- ExposiciónDocumento14 páginasExposiciónAdriana Elorza RamosAún no hay calificaciones

- Practica 3 NeumáticaDocumento24 páginasPractica 3 NeumáticaAdriana Elorza RamosAún no hay calificaciones

- Practica 2 Neumática e HidráulicaDocumento22 páginasPractica 2 Neumática e HidráulicaAdriana Elorza RamosAún no hay calificaciones

- Practica3 - Simulacion de Una Linea de TransmisionDocumento8 páginasPractica3 - Simulacion de Una Linea de TransmisionAdriana Elorza RamosAún no hay calificaciones

- Simulacion de Circuitos Neumaticos SencillosDocumento11 páginasSimulacion de Circuitos Neumaticos SencillosAdriana Elorza RamosAún no hay calificaciones

- Instrucciones. ATMega328PpdfDocumento13 páginasInstrucciones. ATMega328PpdfAdriana Elorza RamosAún no hay calificaciones

- Practica 1Documento4 páginasPractica 1Adriana Elorza RamosAún no hay calificaciones

- Rectificador Onda Completa 6 PulsosDocumento6 páginasRectificador Onda Completa 6 PulsosAdriana Elorza RamosAún no hay calificaciones

- Registros para El ADCDocumento4 páginasRegistros para El ADCAdriana Elorza RamosAún no hay calificaciones

- FormularioDocumento8 páginasFormularioAdriana Elorza RamosAún no hay calificaciones

- Tablas Esfuerzos AGMADocumento12 páginasTablas Esfuerzos AGMAAdriana Elorza RamosAún no hay calificaciones

- Rectificador de Media Onda Con Carga RLDocumento3 páginasRectificador de Media Onda Con Carga RLAdriana Elorza RamosAún no hay calificaciones

- Tarea Rectificador Media OndaDocumento2 páginasTarea Rectificador Media OndaAdriana Elorza RamosAún no hay calificaciones

- Tablas Esfuerzos AGMADocumento12 páginasTablas Esfuerzos AGMAAdriana Elorza RamosAún no hay calificaciones

- FormularioDocumento7 páginasFormularioAdriana Elorza RamosAún no hay calificaciones

- Practica4 PotenciaDocumento3 páginasPractica4 PotenciaAdriana Elorza RamosAún no hay calificaciones

- Graficas y SimulacionDocumento2 páginasGraficas y SimulacionAdriana Elorza RamosAún no hay calificaciones

- Tarea EmbragueDocumento1 páginaTarea EmbragueAdriana Elorza RamosAún no hay calificaciones

- Amplificadores Operacionales Practica 2Documento10 páginasAmplificadores Operacionales Practica 2Adriana Elorza RamosAún no hay calificaciones

- Ramos Adriana 2022-B RO2Documento5 páginasRamos Adriana 2022-B RO2Adriana Elorza RamosAún no hay calificaciones

- EngranesDocumento96 páginasEngranesAdriana Elorza RamosAún no hay calificaciones

- 514-C - Elorza Ramos Adriana - 2022-A - RO3Documento4 páginas514-C - Elorza Ramos Adriana - 2022-A - RO3Adriana Elorza RamosAún no hay calificaciones

- Motores Con Ruedas ArdDocumento5 páginasMotores Con Ruedas ArdAdriana Elorza RamosAún no hay calificaciones

- Introduccion de UP y UCDocumento21 páginasIntroduccion de UP y UCAngel Avalos VillaseñorAún no hay calificaciones

- Microcontroladores LAB1Documento12 páginasMicrocontroladores LAB1Gian IbiasAún no hay calificaciones

- Resumen CAPITULO 5 MEMORIA INTERNA Organizacion y ArquitecturaDocumento12 páginasResumen CAPITULO 5 MEMORIA INTERNA Organizacion y ArquitecturaSebastian Quiroga SilvaAún no hay calificaciones

- LabSDLunV2-30,31,37-E8-P2-Operadores Lógicos Con Circuitos TTLDocumento13 páginasLabSDLunV2-30,31,37-E8-P2-Operadores Lógicos Con Circuitos TTLAngel CastilloAún no hay calificaciones

- Práctica 7 - Paula González IzquierdoDocumento1 páginaPráctica 7 - Paula González IzquierdoPaulaAún no hay calificaciones

- FPGADocumento39 páginasFPGApatrohellAún no hay calificaciones

- Cuadro Sinoptico TTL-CMOSDocumento8 páginasCuadro Sinoptico TTL-CMOSCésar FreemanAún no hay calificaciones

- Practica 1 Electronica Digital (Tablas de Verdad)Documento5 páginasPractica 1 Electronica Digital (Tablas de Verdad)Lalo GarzaAún no hay calificaciones

- 3-Introduccion A La Herramienta Quartus IIDocumento10 páginas3-Introduccion A La Herramienta Quartus IIDanielAún no hay calificaciones

- Historia de Los MicrostransistoresDocumento46 páginasHistoria de Los MicrostransistoresMarco A G CeriAún no hay calificaciones

- Proyecto CDA Semaforo InfoDocumento7 páginasProyecto CDA Semaforo InfoFernando QuinteAún no hay calificaciones

- Chip InmosDocumento8 páginasChip InmosDario GomezAún no hay calificaciones

- Tema IDocumento14 páginasTema IBeatriz Márquez BalderasAún no hay calificaciones

- Caracteristicas - de - Los - PLD - S.PDF Filename UTF-8''Caracteristicas de Los PLD - S PDFDocumento31 páginasCaracteristicas - de - Los - PLD - S.PDF Filename UTF-8''Caracteristicas de Los PLD - S PDFcristoferAún no hay calificaciones

- MDP UMG Arquitectura II Harvard Von Neumann PDFDocumento12 páginasMDP UMG Arquitectura II Harvard Von Neumann PDFLuis MoralesAún no hay calificaciones

- Dispositivos Electrónicos-MosfetDocumento74 páginasDispositivos Electrónicos-MosfetJHONY JAVIER ROQUE AVALOSAún no hay calificaciones

- Contadores SincronasDocumento10 páginasContadores SincronasAna Gabriela Laura NataAún no hay calificaciones

- LABORATORIO N3 CircuitosDocumento9 páginasLABORATORIO N3 CircuitosSteve BryamAún no hay calificaciones

- N 555Documento3 páginasN 555Henry UgshaAún no hay calificaciones

- PMSD 425 TrabajofinalDocumento7 páginasPMSD 425 TrabajofinalquispesaldiasdannyAún no hay calificaciones

- Codificadores y DecodificadoresDocumento10 páginasCodificadores y DecodificadoresJuanito GimenezAún no hay calificaciones

- CISCDocumento2 páginasCISCFranky BejaranoAún no hay calificaciones

- Informe 03Documento14 páginasInforme 03diegoAún no hay calificaciones

- Arquitectura Del Computador Version FinalDocumento15 páginasArquitectura Del Computador Version FinalGregory VerasAún no hay calificaciones

- Resumen Arq de Computadoras UpDocumento25 páginasResumen Arq de Computadoras UpdsadasAún no hay calificaciones

- Dispositivos Lógicos ProgramablesDocumento15 páginasDispositivos Lógicos ProgramablesPaloma RodriguezAún no hay calificaciones

- SDDocumento12 páginasSDCarlos EstradaAún no hay calificaciones

- Puertos y Buses de ComunicacionDocumento6 páginasPuertos y Buses de ComunicacionRegino SantiagoAún no hay calificaciones

- Sesion 13-14Documento10 páginasSesion 13-14Byron PesantezAún no hay calificaciones

- Identificación de La GuíaDocumento12 páginasIdentificación de La Guíajohn garciaAún no hay calificaciones