Documentos de Académico

Documentos de Profesional

Documentos de Cultura

CFT 11325 201810 1

Cargado por

Ruben Naldo Darza MoranTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

CFT 11325 201810 1

Cargado por

Ruben Naldo Darza MoranCopyright:

Formatos disponibles

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Código-Materia: 11325 - INTERFACES Y ARQUITECTURA HARDWARE Y

LABORATORIO

Requisito: PRE: 11121 Lógica Digital y Laboratorio

COR: 11326 Espacio de Laboratorio de Interfaces y Arquitectura

Hardware.

Programa – Semestre: Ingenierías: Telemática – Sexto semestre

Período académico: Enero a Mayo de 2018

Intensidad semanal: 4 horas semanales + 2 horas de laboratorio.

Créditos: 4

Motivación

El curso de Interfaces y Arquitectura Hardware ayudará al estudiante a comprender el

funcionamiento de los elementos constitutivos de los sistemas de cómputo y le permitirá

reconocer las capacidades y limitaciones que tienen los sistemas informáticos en la ejecución de

las operaciones para las cuales se va a utilizar y según una determinada configuración. Incluye un

estudio de la relación hardware-software y se cubren aspectos generales de la arquitectura de

computadores tales como: desempeño, conjunto de instrucciones, modelos de programación de

procesadores, CPUs tipo RISC y CISC, jerarquías de memorias, dispositivos periféricos y de

almacenamiento y demás elementos hardware que dan soporta a los sistemas operativos así como

el uso y aplicación de plataformas hardware basadas en algunos procesadores comerciales, con el

fin de dar solución a ciertos problemas tecnológicos en el campo de la ingeniería.

Programa: Ingeniería Telemática

Resultados de Aprendizaje

relacionados con el • B: Diseño experimentos (A)

Programa

B: Diseño experimentos (A)

Resultados

Fuente de Valoración Si

de Aprendizaje

Objetivos

General

EVALUAR la relación e interacción entre los componentes de hardware y de software de

un sistema de cómputo, en relación con el procesamiento, almacenamiento y el

transporte de la información, con el fin emitir un juicio respecto de su comportamiento y

desempeño.

Terminales:

Interfaces y arquitectura de Hardware y Laboratorio Página 1 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Al finalizar el curso el estudiante estará en capacidad de:

1. EXPLICAR la estructura y la arquitectura de un dispositivo de cómputo utilizando la

perspectiva de los niveles de abstracción y de los componentes funcionales comunes a

cualquier sistema de cómputo.

2. ANALIZAR las capacidades y limitaciones que imponen la relación de compromiso entre el

formato de representación de la información y la arquitectura del sistema. Tanto en el

procesamiento y almacenamiento desde la perspectiva del programador.

3. ESTABLECER las relaciones entre las estructuras de programación de lenguaje de alto nivel

y el conjunto de instrucciones de la arquitectura hardware subyacente, para determinar su

efecto sobre el comportamiento en diferentes configuraciones del dispositivo de cómputo.

4. APLICAR la metodología de diseño y conducción de experimento para emitir un juicio o

conclusión sobre aspectos del comportamiento o desempeño de un sistema de cómputo

5. IMPLEMENTAR servicios informáticos básicos utilizando sistemas embebidos incluyendo

aspectos de interfaces de comunicación y computación física.

Específicos

De formación académica:

UNIDAD 1: Introducción A La Estructura y Arquitectura De Los Sistemas de Cómputo

Objetivos específicos:

Identificar los niveles de descripción de un computador convencional y su estructura

básica.

Ser capaz de identificar la frontera software-hardware, explorando los niveles del

hardware conectados a este punto de contacto.

Dar razón de la evolución de la computación desde el punto de vista de Arquitectura

Von Neumann.

Contenido:

Introducción general a la estructura de computadores. Niveles de abstracción de

un computador y repaso del nivel de lógica Digital.

Generalidades sobre el curso e introducción los conceptos de máquinas Von

Neumann. (8 horas)

Actividades de laboratorio:

Discusión general de la estructura de un PC convencional. (Semana 1)

Interfaces y arquitectura de Hardware y Laboratorio Página 2 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

UNIDAD 2: Aritmética del Computador.

Objetivos específicos:

Examinar las ventajas de la aritmética “en complemento a 2” con respecto a otros

sistemas de numeración.

Manejar formatos de numeración en punto flotante mediante ejemplos concretos.

Describir cómo opera una unidad aritmética y una Unidad de punto flotante.

Identificar las limitaciones de los sistemas de numeración y reconocer los inconvenientes

que puede ocasionar los cambios de tipo formato en los datos y análisis de errores por

redondeo, truncamiento y desbordamiento.

Contenido:

Aritmética del computador: operaciones aritméticas con números positivos y negativos

con énfasis en aritmética “Complemento a 2” y el empleo de notación hexadecimal;

revisión de otros sistemas de numeración.

Generalidades sobre cantidades y operaciones en punto flotantes: números, formatos y

descripción de algunas aplicaciones y restricciones de las unidades de punto flotante en el

manejo de la información.

Análisis de errores de la aritmética del computador.

Las banderas como bits de información adicional a las operaciones realizadas por la ALU.

Información no numérica. Códigos ASCII y Unicode

Actividades de laboratorio:

Interconexión y Simulación de una ALU típica de 8 bits usando Quartus II. (Semana

3-4)

UNIDAD 3: Estructura De Una Unidad Central de Procesamiento (CPU)

Objetivos específicos:

Detallar la organización interna básica de una CPU típica.

Explicar el concepto de programa almacenado, la representación de las instrucciones en

memoria de una computadora y los pasos para su ejecución en un esquema basado en

buses.

Identificar la relación entre lenguaje máquina y lenguaje ensamblador.

Contenido:

Estructura interna aplicable a toda CPU: Unidad aritmética – lógica, registros internos,

unidades de control alambradas y micro-programadas.

Interfaces y arquitectura de Hardware y Laboratorio Página 3 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Relación entre Instrucciones en lenguaje de máquina y ensamblador y lenguajes de alto

nivel.

Proceso detallado de las diferentes fases en el tratamiento de las instrucciones por un

procesador: 1) Búsqueda en memoria de las instrucciones (Fetch); 2) decodificación y 3)

ejecución.

Actividades de laboratorio:

Módulo 3: Diseño y simulación de un procesador RISC simple de 8 bits, utilización de la

ALU, registros, y bloques constructores vistos en la capa de lógica Digital (multiplexores,

de-multiplexores, decodificadores, codificadores, etc.). (Semana 5 - 6).

Interconexión de la CPU diseñada con un sistema de memoria básico. Analizar las fases de

tratamiento de una instrucción y concepto de lenguaje máquina. (Semana 7-8)

UNIDAD 4: Modelo de Programación de procesadores- La Interfaz Hardware / Software

Objetivos específicos:

Explicar los pasos requeridos para cargar y ejecutar un programa que es escrito en

lenguaje de alto nivel en un sistema de cómputo.

Estar en capacidad de traducir un programa corto de alto nivel (sentencias

secuenciales básicas) a lenguaje ensamblador y dar razón de lo que sucede en cada

una de las capas de abstracción del sistema de cómputo.

Establecer las diferencias generales en el lenguaje ensamblador que se genera al

compilar aplicaciones sobre plataformas de 32 y 64 bits.

Contenido:

Estudio del conjunto de instrucciones de procesadores de uso comercial de equipos de

escritorio y dispositivos móviles.

Tipos de ISA: Procesadores RISC semejanzas y diferencias con los CISC.

Estructura básica interna, características básicas del hardware y conjunto de

instrucciones en los procesadores Intel y procesadores ARM.

Modos de direccionamiento, manejo de la pila; subrutinas; ejemplos.

Actividades de laboratorio:

Módulo 3: Programación Básica en Lenguaje Ensamblador. Ejemplos y ejercicios sobre un

Software de emulación de procesadores INTEL y ARM (semana 9-10)

Módulo 5: Prácticas Avanzadas –Análisis de Subrutinas e Interrupciones (Semana 12-13)

UNIDAD 5: Sistema de Memoria y Sistema de Entrada/Salida

Objetivos específicos:

Interfaces y arquitectura de Hardware y Laboratorio Página 4 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Dar razón de las jerarquías de memoria y poder diferenciar capacidades, rapidez y

costos.

Explicar el proceso completo que se lleva a cabo en el manejo de las interrupciones

por parte del procesador y demás componentes hardware.

Analizar y explicar la relación de compromiso entre el sistema de memoria y el

desempeño en la ejecución de procesos en sistemas de cómputo

Contenido:

Razón y necesidad de la organización jerárquica de la memoria.

Principio de localidad espacial y temporal

Memoria caché, concepto y descripción, análisis de prestaciones, métodos de

implementación típica, cálculo del AMAT, miss rate y Hit rate. Ejemplos.

Codificación de programas amigables con la cache.

Mecanismos generales de la comunicación con los periféricos y de su control por la

CPU: Interrupciones de varias clases y procesos de atención a las mismas.

Actividades de laboratorio:

Servicios básicos sobre el PC embebido Raspberry Pi.

Sobre el simulador del Sistema microprocesador didáctico MSX88, se comprueba la

técnica de interrupciones y subrutinas de atención de servicio.

Implementación de un sistema básico cliente servidor usando paso de mensajes e

integración con sensores y actuadores, servicios Web y datalogger.

UNIDAD 6: Diseño Y Conducción de Experimentos Sobre Sistemas De Cómputo

Objetivo:

Identificar las etapas en el diseño de experimentos: objetivo, número de factores

primarios y secundarios. Fuentes de ruido.

Aplicar el diseño y conducción de un experimento partiendo de una hipótesis

relacionada con el desempeño y comportamiento de un sistema de cómputo.

Interpretar y analizar los datos obtenidos en un experimento para diferentes

configuraciones de computadores y relacionar dichos resultados con los componentes

hardware y software específicos.

Dar recomendaciones de características del sistema de cómputo para obtener una

mejor eficiencia y desempeño en la ejecución de programas de aplicación.

Contenido:

Planteamiento y declaración de hipótesis y objetivo de un experimento

Importancia del diseño de los experimentos y Definición de variables, factores

primarios y secundarios, restricciones de un experimento.

Tipos y etapas de experimentos adecuadas sobre sistemas de cómputo.

Análisis e interpretación de datos arrojados de un experimento aplicando técnicas y

herramientas de estadística.

Interfaces y arquitectura de Hardware y Laboratorio Página 5 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Actividades de laboratorio:

Estimación de parámetros usando datos experimentales (aplicación de inferencia

estadística)

Diseño y conducción de varios experimento para responder cuestiones sobre el

rendimiento de la memoria RAM y CPU Vs un programa de aplicación.

De formación en valores y capacidades

La tolerancia, y no en el sentido de desinterés por lo que piensa el otro sino más bien

promover el respeto activo, el interés por comprender a los otros y por ayudar a cumplir

los objetivos de aprendizaje.

La autonomía e interés de querer ir más allá de los que se enseña. La perseverancia a

través del desarrollo de los ejercicios y de talleres y que la motivación simplemente no se

una nota si no su autoformación y amor por aprender cosas nuevas.

La capacidad de análisis, a través de la identificación y evaluación de los componentes

necesarios para resolver un problema planteado.

La capacidad cooperación y comunicación, ya que se deben presentar las soluciones a los

problemas propuestos de una manera clara para los demás participantes del curso.

La capacidad de trabajo bajo presión, ya que se cuenta con tiempos limitados para algunas

actividades.

Trabajo en equipo, se refiere a equipos más o menos numerosos de personas que trabajan

en un mismo proyecto y que son multidisciplinares, ya que el proyecto final se realizará en

conjunto con los estudiantes de ingeniería telemática.

Metodología

Presentación, lecturas y discusión de los temas teóricos; quices, preguntas, trabajo individual y

en grupos; mediante guía del profesor el estudiante inferirá la manera como operan los

principales componentes hardware de una máquina de cómputo; proyectos de fin de curso.

Los alumnos estudiarán materiales basados en el texto guía, libros de referencia, notas del

curso, e información extraída del Internet, de revistas, etc., para discusión en clase.

Experimentos de laboratorio: Simulación de algunos componentes funcionales de un

computador Preparación y ejecución de programas en lenguaje en ensamblador para la

arquitectura IA32/64; simulación de la operación de un microprocesador didáctico;

Compilación y ejecución de programas sobre una arquitectura real y su uso por un sistema

operativo real.

Ayudas docentes tales como videos, proyecciones y uso de programas licenciados y

“freeware”.

Interfaces y arquitectura de Hardware y Laboratorio Página 6 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

Actividades del estudiante

Antes de la clase:

• Estudiar el material asignado para cada sesión, para ello debe consultar en moodle

los temas de estudio de la unidad.

• Responder las preguntas de preparación de cada tema.

• Resolver los ejercicios propuestos para aplicar los conceptos estudiados.

• Escribir las inquietudes y observaciones surgidas en el proceso de preparación del

tema.

Durante la clase:

• Los estudiantes deben participar activamente (compartir experiencias, transmitir

las dudas para ser aclaradas) en las actividades asignadas para cada tema

partiendo del conocimiento previo adquirido a través de la lectura y de la

elaboración de los informes.

• Realizar los ejercicios complementarios que el profesor indique.

Después de la clase:

• Terminar los ejercicios presentados en cada clase.

• Resolver los ejercicios propuestos por el profesor.

• Aplicar los conocimientos y técnicas aprendidas en la realización de los ejercicios

de cada tema.

Evaluación

Exámenes Porcentaje Semana de realización

Primer examen parcial 22% Semana 7

Segundo examen parcial 22% Semana 11

Tercer examen y Final 22% Semana 17

Verificaciones de estudio 10%

Trabajo de Laboratorio 12%

Proyecto Final 12%

Total 100%

a) Primer Examen Parcial (1P) 22% (7a.semana)

Objetivos de aprendizaje:

Interfaces y arquitectura de Hardware y Laboratorio Página 7 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

OE Identificar los niveles de descripción de un computador convencional y su estructura

1.1 básica.

OE Ser capaz de identificar la frontera software-hardware, explorando los niveles del

1.2 hardware conectados a este punto de contacto.

OE Dar razón de la evolución de la computación desde el punto de vista de Arquitectura

1.3 Von Neumann.

OE Examinar las ventajas de la aritmética “en complemento a 2” con respecto a otros

2.1 sistemas de numeración.

OE Manejar formatos de numeración en punto flotante mediante ejemplos concretos.

2.2

OE Describir cómo opera una unidad aritmética y una Unidad de punto flotante.

2.3

OE Identificar las limitaciones de los sistemas de numeración y reconocer los

2.4 inconvenientes que puede ocasionar los cambios de tipo formato en los datos y

análisis de errores por redondeo, truncamiento y desbordamiento.

OE Detallar la organización interna básica de una CPU típica

3.1

OE Explicar el concepto de programa almacenado, la representación de las instrucciones

3.2 en memoria de una computadora y los pasos para su ejecución en un esquema

basado en buses.

OE Identificar la relación entre lenguaje máquina y lenguaje ensamblador

3.3

b) Segundo Examen parcial (2P) 22% (11a.semana)

Objetivo de aprendizaje:

OE Explicar el concepto de programa almacenado, la representación de las instrucciones en

3.2 memoria de una computadora y los pasos para su ejecución en un esquema basado en

buses.

OE Identificar la relación entre lenguaje máquina y lenguaje ensamblador

3.3

OE Explicar los pasos requeridos para cargar y ejecutar un programa que es escrito en

4.1 lenguaje de alto nivel en un sistema de cómputo.

OE Estar en capacidad de traducir un programa corto de alto nivel (sentencias secuenciales

4.2 básicas) a lenguaje ensamblador y dar razón de lo que sucede en cada una de las capas de

abstracción del sistema de cómputo.

OE Establecer las diferencias generales en el lenguaje ensamblador que se genera al compilar

4.3 aplicaciones sobre plataformas de 32 y 64 bits.

OE Calcular y explicar las mejoras y ventajas de técnicas a nivel de micro-arquitectura para

4.4 mejorar el desempeño de procesadores.

Interfaces y arquitectura de Hardware y Laboratorio Página 8 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

c) Tercer Examen Parcial y final (3P) 22% (17a. semana)

Objetivos de aprendizaje:

OE Establecer las diferencias generales en el lenguaje ensamblador que se genera al compilar

4.3 aplicaciones sobre plataformas de 32 y 64 bits.

OE Calcular y explicar las mejoras y ventajas de técnicas a nivel de micro-arquitectura para

4.4 mejorar el desempeño de procesadores.

OE Dar razón de las jerarquías de memoria y poder diferenciar capacidades, rapidez y costos.

5.1

OE Analizar y explicar la relación de compromiso entre el sistema de memoria y el

5.2 desempeño en la ejecución de procesos en sistemas de cómputo

OE Explicar el proceso completo que se lleva a cabo en el manejo de las interrupciones por

5.3 parte del procesador y demás componentes hardware.

OE Identificar las etapas en el diseño de experimentos: objetivo, número de factores

6.1 primarios y secundarios. Fuentes de ruido.

e) Verificaciones de estudio

Las verificaciones de estudio se hacen sin previo aviso y no tienen supletorio.

f) Trabajo de laboratorio: (LAB)

La asistencia a las sesiones de laboratorio son obligatorias, la no asistencia corresponde a una nota

de cero (0.0)

g) Trabajo final escrito y sustentado (PF)

Nota: La distribución de los objetivos asociados a las evaluaciones pueden variar de acuerdo a

cambios en las fechas de los exámenes o tiempo de apropiación y estrategias de aprendizaje. De

todas formas el profesor informará los objetivos que se evaluarán.

Bibliografía

Libros Guía.

Principal:

1. Computer Systems: A Programmer's Perspective, Randal E. Bryant, David R. O'Hallaron.

Addison Wesley Pub Co Inc; Edición: 0002 (1 de febrero de 2010).

Secundarios:

Interfaces y arquitectura de Hardware y Laboratorio Página 9 de 10

FACULTAD DE INGENIERÍA

DEPARTAMENTO CIENCIAS FÍSICAS Y TECNOLOGÍA

2. Digital Desing and Computer Architecture, David Money Harris & Sarah L. Harris. Morgan

Kaufmann; 1 edition (March 16, 2007)

3. Inside the Machine: An Illustrated Introduction to Microprocessors and Computer

Architecture. Jon M. Stokes, 1 edition (November 30, 2006)

Referencias generales

Microprocesadores de INTEL 8086/8088, 80186/80188, 80286, 80386, 80486, Pentium,

Prentium ProProcessor, Pentium II, III, 4. BREY, Barry B. Prentice Hall; 7 edición, 2005.

Digital Design and Computer Architecture, David Harris, Sarah Harris. Morgan Kaufmann; 1

edición, 2007.

Estructura de Computadores y Periféricos, R.J. Martínez, José A. Boluda, Juan J. Pérez,

Alfaomega Ra-Ma, 2001

Arquitectura y Organización de Computadoras, Stallings W. , Prentice Hall

Anexo 1:

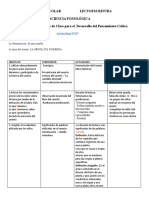

OT1: EXPLICAR la estructura OT2: ANALIZAR las OT3: ESTABLECER las OT4: APLICAR la OT5: IMPLEMENTAR

y la arquitectura de un capacidades y limitaciones relaciones entre las metodología de servicios informáticos

dispositivo de cómputo que imponen la relación de estructuras de programación diseño y conducción básicos utilizando

utilizando la perspectiva de compromiso entre el de lenguaje de alto nivel y el de experimento para sistemas embebidos

OT los niveles de abstracción y formato de representación conjunto de instrucciones de emitir un juicio o incluyendo aspectos de

Objetivos de los componentes de la información y la la arquitectura hardware conclusión sobre interfaces de

Terminales funcionales comunes a arquitectura del sistema. subyacente, para determinar aspectos del comunicación y

cualquier sistema de Tanto en el procesamiento y su efecto sobre el comportamiento o computación física.

OE Objetivo cómputo. almacenamiento desde la comportamiento en desempeño de un

Específico perspectiva del diferentes configuraciones sistema de cómputo

OE 1.1 x programador. del dispositivo de cómputo.

UNIDAD 1: Introducción A La

Estructura y Arquitectura De Los OE 1.2 x

Sistemas de Cómputo OE 1.3 x

OE 2.1 x

UNIDAD 2: Aritmética del OE 2.2 x

Computador OE 2.3 x

OE 2.4 x x

UNIDAD 3:Estructura De Una OE 3.1 x

Unidad Central de Procesamiento OE 3.2 x

(CPU) OE 3.3 x x

UNIDAD 4: Modelo de OE 4.1 x

Programación de procesadores OE 4.2 x

La Interfaz Hardware / Software. OE 4.3 x

UNIDAD 5: Sistema de Memoria y

OE 5.1 x

Sistema de Entrada/Salida

OE 5.2 x

OE 5.3 x

O E 6.1 x x

UNIDAD 6: Diseño Y Conducción

de Experimentos Sobre Sistemas

O E 6.2 x

De Cómputo O E 6.3 x x x

O E 6.4 x

Espacio de laboratorio x x x x x

Ilustración 1Mapeo OT Vs OE por Unidad

Interfaces y arquitectura de Hardware y Laboratorio Página 10 de 10

También podría gustarte

- Acciones solidarias UNAD para comunidadesDocumento3 páginasAcciones solidarias UNAD para comunidadesRuben Naldo Darza MoranAún no hay calificaciones

- Comisión Nacional Del ServicioDocumento1 páginaComisión Nacional Del ServicioRuben Naldo Darza MoranAún no hay calificaciones

- Certificación Laboral y Dos Últimos Desprendibles de PagoDocumento1 páginaCertificación Laboral y Dos Últimos Desprendibles de PagoRuben Naldo Darza MoranAún no hay calificaciones

- Pagos PSE de Nequi Pago RealizadoDocumento2 páginasPagos PSE de Nequi Pago RealizadoRuben Naldo Darza MoranAún no hay calificaciones

- Actividad P2P - Curso Desarrollo Del Pensamiento CríticoDocumento3 páginasActividad P2P - Curso Desarrollo Del Pensamiento CríticoRuben Naldo Darza MoranAún no hay calificaciones

- Circular InformativaDocumento2 páginasCircular Informativahugo mejiaAún no hay calificaciones

- Listado de Desempenos 20220414 110036Documento1 páginaListado de Desempenos 20220414 110036Ruben Naldo Darza MoranAún no hay calificaciones

- 1 Guía de Aprendizaje Metodo Cientifico ArlethDocumento17 páginas1 Guía de Aprendizaje Metodo Cientifico ArlethRuben Naldo Darza MoranAún no hay calificaciones

- 2022-Silueta Textual de Guía de Aprendizaje MIXDocumento16 páginas2022-Silueta Textual de Guía de Aprendizaje MIXRuben Naldo Darza MoranAún no hay calificaciones

- Convenio académico UMECIT-CoreducamosDocumento14 páginasConvenio académico UMECIT-CoreducamosRuben Naldo Darza MoranAún no hay calificaciones

- 6 Version Electronica de Una RevistaDocumento160 páginas6 Version Electronica de Una Revistasistemas descargasAún no hay calificaciones

- 6 Version Electronica de Una RevistaDocumento160 páginas6 Version Electronica de Una Revistasistemas descargasAún no hay calificaciones

- Galvan 2020Documento1 páginaGalvan 2020Ruben Naldo Darza MoranAún no hay calificaciones

- UD BD RelacionalesDocumento24 páginasUD BD RelacionalesJosé Luis Benito AndújarAún no hay calificaciones

- RÚBRICA para Evaluar La Presentación de Trabajos EscritosDocumento1 páginaRÚBRICA para Evaluar La Presentación de Trabajos EscritosRuben Naldo Darza MoranAún no hay calificaciones

- Cronograma Planeacion Area de Tecnologia e Informatica - 2019, ConsolidadoDocumento21 páginasCronograma Planeacion Area de Tecnologia e Informatica - 2019, ConsolidadoRuben Naldo Darza MoranAún no hay calificaciones

- RIBIEAlgoritmosDocumento47 páginasRIBIEAlgoritmosRuben Naldo Darza MoranAún no hay calificaciones

- Plasticos en Los Oceanos LRDocumento4 páginasPlasticos en Los Oceanos LRRuben Naldo Darza MoranAún no hay calificaciones

- VdsvdfsDocumento12 páginasVdsvdfsRuben Naldo Darza MoranAún no hay calificaciones

- FGFDGFDGDocumento29 páginasFGFDGFDGRuben Naldo Darza MoranAún no hay calificaciones

- Reseña Pregúntele Al EnsayistaDocumento7 páginasReseña Pregúntele Al EnsayistaLaura Yolanda Calderón Benítez100% (1)

- FGFDGFDGDocumento29 páginasFGFDGFDGRuben Naldo Darza MoranAún no hay calificaciones

- Conviasa ReservaDocumento6 páginasConviasa ReservaJuan Carlos AgudeloAún no hay calificaciones

- DBA MatemáticasDocumento88 páginasDBA Matemáticasoriol_telAún no hay calificaciones

- Plastico en Oceanos GreenpeaceDocumento5 páginasPlastico en Oceanos GreenpeaceSofi ChacónAún no hay calificaciones

- CEPAL Indicadores SocialesDocumento111 páginasCEPAL Indicadores Socialesapi-3837253100% (6)

- BiocomercioDocumento4 páginasBiocomercioRuben Naldo Darza MoranAún no hay calificaciones

- Normas Apa 2015Documento21 páginasNormas Apa 2015Anastacio Sandalia Saliva81% (31)

- 2ConceptosBasicos v1Documento37 páginas2ConceptosBasicos v1Reyes Espino PeñalozaAún no hay calificaciones

- Rectificadores de onda completa y filtros: cálculos de rizo y regulaciónDocumento2 páginasRectificadores de onda completa y filtros: cálculos de rizo y regulaciónalfonso garciaAún no hay calificaciones

- 5 - Color - Rellenos y TransparenciasDocumento21 páginas5 - Color - Rellenos y TransparenciasGiovanni CardozoAún no hay calificaciones

- Exposicion de CENTRALES DE GENERACIÓN EÓLICADocumento30 páginasExposicion de CENTRALES DE GENERACIÓN EÓLICAINGJDIAZAún no hay calificaciones

- Examen 17 - ControlDocumento27 páginasExamen 17 - ControlRosember RamirezAún no hay calificaciones

- Ejercicios AplicadosDocumento3 páginasEjercicios AplicadosAnonymous SegCAngVY5Aún no hay calificaciones

- Capacitacion Modelo Webcam 1Documento5 páginasCapacitacion Modelo Webcam 1Meli Gomez0% (2)

- Cuaderno de Informe Numero 12Documento14 páginasCuaderno de Informe Numero 12aldahirtaboadAún no hay calificaciones

- Introducción A Las Normas de La Gestión de La CalidadDocumento39 páginasIntroducción A Las Normas de La Gestión de La Calidadvaletele75% (8)

- EJERCICIOS ANÁLISIS DE CARGAS Y REACCIONESDocumento6 páginasEJERCICIOS ANÁLISIS DE CARGAS Y REACCIONESPablo HollamnnAún no hay calificaciones

- Recuperación local escolarDocumento9 páginasRecuperación local escolarEdu ReyesAún no hay calificaciones

- Sociologia Del Trabajao - El Capitalismo en La Era Del BigDataDocumento1 páginaSociologia Del Trabajao - El Capitalismo en La Era Del BigDataFrederick Díaz MejíaAún no hay calificaciones

- Diagnóstico situacional y recolección de informaciónDocumento2 páginasDiagnóstico situacional y recolección de informaciónJesus RodríguezAún no hay calificaciones

- 6 - Tipos de AuditoríasDocumento1 página6 - Tipos de AuditoríasShary NuñezAún no hay calificaciones

- Exposicion AddiDocumento8 páginasExposicion AddiEdwin Ferney Ruiz CameloAún no hay calificaciones

- Tarea 6 - Introducción A La AgrimensuraDocumento6 páginasTarea 6 - Introducción A La AgrimensuraMariel del Carmen Gonzalez Rosario50% (2)

- Tarea 1. Cuestionario P59Documento2 páginasTarea 1. Cuestionario P59Nikolay Fuel NcfcAún no hay calificaciones

- Sesion4-2 Fuentes Inv MercadosDocumento21 páginasSesion4-2 Fuentes Inv MercadosVictor ManriqueAún no hay calificaciones

- Oxford CATALOGODocumento28 páginasOxford CATALOGOteam37Aún no hay calificaciones

- Conceptos Que Se Deben Tener en Cuenta Sobre Este Paradigma: Por: Italo Alexander Morales ZamoraDocumento16 páginasConceptos Que Se Deben Tener en Cuenta Sobre Este Paradigma: Por: Italo Alexander Morales Zamoraalex201476Aún no hay calificaciones

- Botones PrincipalesDocumento3 páginasBotones PrincipalesNgonzalo GZAún no hay calificaciones

- Instrucciones Basicas de QbasicDocumento9 páginasInstrucciones Basicas de QbasicJesús Yair Ramirez VillalobosAún no hay calificaciones

- Calentador Estanco Bajo Nox Gas Natural Next Evo X SFT Blu L Ariston 10899742 TechsheetsupDocumento2 páginasCalentador Estanco Bajo Nox Gas Natural Next Evo X SFT Blu L Ariston 10899742 TechsheetsupConchitaAún no hay calificaciones

- Articulos Cientificos Sala 6Documento4 páginasArticulos Cientificos Sala 6denisita cervantes100% (1)

- Medidores de Gas Tipo Diafragma G1Documento4 páginasMedidores de Gas Tipo Diafragma G1Helton De AlbaAún no hay calificaciones

- Variador de VelocidadDocumento26 páginasVariador de VelocidadHumberto Paccosoncco HuancaAún no hay calificaciones

- Cultura Organizacional de SpotifyDocumento6 páginasCultura Organizacional de SpotifySanti C.D100% (1)

- Pruebas de hipótesis y distribuciones estadísticasDocumento3 páginasPruebas de hipótesis y distribuciones estadísticaskatherin MartinezAún no hay calificaciones

- FOR. Orden de CompraDocumento1 páginaFOR. Orden de CompraDOCUMENTAL FINCIMECAún no hay calificaciones

- Descarga e impresión de historiales y alarmas panel Notifier 320/640Documento10 páginasDescarga e impresión de historiales y alarmas panel Notifier 320/640Alfredo Zambra Alarcón Alias Morro100% (3)

- Constancia de Registro de Compras Y VentasDocumento1 páginaConstancia de Registro de Compras Y VentasLuis Fernandez FuertesAún no hay calificaciones