Documentos de Académico

Documentos de Profesional

Documentos de Cultura

1 - PLDs

Cargado por

Alberto Aguilera MartinezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

1 - PLDs

Cargado por

Alberto Aguilera MartinezCopyright:

Formatos disponibles

IPN ESIME CULHUACAN

Ingeniería en Computación

Circuitos Lógicos II

DCC Eusebio Ricárdez Vázquez

agosto – diciembre 2017

Dispositivos Lógicos Programables

(PLD´s).

¿Qué es un PLD?

Programable logical Device

Definición:

(Investigar una definición)

20/09/2017 Dr. Eusebio Ricárdez Vázquez 3

Características

Circuito integrado digital, donde la función boolena

puede ser determinada por el usuario.

Los PLD´s pueden reemplazar circuitos integrados de

propósito especifico en el diseño de circuitos digitales.

Un solo PLD es funcionalmente equivalente a dispositivos

que tienen desde 5 hasta 10,000 compuertas lógicas.

Básicamente en los PLD´s se pueden implementar

funciones booleanas usando Suma de Productos o

Productos de Suma usando una estructura AND-OR.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 4

Arquitectura Básica de los PLD´s

Los PLD´s contienen una arquitectura general

predefinida y se puede reprogramar por el

usuario.

Agunos PLD´s contiene flip-flops y Latches

para ser usados como elementos de

almacenamiento para entradas y salidas.

Los pines pueden ser usados como entradas,

salidas o I/O con habilitación de tres estados.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 5

Ventajas de los PLD´s

Reduce la cantidad de CI

Reduce el espacio en las tarjetas

electrónicas.

Menor consumo de potencia.

Tiempo de diseño corto.

Se pueden realizar cambios del

programa (mantenimiento).

Compacta.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 6

20/09/2017 Dr. Eusebio Ricárdez Vázquez 7

Estos dispositivos están basados en transistores bipolares ó

transistores especiales que cuando se hace circular una

fuerte corriente dejan de conducir, pero pueden volver a

conducir aplicando una diferencia de potencial en el

circuito.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 8

20/09/2017 Dr. Eusebio Ricárdez Vázquez 10

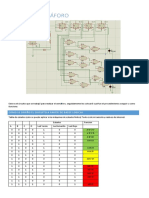

X X X X

X X X X X w

A

X X

X X X X x

B

X X X

X X X y

X X X

C

X X

X X X X z

X X X X X

D

20/09/2017 Dr. Eusebio Ricárdez Vázquez 11

La GAL (Generic Array Logic) es un PLD E²CMOS, la cual es

básicamente un PLA pero contiene a la salida FF´s D y compuertas XOR

(Macrocelda) para cambiar el estado lógico de la salida, además de

retroalimentar las salidas de los FF.

Macrocelda

20/09/2017 Dr. Eusebio Ricárdez Vázquez 12

GAL16V8

8 SALIDAS CON MACROCELDAS

PIN 1: SEÑAL DE RELOJ CLK

PIN 11: OUTPUT ENABLE PARA

HABILITAR LAS SALIDAS DEL

REGISTRO.

8 TERMINOS PRODUCTOS POR

SALIDA.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 13

Hay tres configuraciones posibles para la macrocelda OLMC (Output

Logic Macrocell) que son: simple, complejo y registrado.

Existen dos bits globales que son SYN y AC0 para el control del modo de

configuración. El bit XOR para control de la polaridad de la salida en

cualquiera de los tres modos, mientras que el bit AC1 para el control de

la configuración de la entrada salida de las macroceldas.

1. En modo simple todos los pines de salida son realimentados por los

pines adyacentes.

2. En el modo registrado, el pin 1 y el pin 11 son configurados como reloj

y habilitación de la salida.

3. En el modo complejo el pin 1 y 11 se usan como entradas y se usan

para retroalimentar los pines 19 y 12 respectivamente.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 14

MODO SIMPLE.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 15

MODO REGISTRADO.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 16

MODO COMPLEJO.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 17

PROCEDIMIENTO DE DISEÑO CON

DISPOSITIVOS LOGICOS

PROGRAMABLES.

1. Especificar la función que el circuito deseado debe realizar.

2. Generación de las ecuaciones booleanas requeridas para implementar

esa función.

3. Simplificación de las ecuaciones booleanas.

4. Generación de un mapa de fusibles desde las ecuaciones booleanas.

5. Simulación Lógica (Opcional).

6. Programación de dispositivo seleccionado.

7. Chequeo o test del dispositivo ya programado con el programador.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 18

Software para compilar los programas de los PLD:

ABEL

CUPL

LOGIC/ic

ORCAD-PLD

PLDesigner

TANGO-PLD

20/09/2017 Dr. Eusebio Ricárdez Vázquez 19

20/09/2017 Dr. Eusebio Ricárdez Vázquez 20

GAL22V10

10 SALIDAS CON MACROCELDA.

CIRCUITO DE 24 PINES.

PIN1: SEÑAL DE RELOJ.

PIN 13: OUTPUT ENABLE

PIN 14 Y 23 : 8 TERMINOS PRODUCTOS

PIN 15 Y 22: 10 TERMINOS PRODUCTOS.

PIN 16 Y 21: 12 TERMINOS PRODUCTOS.

PIN 17 Y 20: 14 TERMINOS PRODUCTOS.

PN 18 Y 19: 16 TERMINOS PRODUCTOS.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 21

SOFTWARE DE PROGRAMACION CUPL

IMPLEMENTACION DE CIRCUITOS

COMBINACIONALES.

USO DE ECUACIONES BOOLENAS Ó TABLAS DE

VERDAD.

IMPLEMENTACION DE CIRCUITOS SECUENCIALES.

USO DE ECUACIONES DE SECUENCIAS DE ESTADO

Ó MAQUINAS DE ESTADO.

20/09/2017 Dr. Eusebio Ricárdez Vázquez 22

Operadores CUPL

20/09/2017 Dr. Eusebio Ricárdez Vázquez 23

Ejemplo CUPL

20/09/2017 Dr. Eusebio Ricárdez Vázquez 24

Directivas CUPL

20/09/2017 Dr. Eusebio Ricárdez Vázquez 25

Ejemplo:

Diseñar un circuito para el control de un

motor de pasos, con señal de dirección

del giro.

OE

B

RELOJ

CIRCUITO

SECUENCIAL C

DIR D

20/09/2017 Dr. Eusebio Ricárdez Vázquez 26

Designer Engineer ;

Company CDM FI UNAM ;

Assembly None ;

Location ;

Device g16v8a ;

/* *************** INPUT PINS *********************/

PIN 1 = clk;

PIN 2 = dir;

PIN 11 = !oe;

/* *************** OUTPUT PINS *********************/

PIN 19 = A ; /* */

PIN 18 = B ; /* */

PIN 17 = C ; /* */

PIN 16 = D ; /*

/** Ecuaciones Logicas */

B.d = dir $ A;

A.d = !dir&!B # dir&B;

C= !A;

D= !B;

20/09/2017 Dr. Eusebio Ricárdez Vázquez 27

También podría gustarte

- Potencial Del Capital HumanoDocumento1 páginaPotencial Del Capital HumanoAlberto Aguilera MartinezAún no hay calificaciones

- Apuntes Gestalt Terapiados-2 0 PDFDocumento39 páginasApuntes Gestalt Terapiados-2 0 PDFÁngel Alvarado CastroAún no hay calificaciones

- Perls Fritz Yo Hambre Y Agresion PDFDocumento227 páginasPerls Fritz Yo Hambre Y Agresion PDFAlejandro Ayon Luna91% (11)

- Plan Didactica 1 Sem Fundamentos OSORNIO 1CV1Documento8 páginasPlan Didactica 1 Sem Fundamentos OSORNIO 1CV1Alberto Aguilera MartinezAún no hay calificaciones

- 6.-Diseño SecuencialDocumento24 páginas6.-Diseño SecuencialAlberto Aguilera MartinezAún no hay calificaciones

- 2.-PLDs 2Documento21 páginas2.-PLDs 2Alberto Aguilera MartinezAún no hay calificaciones

- Pag 20 Aguilera Martinez Luis AlbertoDocumento3 páginasPag 20 Aguilera Martinez Luis AlbertoAlberto Aguilera MartinezAún no hay calificaciones

- Tarea 3 ADocumento3 páginasTarea 3 AAlberto Aguilera MartinezAún no hay calificaciones

- Tarea 3Documento2 páginasTarea 3Alberto Aguilera MartinezAún no hay calificaciones

- Tarea 3 ADocumento3 páginasTarea 3 AAlberto Aguilera MartinezAún no hay calificaciones

- Tarea 4Documento1 páginaTarea 4Alberto Aguilera MartinezAún no hay calificaciones

- Tarea 2 Edopte 2Documento2 páginasTarea 2 Edopte 2Alberto Aguilera MartinezAún no hay calificaciones

- Tar 3 Edec 2 OrysistDocumento2 páginasTar 3 Edec 2 OrysistAlberto Aguilera MartinezAún no hay calificaciones

- Sold e BesselDocumento1 páginaSold e BesselAlberto Aguilera MartinezAún no hay calificaciones

- Reposicion 1Documento2 páginasReposicion 1Alberto Aguilera MartinezAún no hay calificaciones

- Numeros Complejos 2Documento38 páginasNumeros Complejos 2Roberth Vargas TorresAún no hay calificaciones

- APUNTESDocumento225 páginasAPUNTESAlberto Aguilera MartinezAún no hay calificaciones

- El Negro DurazoDocumento2 páginasEl Negro DurazoAlberto Aguilera MartinezAún no hay calificaciones

- Sold e BesselDocumento1 páginaSold e BesselAlberto Aguilera MartinezAún no hay calificaciones

- Comple JosDocumento3 páginasComple Joskatekyo19Aún no hay calificaciones

- WPSPin GeneradorDocumento6 páginasWPSPin GeneradorramonAún no hay calificaciones

- Guia de Practica 07Documento3 páginasGuia de Practica 07Milita RamosAún no hay calificaciones

- Programacion Equipos CobanDocumento5 páginasProgramacion Equipos CobanDario ManosalvasAún no hay calificaciones

- KemisDocumento18 páginasKemisDaniel Romero AAún no hay calificaciones

- Driver BoosterDocumento7 páginasDriver Boosteraldair paredes vasquezAún no hay calificaciones

- Azure AKS KubernetesDocumento2897 páginasAzure AKS Kubernetesacademia.online.opo.2022Aún no hay calificaciones

- Practica Calificada 1 - Electrónica Analógica y DigitalDocumento3 páginasPractica Calificada 1 - Electrónica Analógica y DigitalJoel Figueroa SaezAún no hay calificaciones

- Informe Laboratorios PLCDocumento19 páginasInforme Laboratorios PLCCristian San Martín DíazAún no hay calificaciones

- Cableado EstructuradoDocumento9 páginasCableado Estructuradojanalina ramosAún no hay calificaciones

- Manual de Instrucciones de EOS Utility Ver.3.12 para Macintosh (Spanish Edition)Documento117 páginasManual de Instrucciones de EOS Utility Ver.3.12 para Macintosh (Spanish Edition)alexisfpcAún no hay calificaciones

- Seminario1 - 2019B 797-5 CloudDocumento2 páginasSeminario1 - 2019B 797-5 CloudSaul ObandoAún no hay calificaciones

- Videojuego Con Unity y C#Documento64 páginasVideojuego Con Unity y C#Gabriel HernandezAún no hay calificaciones

- APRENDE Mantenimiento - Predictivo Preventivo Al Interior Del PCDocumento4 páginasAPRENDE Mantenimiento - Predictivo Preventivo Al Interior Del PCAlejoAún no hay calificaciones

- PDF Guia Instalador Tecnico CompressDocumento80 páginasPDF Guia Instalador Tecnico Compressfergot2010Aún no hay calificaciones

- 100 Preguntas LinuxDocumento3 páginas100 Preguntas LinuxjanocorroAún no hay calificaciones

- Tarjeta de RedDocumento43 páginasTarjeta de RedandresAún no hay calificaciones

- Diagrama Como Funciona InternetDocumento1 páginaDiagrama Como Funciona Internetdaniel LeonAún no hay calificaciones

- Air FiberDocumento74 páginasAir Fiberluis rodriguezAún no hay calificaciones

- Problema 1 TCPDocumento1 páginaProblema 1 TCPlpiloAún no hay calificaciones

- Diagrama Circulina MotosDocumento7 páginasDiagrama Circulina MotosHenry David Barboza CubasAún no hay calificaciones

- Coca Cola CompanyDocumento9 páginasCoca Cola CompanyMaria Alejandra Orjuela OrtizAún no hay calificaciones

- Marco TeoricoDocumento10 páginasMarco TeoricoBREYDI HENRY BLANCAS DE LA ROSAAún no hay calificaciones

- Proyecto SemáforoDocumento4 páginasProyecto SemáforoDiego AlonzoAún no hay calificaciones

- Grupo 5 - Informe FinalDocumento19 páginasGrupo 5 - Informe FinalMarilyn AlvaAún no hay calificaciones

- Metodología de Desarrollo de Un Sistema Empotrado Por Gutiérrez Et AlDocumento3 páginasMetodología de Desarrollo de Un Sistema Empotrado Por Gutiérrez Et AlMary OrtizAún no hay calificaciones

- Modelos de Bases de Datos y Manejadores PDFDocumento10 páginasModelos de Bases de Datos y Manejadores PDFEfraín ClaudioAún no hay calificaciones

- Qué Es Un Manejador de Base de DatosDocumento2 páginasQué Es Un Manejador de Base de DatosIsbelimar GuedezAún no hay calificaciones

- Qué Es Una DMZ y Cómo Te Puede Ayudar A Proteger Tu Empresa - INCIBEDocumento12 páginasQué Es Una DMZ y Cómo Te Puede Ayudar A Proteger Tu Empresa - INCIBEprobagarajeaAún no hay calificaciones

- Evidencia 3Documento2 páginasEvidencia 3Javi GarciaAún no hay calificaciones

- Introducción A PatronesDocumento2 páginasIntroducción A PatronesGerardo GandaraAún no hay calificaciones