Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Memorias PDF

Memorias PDF

Cargado por

JMGTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Memorias PDF

Memorias PDF

Cargado por

JMGCopyright:

Formatos disponibles

Memorias RAM

(Mantenimiento de Instalaciones Informticas)

Guillermo Bada Mart

al073569@alumail.uji.es

MemoriasRAM

GuillermoB.

ndice

MemoriasRAM:

Introduccin

..

Tipos

Segnlaconservacindelosdatos

Segnsuscontactos

...

....

Variantessegncaractersticas ..

4

4,5

6

Funcionamiento

...

Sincronizacin(tiempos)

Estructuralgica,almacenamientode:

Datos ...

Ejecutables

..

713

14

14

.................

14,15

Clasesdeerror .................

15,17

Errores

Sistemasdecorreccin

Paridad...

17

ECC

17,18

............................

Canaldoble

...............

18,19

Pgina2de19

MemoriasRAM

GuillermoB.

Memoriasprimarias

Cuando hablamos de la placabase, comentamos que lamemoria internaes la que se

encuentra fsicamente dentro del sistema constituido por la placabase, o en tarjetas de

circuito impreso directamente conectadas a ella. Debido a ello distinguimos memorias

internas y externas (tambin primarias y secundarias). Dentro de este tipo de memorias

(primariasointernas)distinguiremoslassiguientes:

Losregistrosdelprocesador

Lascachsinternayexterna

LamemoriaBIOS

LamemoriaRAM

En ste trabajo nos vamos a centrar en las memorias RAM, la memoria RAM cundo nos

referimos, o hacemos referencia a las memorias 'RAM' de nuestro ordenador estamos

haciendo uso del acrnimo de (Random Access Memory). ste tipo de memorias est

clasificadacomointernaperoenciertomodoesalmismotiempounamemoriaexternayaque

estsituadafueradelprocesador(el"Cerebro"delordenador);escomosublocdenotas.El

procesador tiene una memoria raqutica (se reduce a sus registros), pero una gran facilidad

paramanejarestealmacenamientoauxiliar.Dehecho,granpartedeltrabajodelprocesador

seconcretaentraeryllevardatosdesdeRAMhastasuspropiosregistros.Adiferenciadelos

discos duros (HD) stas memorias son de tipo temporal, es decir, sin energa pierden la

informacinquecontienenporlotantodecimosquesonmemoriasvoltiles,parareferirnosa

memoriasnovoltilesharemosreferenciaamemoriasROM(ReadOnlyMemory),aunqueotra

de las principales diferencias entre stas dos memorias es el acceso, una nos permite la

lecturaescritura(RAM),mientrasquelaotrasloesdelectura(ROM).

Pgina3de19

MemoriasRAM

GuillermoB.

EntreellaspodemosdistinguirdostiposdememoriasRAM:

Estticas:(SRAM)stetipodememoria,mantienesucontenidoinalterado,mientras

recibeenerga.

Dinmicas: (DRAM) Las memorias dinmicas pierden su informacin cuando ste es

ledoyademssidejanderecibirenerga.Paraevitarlasprdidasdeinformacinalserleda

serestauralainformacinquecontienensusceldas(refresco).

Como bien sabemos las memorias RAM, al igual que el resto de elementos hardware, el

desarrollo de la tecnologa de memorias ha sido incesante y por ello hoy en da podemos

distinguir gran variedad de tipos, ya sea por su forma de conectarse a la placabase,

funcionalidad,gestinderecursos,etc.Aquseincluyenalgunostipos:

Los primeros PCs no llegaron a conocer las memorias de ncleos de ferrita, puesto que ya

montaban varias decenas mdulos de DRAM encapsulados en chips DIP ("Dual Inline

Package")de16contactossobrezcalos.Podemosafrimarqueexistenlossiguientestipos:

SIMM(SingleInlineMemoryModule),con3072contactos,mdulos

DIMM(DualInlineMemoryModule),con168contactos.

RIMM(RAMBUSInlineMemoryModule)con184contactos.

EncuantoalosmdulosenformatoSIMM(MdulodeMemoriaenLneaSimple):se

trata de placas de circuito impresas, con uno de sus lados equipado con chips de memoria.

ExistendostiposdemdulosSIMM,segnelnmerodeconectores:

LosmdulosSIMM con30conectores(de89x13mm)sonmemoriasde8bits quese

instalabanenlosPCdeprimerageneracin(286,386).

LosmdulosSIMMcon72conectores(susdimensionesson108x25mm)sonmemorias

capaces de almacenar 32 bits de informacin en forma simultnea. Estas memorias se

encuentranenlosPCquevandesdeel386DXhastalosprimerosPentiums.Enelcasodeestos

ltimos,elprocesadorfuncionaconunbusdeinformacinde64bits,raznporlacual,estos

ordenadoresnecesitanestarequipadoscondosmdulosSIMM.Losmdulosde30clavijasno

pueden instalarse en posiciones de 72 conectores, ya que la muesca (ubicada en la parte

centraldelosconectores)imposibilitaralaconexin.

Pgina4de19

MemoriasRAM

GuillermoB.

LosmdulosenformatoDIMM(MdulodeMemoriaenLneaDoble),sonmemorias

de64bits,locualexplicaporqunonecesitanemparejamiento.LosmdulosDIMMposeen

chips de memoria en ambos lados de la placa de circuito impresa, y poseen a la vez, 84

conectores de cada lado, lo cual suma un total de 168 clavijas. Adems de ser de mayores

dimensionesquelosmdulosSIMM(130x25mm),estosmdulosposeenunasegundamuesca

queevitaconfusiones.

CabeobservarquelosconectoresDIMMhansidomejoradosparafacilitarsuinsercin,gracias

alaspalancasubicadasaambosladosdecadaconector.

Tambin existen mdulos ms pequeos, conocidos comoSO DIMM(DIMM de contorno

pequeo), diseados para ordenadores porttiles. Los mdulosSO DIMMslo cuentan con

144clavijasenelcasodelasmemoriasde64bits,ycon77clavijasenelcasodelasmemorias

de32bits.

Los mdulos en formatoRIMM(Mdulo de Memoria en Lnea Rambus, tambin

conocido comoRDRAMoDRDRAM) son memorias de 64 bits desarrolladas por la empresa

Rambus.Poseen184clavijas.Dichosmdulosposeendosmuescasdeposicin,conelfinde

evitarelriesgodeconfusinconmdulosprevios.

Dada la alta velocidad de transferencia de que disponen, los mdulos RIMM poseen una

pelculatrmicacuyoroleselmejorarlatransferenciadecalor.

Al igual que con los mdulos DIMM, tambin existen mdulos ms pequeos, conocidos

comoSO RIMM(RIMM de contorno pequeo), diseados para ordenadores porttiles. Los

mdulosSORIMMposeenslo160clavijas.

Enlaimagen:MduloDIMMde168contactoscon16MBdeSDRAMjuntoconunantiguochip

de16contactoscon2KBdeDRAM.

Pgina5de19

MemoriasRAM

GuillermoB.

Sobre estos mdulos se conectan los chips de memoria RAM, y existen gran variedad de

variantesdememoriasRAMdependiendodesuusoysuscaractersticas:

VRAM (Vdeo RAM) Acceso de diferentes dispositivos al mismo tiempo. Mejor

rendimientoquelaRAMnormal(mscara).

SIMM (Single In line Memory Module, de 72 contactos) tipo de encapsulado

consistente en una pequea placa de circuito impreso que almacena chips

dememoria, yquese insertaenunzcaloSIMMenlaplaca madreoenla placade

memoria. Los SIMMs son ms fciles de instalar que los antiguos chips de memoria

individuales,yadiferenciadeellossonmedidosenbytesenlugardebits.

DIMM (Dual In line Memory Module, de 168 contactos), un tipo de encapsulado,

consistente en una pequea placa de circuito impreso que almacena chips de

memoria,queseinsertaenunzcaloDIMMenlaplacamadre.

VRAM: Siglas de Vdeo RAM, unamemoriade propsito especial usada por los

adaptadoresdevdeo.AdiferenciadelaconvencionalmemoriaRAM,laVRAMpuede

ser accedida por dos diferentes dispositivos de forma simultnea. Esto permite que

unmonitorpueda acceder a la VRAM para las actualizaciones de la pantalla al

mismotiempoque unprocesadorgrfico suministra nuevosdatos. VRAM permite

mejoresrendimientosgrficosaunqueesmscaraquelaunaRAMnormal.

SIMM:SiglasdeSingleInlineMemoryModule,untipodeencapsuladoconsistenteen

una pequea placa de circuito impreso que almacena chips dememoria, y que se

insertaenunzcaloSIMMenlaplacamadreoenlaplacadememoria.LosSIMMsson

msfcilesdeinstalarquelosantiguoschipsdememoriaindividuales,yadiferencia

deellossonmedidosenbytesenlugardebits.Elprimerformatoquesehizopopular

enloscomputadorespersonalestena3.5"delargoyusabaunconectorde32pins.Un

formato ms largo de 4.25", que usa 72 contactos y puede almacenar hasta 64

megabytes de RAM es actualmente el ms frecuente. Un PC usa tanto memoria de

nuevebits(ochobitsyunbitdeparidad,en9chipsdememoriaRAMdinmica)como

memoriadeochobitssinparidad.Enelprimercasolosochoprimerossonparadatosy

elnovenoesparaelchequeodeparidad.

DIMM:SiglasdeDualInlineMemoryModule,untipodeencapsulado,consistenteen

unapequeaplacadecircuitoimpresoquealmacenachipsdememoria,queseinserta

en un zcalo DIMM en la placa madre y usa generalmente un conector de 168

contactos.

DIP:SiglasdeDualInlinePackage,untipodeencapsuladoconsistenteenalmacenar

unchipdememoriaenunacajarectangularcondosfilasdepinesdeconexinencada

lado.

RAMDisk:SerefierealaRAMquehasidoconfiguradaparasimularundiscoduro.Se

puedeaccederalosficherosdeunRAMdiskdelamismaformaenlaqueseaccedena

losdeundiscoduro.Sinembargo,losRAMdisksonaproximadamentemilesdeveces

Pgina6de19

MemoriasRAM

GuillermoB.

ms rpidos que losdiscos duros, y son particularmente tiles para aplicaciones que

precisandefrecuentesaccesosadisco.DadoqueestnconstituidosporRAMnormal.

losRAMdiskpierdensucontenidounavezquelacomputadoraesapagada.Parausar

los RAM Disk se precisa copiar los ficheros desde undisco duroreal al inicio de la

sesinycopiarlosdenuevoaldiscoduroantesdeapagarlamquina.Observequeen

elcasodefallodealimentacinelctrica,seperdernlosdatosquehubieraenelRAM

disk.ElsistemaoperativoDOSpermiteconvertirlamemoriaextendidaenunRAMDisk

pormediodelcomandoVDISK,siglasdeVirtualDISK,otronombredelosRAMDisks.

MemoriaCachRAMCach:Uncachesunsistemaespecialdealmacenamientode

altavelocidad. Puede ser tanto un rea reservada dela memoriaprincipal como un

dispositivo dealmacenamientode altavelocidadindependiente. Hay dos tipos de

cach frecuentemente usados en lascomputadoraspersonales: memoria cach y

cachdedisco.Unamemoriacach,llamadatambinavecesalmacenamientocach

RAMcach,esunapartedememoriaRAMestticadealtavelocidad(SRAM)msque

la lenta y barata RAMdinmica(DRAM) usada como memoria principal.La

memoriacach es efectiva dado que los programasacceden una y otra vez a los

mismosdatoso

instrucciones.

Guardando

estainformacinen

SRAM,la

computadoraevita acceder a la lenta DRAM. Cuando un dato es encontrado en el

cach,sedicequesehaproducidounimpacto(hit),siendouncachjuzgadoporsu

tasa de impactos (hit rate). Los sistemasde memoria cach usan

unatecnologaconocida por cach inteligente en el cual elsistemapuede reconocer

cierto tipo dedatosusados frecuentemente. Lasestrategiaspara determinar

quinformacindebedeserpuestaenelcachconstituyenunodelosproblemasms

interesantes en la cienciade lascomputadoras. Algunasmemoriascach estn

construidas en laarquitecturade losmicroprocesadores. Por ejemplo, elprocesador

PentiumII tiene una cach L2 de 512 Kbytes. El cach de disco trabaja sobre los

mismosprincipiosquela memoriacach, pero en lugar de usar SRAM de

altavelocidad, usa la convencional memoria principal. Losdatosms recientes

deldisco duroa los que se ha accedido (as como los sectores adyacentes) se

almacenanenunbufferdememoria.Cuandoelprogramanecesitaaccederadatosdel

disco, lo primero que comprueba es la cach del disco para ver si losdatosya estn

ah.Lacachdediscopuedemejorardrsticamenteelrendimientodelasaplicaciones,

dadoqueaccederaunbytededatosenRAMpuedesermilesdevecesmsrpidoque

accederaunbytedeldiscoduro.

SRAM Siglas de Static RandomAccessMemory, es un tipo de memoria que es ms

rpida y fiable que la ms comn DRAM (Dynamic RAM). El trmino estticaviene

derivadodelhechoquenecesitaserrefrescadamenosvecesquelaRAMdinmica.Los

chipsdeRAMestticatienentiemposdeaccesodelordende10a30nanosegundos,

mientrasquelasRAMdinmicasestnporencima de30,ylasmemoriasbipolaresy

ECL se encuentran por debajo de 10 nanosegundos. Un bit de RAMestticase

construye con un como circuito flipflop que permite que la corriente fluya de un

ladoaotrobasndoseencualdelosdostransistoresesactivado.LasRAMestticasno

precisandecircuiteraderefrescocomosucedeconlasRAMsdinmicas,peroprecisan

msespacioyusanmasenerga.LaSRAM,debidoasualtavelocidad,esusadacomo

memoriacach.

DRAM Siglas de Dynamic RAM, un tipo de memoria de gran capacidad pero que

precisa ser constantemente refrescada (reenergizada) o perdera su contenido.

Generalmente usa untransistory un condensador para representar un bit

Loscondensadoresdebe de ser energizados cientos de veces por segundo para

Pgina7de19

MemoriasRAM

GuillermoB.

mantener las cargas. A diferencia de los chips firmware (ROMs, PROMs, etc.) las dos

principales variaciones de RAM (dinmicayesttica) pierden su contenido cuando se

desconectan de laalimentacin. Contrasta con la RAMesttica. Algunas veces en los

anuncios dememorias, la RAMdinmicase indica errneamente como un tipo de

encapsulado;porejemplo"sevendenDRAMs,SIMMsySIPs",cuandodeberadecirse

"DIPs, SIMMs y SIPs" los tres tipos de encapsulado tpicos para almacenar chips de

RAMdinmica. Tambin algunas veces el trmino RAM (RandomAccessMemory) es

utilizadoparareferirsealaDRAMydistinguirladelaRAMesttica(SRAM)queesms

rpida y ms estable que la RAMdinmica, pero que requiere ms energa y es ms

cara

SDRAM Siglas de Synchronous DRAM, DRAM sncrona, un tipo dememoria

RAMdinmicaqueescasiun20%msrpidaquelaRAMEDO.SDRAMentrelazadoso

msmatricesdememoriainternadetalformaquemientrasqueseestaccediendoa

unamatriz, la siguiente se est preparando para el acceso. SDRAMII

estecnologaSDRAM ms rpida esperada para 1998. Tambin conocido como DDR

DRAM o DDR SDRAM (Double Data Rate DRAM o SDRAM), permite leer y

escribirdatosadosveceslavelocidadbs.

FPM:SiglasdeFastPageMode,memoriaenmodopaginado,eldiseomscomnde

chips de RAMdinmica. El acceso a los bits de memoria se realiza por medio de

coordenadas,filaycolumna.Antesdelmodopaginado,eraledopulsandolafilayla

columnadelaslneasseleccionadas.Conelmodopagina,lafilaseseleccionasolouna

vezparatodaslascolumnas(bits)dentrodelafila,dandocomoresultadounrpido

acceso.La memoriaen modo paginado tambin es llamada memoria de modo Fast

PageomemoriaFPM,FPMRAM,FPMDRAM.Eltrmino"fast"fuaadidocuandolos

msnuevoschipsempezaronacorrera100nanosecondseinclusoms.

EDO:SiglasdeExtendedDataOutput,untipodechipdeRAMdinmicaquemejorael

rendimiento del modo de memoria Fast Page alrededor de un 10%. Al ser un

subconjunto de Fast Page, puede ser substituida por chips de modo Fast Page. Sin

embargo, si el controlador de memoria no est diseado para los ms rpidos chips

EDO,elrendimientoserelmismoqueenelmodoFastPage.EDOeliminalosestados

deesperamanteniendoactivoelbufferdesalidahastaquecomienzaelprximociclo.

BEDO (Burst EDO) es un tipo ms rpido de EDO que mejora lavelocidadusando un

contadordedireccinparalassiguientesdireccionesyunestado'pipeline'quesolapa

lasoperaciones.

PBSRAM:SiglasdePipelineBurstSRAM.Sellama'pipeline'aunacategoradetcnicas

que proporcionan unprocesosimultneo, o en paralelo dentro dela computadora, y

se refiere a lasoperacionesde solapamiento moviendodatoso instrucciones en una

'tubera' conceptual con todas las fases del 'pipe' procesando simultneamente. Por

ejemplo, mientras una instruccin se est ejecutando,la computadoraest

decodificandolasiguienteinstruccin.Enprocesadoresvectoriales,puedenprocesarse

simultneamentevariospasosdeoperacionesdecomaflotanteLaPBSRAMtrabajade

estaformaysemueveenvelocidadesdeentre4y8nanosegundos.

Pgina8de19

MemoriasRAM

GuillermoB.

FuncionamientodelamemoriaRAM

Al hacer alusin a que la memoria RAM y referirnos a ella como el bloc de notas del

procesador, es porque sta funciona como apoyo de los registros del procesador. Cualquier

programa en ejecucin est alojado en memoria; las instrucciones van siendo pasadas a los

registros para su ejecucin de forma secuencial, y los datos son pasados tambin a los

registrosparasumanipulacin.

Lamemoriadeaccesoaleatorioconstadecientosdemilesdepequeoscapacitadores

que almacenan cargas. Al cargarse, el estado lgico del capacitador es igual a 1; en el caso

contrario,esiguala0,loqueimplicaquecadacapacitadorrepresentaunbitdememoria.

Teniendo en cuenta que se descargan, los capacitadores deben cargarse constantemente (el

trminoexactoesactualizar)aintervalosregulares,loquesedenominaciclodeactualizacin.

LasmemoriasDRAM,porejemplo,requierenciclosdeactualizacindeunos15nanosegundos

(ns).

Cadacapacitadorestacopladoauntransistor(tipoMOS),locualposibilitala"recuperacin"

o modificacin del estado del capacitador. Estos transistores estn dispuestos en forma de

tabla (matriz), de modo que se accede a lacaja de memoria (tambin llamadapunto de

memoria)medianteunalneayunacolumna.

Heaquunpequeoejemplodecmoestndispuestos:

Puesto que se trata de un almacenamiento voltil, cualquier dato almacenado en memoria

debesersalvadoaunalmacenamientopermanente(disco)antesdeapagarelsistema.

La forma en que se utiliza la memoria depende del SO utilizado.En cuanto a los

sistemastipoMSDOStienenunadisposicin"Mapeado"relativamentecomplicada,loquees

debido a la pequea cantidad de memoria que poda ser direccionada por los primeros

equipos(1MBparael8088).Actualmenteelproblemahadesaparecidoparcialmente,yaque

a partir del 80286los PCs podan direccionar 16 MB; cantidad que fue creciendo

Pgina9de19

MemoriasRAM

GuillermoB.

paulatinamente a 4 GB para el80386y que actualmente llega a 64 GB en los modernos

procesadoresPentiumysimilares.

DRAMPM

LaDRAM(RAMDinmica)eseltipodememoriamscomnenestostiempos.Setratadeuna

memoria cuyostransistoressedisponenenformadematriz,enformadefilasycolumnas.Un

transistor,acopladoconuncapacitador,proporcionainformacinenformadebits.Dadoque

un octeto contiene 8 bits, un mdulo de memoria DRAM de 256 Mo contendr por lo tanto

256 * 2^10 * 2^10 = 256 * 1024 * 1024 = 268.435.456 octetos = 268.435.456 * 8 =

2.147.483.648bits=2.147.483.648transistores.Deestamanera,unmdulode256Moposee

unacapacidadde268.435.456octetos,o268Mo.Lostiemposdeaccesodeestasmemorias

sonde60ns.

Adems, el acceso a la memoria en general se relaciona con la informacin almacenada

consecutivamenteenlamemoria.Deestamanera,elmododerfagapermiteelaccesoalas

trespartesdeinformacinquesiguenalaprimeraparte,sintiempodelatenciaadicional.De

estemodo,eltiemponecesarioparaaccederalaprimerapartedelainformacinesigualal

tiempodelciclomseltiempodelatencia,mientrasqueeltiemponecesarioparaaccedera

lasotrastrespartesdelainformacinsloesigualaltiempodeciclo;loscuatrotiemposde

accesoseexpresan,entonces,enlaformaXYYY.Porejemplo,5333indicaquelamemoria

necesita5ciclosdelrelojparaaccederalaprimerapartedelainformacin,y3paraaccedera

lassubsiguientes.

DRAMFPM

ParaacelerarelaccesoalaDRAM,existeunatcnica,conocidacomopaginacin,quepermite

accederalainformacinubicadaenunamismacolumna,modificandonicamenteladireccin

enlafila,yevitandodeestamanera,larepeticindelnmerodecolumnaentrelecturaspor

fila.EsteprocesoseconocecomoDRAMFPM(MemoriaenModoPaginado).ElFPMalcanza

tiempos de acceso de unos 70 u 80 nanosegundos, en el caso de frecuencias de

funcionamientodeentre25y33Mhz.

DRAMEDO

LaDRAM EDO(Salida de Informacin Mejorada, a veces denominada "hper pgina") se

introdujoen1995.Latcnicautilizadaenestetipodememoriaimplicadireccionarlacolumna

siguientemientrasparalelamenteseestleyendolainformacindeunacolumnaanterior.De

esta manera, se crea un acceso superpuesto que permite ahorrar tiempo en cada ciclo. El

tiempo de acceso de la memoria EDO es de 50 a 60 nanosegundos, en el caso de una

frecuenciadefuncionamientodeentre33y66Mhz.

De modo que la RAM EDO, cuando se utiliza en modo rfaga, alcanza ciclos 5222, lo cual

representa una ganancia de 4 ciclos al acceder a 4 partes de informacin. Dado que la

memoriaEDOnofuncionabaconfrecuenciasmayoresa66Mhz,sesuspendisuusoenfavor

delaSDRAM.

SDRAM

Pgina10de19

MemoriasRAM

GuillermoB.

LaSDRAM(DRAM Sincrnica), introducida en 1997, permite la lectura de la informacin

sincronizadaconelbusdelaplacamadre,adiferenciadeloqueocurreconlasmemoriasEDO

y FPM (conocidas comoasincrnicas), las cuales poseen reloj propio. La SDRAM elimina de

esta manera, los tiempos de espera ocasionados por la sincronizacin con la placa madre.

Gracias a esto se logra un ciclo de modo rfaga de 5111, con una ganancia de 3 ciclos en

comparacin con la RAM EDO. La SDRAM puede, entonces, funcionar con una frecuencia

mayora150MHz,lograndotiemposdeaccesodeunos10ns.

DRSDRAM(RambusDRAM)

LaDRSDRAM(DRAMDirectadeRambus),esuntipodememoriaquepermitelatransferencia

dedatosaunbusde16bitsyaunafrecuenciade800Mhs,loqueproporcionaunanchode

bandade1,6GB/s.AligualquelaSDRAM,estetipodememoriaestsincronizadaconelreloj

delbus,afindemejorarelintercambiodeinformacin.Sinembargo,lamemoriaRAMBUSes

un producto de tecnologa patentada, lo que implica que cualquier empresa que desee

producirmdulosRAMqueutilicenestatecnologadeberabonarregalas,tantoaRAMBUS

comoaIntel.

DDRSDRAM

LaDDRSDRAM(SDRAMdeTasaDobledeTransferenciadeDatos)esunamemoriabasadaen

la tecnologa SDRAM, que permite duplicar la tasa de transferencia alcanzada por sta

utilizandolamismafrecuencia.

La informacin se lee o ingresa en la memoria al igual que un reloj. Las memorias DRAM

estndares utilizan un mtodo conocido comoSDR(Tasa Simple de Transferencia de Datos),

queimplicalalecturaoescrituradeinformacinencadabordedeentrada.

LaDDRpermiteduplicarlafrecuenciadelectura/escrituraconunrelojalamismafrecuencia,

enviandoinformacinacadabordedeentradayacadabordeposterior.

Las memorias DDR por lo general poseen una marca, tal como PCXXXX, en la que "XXXX"

representalavelocidadenMB/s.

Pgina11de19

MemoriasRAM

GuillermoB.

DDR2SDRAM

LasmemoriasDDR2(oDDRII)alcanzanvelocidadesdosvecessuperioresalasmemoriasDDR

conlamismafrecuenciaexterna.

El acrnimo QDR (Tasa Cudruple de Transferencia de Datoso conQuadpump) designa el

mtodo de lectura y escritura utilizado. De hecho, la memoria DDR2 utiliza dos canales

separadosparalosprocesosdelecturayescritura,conlocualescapazdeenviarorecibirel

dobledeinformacinquelaDDR.

La DDR2 tambin posee ms conectores que la DDR clsica (la DDR2 tiene 240, en

comparacinconlos184delaDDR).

Pgina12de19

MemoriasRAM

GuillermoB.

Cuadroderesumen

El siguiente cuadro muestra la equivalencia entre la frecuencia de la placa madre (FSB), la

frecuenciadelamemoria(RAM)ysuvelocidad:

Memoria

Nombre

Frecuencia (RAM)

Frecuencia (RAM)

Velocidad

DDR200

PC1600

200 MHz

100 MHz

1,6 GB/s

DDR266

PC2100

266 MHz

133 MHz

2,1 s

DDR333

PC2700

333 MHz

166 MHz

2,7 s

DDR400

PC3200

400 MHz

200 MHz

3,2 s

DDR433

PC3500

433 MHz

217 MHz

3,5 s

DDR466

PC3700

466 MHz

233 MHz

3,7 s

DDR500

PC4000

500 MHz

250 MHz

4s

DDR533

PC4200

533 MHz

266 MHz

4,2 s

DDR538

PC4300

538 MHz

269 MHz

4,3 s

DDR550

PC4400

550 MHz

275 MHz

4,4 s

DDR2-400

PC2-3200

400 MHz

100 MHz

3,2 s

DDR2-533

PC2-4300

533 MHz

133 MHz

4,3 s

DDR2-667

PC2-5300

667 MHz

167 MHz

5,3 s

DDR2-675

PC2-5400

675 MHz

172,5 MHz

5,4 s

DDR2-800

PC2-6400

800 MHz

200 MHz

6,4 s

Pgina13de19

MemoriasRAM

GuillermoB.

Sincronizacin(tiempos)

Noespococomnvervalorescomo"3222""2332"paradescribirlosparmetrosdela

memoria de acceso aleatorio. Esta sucesin de cuatro cifras describe la sincronizacin de la

memoria (tiempo); es decir, la secuencia de ciclos de reloj necesaria para acceder a la

informacinalmacenadaenlaRAM.Lascuatrocifrascorresponden,enorden,alossiguientes

valores:

Demora de CASolatencia de CAS(CAS significaSealizador de Direccionamiento en

Columna):eselnmerodeciclosderelojquetranscurreentreelenvodelcomandodelectura

y la llegada de la informacin. En otras palabras, es el tiempo necesario para acceder a una

columna.

Tiempo de precarga de RAS(conocido comotRP; RAS significaSealizador de

DireccionamientoenFila):eselnmerodeciclosderelojtranscurridosentredosinstrucciones

deRAS,esdecir,entredosaccesosaunafila.

Demora de RAS a CAS(a veces llamadatRCD): es el nmero de ciclos de reloj

correspondientealtiempodeaccesodeunafilaaunacolumna.

Tiempo activo de RAS(a veces denominadotRAS): es el nmero de ciclos de reloj

correspondientealtiempodeaccesoaunacolumna.

Las tarjetas de memoria estn equipadas con un dispositivo llamadoSPD(Deteccin de

PresenciaenSerie),elcualpermitealBIOSaveriguarlosvaloresdeajustenominalesdefinidos

porelfabricante.SetratadeunaEEPROM,cuyainformacinpuedecargarseenelBIOSsiel

usuarioeligeelajuste"auto".

Estructuralgica

EncuantoalaestructuralgicadelasmemoriasRAM,astassepuedeacceder,tantopara

lectura como para escritura, se accede a los mismos, en grupos de 8 bytes, mediante una

direccin.

Podemosdistinguirdosaspectosquepuedenserrelevantesparalosprogramadores:

Cmoseguardanlosdatos.

Cmoseguardanlosejecutables.

Respectoalosdatos

Aunque la arquitectura de PC permite manejar la memoria en bytes individuales. Muchas

operaciones implican guardar palabras de 16 bits. De estos 2 octetos adyacentes, el de la

izquierda es el ms significativo y el de la derecha el menos. En estos casos, el byte menos

significativo se guarda en la posicin ms baja y el ms significativo a continuacin, en la

posicinmsalta.Estaformadealmacenamientosedenominadepalabrasinvertidas("Back

words")olittleendian.

Respectoalosejecutables

Para ejecutar un programa, ste debe ser previamente cargado en memoria. Pero en la

mayoradeloscasosnosetratadeunacargadelficherotalcualseencuentraeneldisco,sino

que requiere un "acomodo" especial.De este trabajo se encarga un programa especial (de

carga), y se exige que la primera parte del contenido de un fichero .EXE contenga

precisamentelainformacinsobre"como"serealizarlaacomodacinantesaludida.Enel

Pgina14de19

MemoriasRAM

GuillermoB.

casodeWindows,losejecutablesdebencontenerestainformacinenunformatoespecfico,

denominadonuevo formato de fichero ejecutable("New Executable file format"); una

especificacindeMSparalasaplicacionesquedebancorrerbajosusSistemas.

ManutencindelasRAM

Cada punto de memoria se caracteriza as por una direccin que corresponde a su vez a un

nmero de fila y a un nmero de columna. Este acceso no es instantneo; el perodo de

tiempoquellevasedenominatiempodelatencia.Enconsecuencia,eltiemponecesariopara

accederalainformacinenlamemoriaesigualaltiempodelciclomseltiempodelatencia.

De este modo, en el caso de la memoria DRAM, por ejemplo, el tiempo de acceso es de 60

nanosegundos(35nsdeltiempodelcicloms25nsdeltiempodelatencia).Enelordenador,

el tiempo del ciclo corresponde al opuesto de la frecuencia de reloj; por ejemplo, en un

ordenadorconunafrecuenciade200MHz,eltiempodelcicloesde5ns(1/200*106).

Enconsecuencia,enunordenadorconaltafrecuencia,queutilizamemoriasconuntiempode

acceso mucho ms prolongado que el tiempo del ciclo del procesador, se deben

producirestados de esperapara que se permita el acceso a la memoria. En el caso de un

ordenadorconunafrecuenciade200 MHz queutilizamemoriasDRAM(y conuntiempo de

acceso de 60 ns), se generan 11 estados de espera para un ciclo de transferencia. El

rendimientodelordenadordisminuyeamedidaqueaumentaelnmerodeestadosdeespera,

porloqueesrecomendableimplementarelusodememoriasmsrpidas.

ERRORES

Algunasmemoriasposeenmecanismosdecorreccindeerrores,conelfindegarantizarla

integridaddelainformacinquecontienen.Estetipodememoriaseutilizaporlogeneralen

sistemasquetrabajanconinformacinesencial,motivoporelcualestetipodememoriase

encuentraenservidores.

Clasesdeerror

Podemosestablecerdostiposdeerrores:

Erroresduros:Sondebidosaaverasodaosfsicos.Sepresentandeformarecurrenteyson

losmsfcilesdediagnosticar.

Erroresblandos:Ocurrendeformamuyespordica;cuandounbitcambiaespontneamente

de0a1oviceversa.Sonlosmsdifcilesdeprever.Lascausadeestaanomalapuedenser

varias:

Pgina15de19

MemoriasRAM

GuillermoB.

Partculasalfa(enlosprimerosequipos)porcontaminacinconuranioytoriodelmaterialde

encapsuladodelasmemorias.

Rayoscsmicos.Estosrayosdealtaenergapuedencambiarelestadodeuntransistoroun

condensador. El problema es ms frecuente en la SRAM que en las DRAM. Posiblemente se

agravar progresivamente con el aumento de la densidad de integracin de los chips

(componentescadavezmspequeos).

Defectosdesuministroelctrico.Enespecialelruidodealtafrecuenciaenlaalimentacin.Se

recomiendainstalarfiltrosdered.

Interferenciasderadiofrecuencia(RF)motivadasporequiposexternosoelementosdelpropio

sistemaindebidamenteapantallados.

Memoriadevelocidadinadecuadaparaelquipoenquesehainstalado(porejemplo,memoria

PC100enunequipoquenecesitePC133).

Defectosdetemporizacin.Porejemplo,porsobrecarga"Overclocking"delsistema,oporuna

configuracindefectuosadelafrecuenciaderefrescoenlaBIOS.

Sistemasdecorreccin

Yadesdeelprincipio,laexistenciadeerroreshizocobrarrelevanciaalosmecanismoscapaces

dedetectar,yensucasocorregir,losposibleserroresquesepuedanproducirenlosprocesos

de lectura/escritura. A la fecha se emplean principalmente dos mtodos para garantizar la

integridad de los datos: laparidad, y el cdigo de correccin de erroresECC("Error Checking

andCorrection").

Pgina16de19

MemoriasRAM

GuillermoB.

Paridad

Es el mtodo ms comn y tradicional. Consiste en que por cada 8 bits (byte) de

almacenamiento,seaade1bitadicional.Acambiodeaumentarenun12.5%eltamaodela

memoria, se consigue un cierto control sobre la integridad de los datos, ya que este bit

adicional contiene informacin sobre la paridad del conjunto. A este respecto existen dos

protocolos:paridadpareimpar.Sufuncionamientoseesquematizaenlatablasiguiente.

Paridadpar

Paridadimpar

Paso1 El bit de paridad se fija en uno (se Elbitdeparidadsefijaenunosilosbits

activa),silosbitsdedatoscontienen dedatoscontienenunnmeroimparde

un nmero par de unos. Por el unos,ysedesactivasisunmeroespar.

contrario, si el nmero es impar, se

desactiva.

Paso2 Los8bitsdedatosyeldeparidadse Los 8 bits de datos y el de paridad se

almacenanenDRAM.

almacenanenDRAM

Paso3 Los datos son interceptados por el Elprocesoesanlogoaldeparidadpar.

circuito de paridad antes de ser Ladiferenciaesqueeldatoseconsidera

enviadosalprocesador.

vlido si el nmero de unos es par y

erroneoencasocontrario.

Si este circuito identifica un nmero

impar de unos, los datos se

consideran vlidos. Se elimina el bit

de paridad y se traspasanlos bits de

datosalprocesador.

Si el nmero de unos es par, el dato

se considera erroneo y se genera un

errordeparidad.

El modelo de paridad tiene ciertas limitaciones, la principal es que puede detectar el error

peronocorregirlo(nosabecualeselbiterrneo).Adems,sihaymsdeunbitincorrecto,los

bitsdefectuosospuedencancelarseentresyenmascararelerror(sinembargo,laposibilidad

dequeestoocurraesremota).

Paridad artificial. Algunos fabricantes de equipos de baja calidad utilizan un chip de paridad

artificial. Este chip no almacena en realidad ningn bit extra con la paridad del dato. En su

lugargeneranunbitadicionalcuandoeldatodebeseenviadoalcontroladordeparidadconel

valor correcto. En realidad es un mtodo de engaar al controlador de paridad envindole

siemprelasealOk

Pgina17de19

MemoriasRAM

GuillermoB.

RAMconparidadfalsao"virtual":Probablementeobtendrmdulosdememoriaconparidad

virtual en lugar de mdulos con paridad real si solicita RAM con paridad en una tienda de

informtica. Los SIMMs con paridad virtual pueden distinguirse frecuentemente (pero no

siempre)porqueslotienenunchipmsqueunSIMMsinparidad,yporqueelchipextraes

ms pequeo que el resto. Los SIMMs con paridad virtual trabajan exactamente como la

memoriasinparidad.NopuedendecirlecuandoseproduceunerrordebitsimpleenRAM,

algoqueshacenlosSIMMsconparidadrealenunaplacabasequeimplementeparidad.

Consejo: Nunca pague ms por un SIMM con paridad virtual que por uno sin paridad. En

cambio, si que puede llegar a pagar un poco ms por SIMMs con paridad real, porque en

realidadestcomprandounbitmsdememoriaporcada8bits.

ECC:

LosmdulosdememoriaECC(CdigosdeCorreccindeErrores),disponendevariosbits

dedicadosalacorreccindeerrores(conocidoscomobitsdecontrol).Dichosmdulos,

utilizadosprincipalmenteenservidores,permitenladeteccinylacorreccindeerrores.

EstesistemaECC("ErrorCheckingandCorrection")sebasaenunalgoritmomscomplejo,yse

utilizaenPCsdegamaalta,comoservidoresdeRed.Elsistematrabajaenconjuncinconel

controladordememoria,yanexaalosbitsdedatoslosbitsECC,quesonalmacenadosjunto

con los de datos. Estos bits extras, junto con la decodificacin correspondiente, sirven para

realizarlacomprobacinenelmomentodelalectura.

Sudiferenciaprincipalconlaparidadesquepuededetectarelerrordeunbitycorregirlo,con

lo que generalmente el usuario no detecta que se ha producido un error. Dependiendo del

controladordememoriautilizado,elsistemaECCtambinpuededetectarerroresde2,3y4

bits(sumamenteraros),aunqueenestecasonopuedecorregirlos;enestoscasosdevuelveun

errordeparidad.

Tenerencuentaquelaverificacindeerrores(ECCoparidad)depende

ms del la placabase (tipo de controlador de memoria utilizado) que de la

memoriaen s.Lamemoriaponeelalmacenamiento,peroesel controladorel

que decide como se utilizar. Generalmente para poder utilizar una memoria

ECCesnecesariouncontroladorquepuedautilizarestatecnologa.

En ambos casos, paridad o ECC, cuando se detecta un error se produce una excepcin no

enmascarable. Lo que sucede a continuacin depende del Sistema. En algunos casos el

procesadorsedetieneylanzaunarutinaquedejalapantallaenblanco(oazul)ymuestrael

error. En otros se permite ignorar el error, guardar el trabajo en curso y continuar. En

cualquier caso, despus de uno de estos errores, es conveniente pasar al equipo un test de

memoriaespecializado,msseveroqueelrealizadoporlaPOSTdelaBIOS.

Pgina18de19

MemoriasRAM

GuillermoB.

EnlossistemasWindowsesfrecuentequeloserroresdememoriaenlos

momentosdecargadelSistemagenerenmensajesdeavisoindicandoquealgn

fichero importante est corrompido o falta, y debe reinstalarse el Sistema. En

estos casos es imprescindiblerealizar un chequeo exhaustivo de la

memoriaantesderealizarningncambioenelsoftware

Canaldoble

Algunoscontroladoresdememoriadisponendeuncanaldobleparalamemoria.Losmdulos

dememoriaseutilizanenparesconelfindelograrunmayoranchodebandayaspoder

utilizaralmximolacapacidaddelsistema.AlutilizarelCanalDoble,resultaindispensable

utilizarunpardemdulosidnticos(delamismafrecuenciaycapacidad,y,preferentemente,

delamismamarca).

Pgina19de19

También podría gustarte

- ASTM AplicablesDocumento4 páginasASTM AplicablesJuan Alejandro Jurado de la RosaAún no hay calificaciones

- Diagnostico Camion 930e-4Documento8 páginasDiagnostico Camion 930e-4MARIO DEL PINO MUÑOZAún no hay calificaciones

- LIBRO Version 2.0 Calidad de SoftwareDocumento234 páginasLIBRO Version 2.0 Calidad de SoftwareViridiana Jimenez100% (1)

- Infoplc Net Manual Formacion Vijeo DesignerDocumento130 páginasInfoplc Net Manual Formacion Vijeo DesignerCristóbal Eduardo Carreño MosqueiraAún no hay calificaciones

- Estimulación de PozosDocumento26 páginasEstimulación de PozosVivi Bonilla100% (1)

- ConkyDocumento2 páginasConkyRubén Darío SalgadoAún no hay calificaciones

- Conky LuaDocumento2 páginasConky LuaRubén Darío SalgadoAún no hay calificaciones

- Mas de Lo MismoDocumento2 páginasMas de Lo MismoRubén Darío SalgadoAún no hay calificaciones

- Parcial 1 - Contabilidad - Estado de Resultados - Scribd: 1 Respuesta 6 Dic. 2017Documento2 páginasParcial 1 - Contabilidad - Estado de Resultados - Scribd: 1 Respuesta 6 Dic. 2017Rubén Darío SalgadoAún no hay calificaciones

- Mas de Lo MismoDocumento2 páginasMas de Lo MismoRubén Darío SalgadoAún no hay calificaciones

- Mas y MasDocumento2 páginasMas y MasRubén Darío SalgadoAún no hay calificaciones

- PDF BusquedaDocumento2 páginasPDF BusquedaRubén Darío SalgadoAún no hay calificaciones

- Algebra Lineal Semana 4 PDFDocumento5 páginasAlgebra Lineal Semana 4 PDFRubén Darío SalgadoAún no hay calificaciones

- PDF BusquedaDocumento2 páginasPDF BusquedaRubén Darío SalgadoAún no hay calificaciones

- PDF BusquedaDocumento2 páginasPDF BusquedaRubén Darío SalgadoAún no hay calificaciones

- Beneficiado Húmedo ANACAFEDocumento10 páginasBeneficiado Húmedo ANACAFEjulio cordonAún no hay calificaciones

- Relacion Lluvia-EscurrimientoDocumento13 páginasRelacion Lluvia-EscurrimientoAbiimaeel Raga 'RdgzAún no hay calificaciones

- Manual RefrigeradorDocumento30 páginasManual RefrigeradorGilberto LópezAún no hay calificaciones

- ETL UntelsDocumento48 páginasETL UntelssamputaAún no hay calificaciones

- EjerciciosDocumento36 páginasEjercicioslimbergAún no hay calificaciones

- Procesadores de Texto Basados en WebDocumento9 páginasProcesadores de Texto Basados en WeblorelijiAún no hay calificaciones

- Inspecciones Planeadas Doc. TallerDocumento6 páginasInspecciones Planeadas Doc. Tallerhumberto sepulveda sandovalAún no hay calificaciones

- SOP Instalación Ventilación Forzada Variadores InyecciónDocumento7 páginasSOP Instalación Ventilación Forzada Variadores InyecciónAndrea Del Pilar GAVIRIA BAHAMONAún no hay calificaciones

- Grupo 6 - Nuevo Metodo AustriacoDocumento16 páginasGrupo 6 - Nuevo Metodo AustriacoOscar Zuñiga SolariAún no hay calificaciones

- Evaluacion FinalDocumento3 páginasEvaluacion Finaledwin ferneyAún no hay calificaciones

- 1GDL de EstructurasDocumento11 páginas1GDL de EstructurasKaren MayaAún no hay calificaciones

- 08 Ocho Casos de Accidente Por Desprendimiento de RocasDocumento24 páginas08 Ocho Casos de Accidente Por Desprendimiento de RocasJose CecenarroAún no hay calificaciones

- Soodle Mundos Virtuales Universidad Rey Juan Carlos TesisDocumento511 páginasSoodle Mundos Virtuales Universidad Rey Juan Carlos TesisTito HerreraAún no hay calificaciones

- Practicas BCRP 2019 PDFDocumento5 páginasPracticas BCRP 2019 PDFJesus E. Mescua CaceresAún no hay calificaciones

- D2. Semejanzas y DiferenciasDocumento2 páginasD2. Semejanzas y DiferenciasMajo AvilaAún no hay calificaciones

- Tomo I Mapro PDFDocumento270 páginasTomo I Mapro PDFFrank Carlos Barrionuevo TeranAún no hay calificaciones

- Compendio Normas Adm PDFDocumento192 páginasCompendio Normas Adm PDFJose CarlosAún no hay calificaciones

- Guia Tipo de Reacciones QuimicasDocumento6 páginasGuia Tipo de Reacciones QuimicasalvarezcamiloAún no hay calificaciones

- Memoria DescriptivaDocumento21 páginasMemoria DescriptivaJeanPierrePazosAún no hay calificaciones

- Composición Arquitectónica Galvan Castro CarlosDocumento60 páginasComposición Arquitectónica Galvan Castro CarlosLuis Fernando Cruz ContrerasAún no hay calificaciones

- Et 470 1Documento12 páginasEt 470 1flor urra sotoAún no hay calificaciones

- PR 10Documento2 páginasPR 10Jonathan Terrón100% (1)

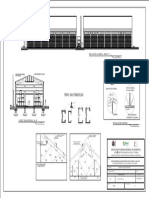

- Plano Silo de Almacenamiento de Papa 2-4Documento1 páginaPlano Silo de Almacenamiento de Papa 2-4Kevin Padilla LopezAún no hay calificaciones

- Ej SELECTIVIDAD Quimica T 10 ReducidoDocumento2 páginasEj SELECTIVIDAD Quimica T 10 ReducidoRodeo CrabAún no hay calificaciones

- Formato Proyecto 2do Avance - 2023 - 1Documento5 páginasFormato Proyecto 2do Avance - 2023 - 1Alisson Mirella Robles NizamaAún no hay calificaciones