Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Practica - 01 - Compuertas Lógicas - 404 PDF

Cargado por

DjAngel Ďē La Ĉruž RwaamsTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Practica - 01 - Compuertas Lógicas - 404 PDF

Cargado por

DjAngel Ďē La Ĉruž RwaamsCopyright:

Formatos disponibles

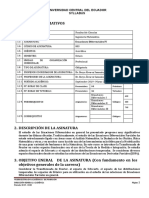

UNIVERSIDAD TECNOLOGICA DEL SURESTE DE

VERACRUZ

Carrera

Mantenimiento rea industrial

Materia

Electrnica digital

Docente

Ing. Juan Carlos Hernndez Cruz

Trabajo

Practica No. 1

Compuertas lgicas

Alumno(s)

_____________________________

_____________________________

_____________________________

Cuatrimestre

Cuarto

Grupo

404

UNIVERSIDAD TECNOLOGICA DEL SURESTE DE

VERACRUZ

MANUAL DE PRACTICAS DE ELECTRNICA DIGITAL

DC-MAI-MP-01

REVISION: 1

FECHA:

01/09/14

PAG. 2 DE

Titulo

Compuertas lgicas

Prctica #1

Nombre de la asignatura

Electrnica digital

Cuatrimestre

Cuarto

Unidad temtica

I. Lgica digital

Tema (s)

1.2 Compuertas lgicas y tablas de verdad

Lugar Duracin

Laboratorio de electrnica 4 horas

Objetivo:

El alumno entender los conceptos bsicos necesarios en la

realizacin de circuitos lgicos, as como conocer los distintos tipos

de compuertas lgicas bsicas, mediante la comprobacin de las

tablas de verdad que rigen a estas clulas lgicas

Materiales Maquinaria y equipo Herramientas

1 Protoboard.

1 SN74LS00.

1 SN74LS02.

1 SN74LS04.

1 SN74LS08.

1 SN74LS32.

1 SN74LS86.

5 Resistencias de carbn de

330 a W.

Cable calibre 22 AWG.

1 Fuente de

alimentacin.

1 Multmetro digital.

Pinzas de corte.

Pinzas de Punta

Introduccin

Los sistemas digitales se caracterizan por funcionar de modo binario, es decir, emplean

dispositivos mediante los cuales slo son posibles dos estados: alto y bajo 1 lgico y 0 lgico.

Dependiendo del estado y del nivel lgico se pueden establecer dos sistemas lgicos:

1) Lgica Positiva. Cuando el estado alto coincida con el 1 lgico y el estado bajo con el 0

lgico.

2) Lgica Negativa negada. Cuando el estado alto coincida con el 0 lgico y el estado bajo

con el 1 lgico.

Es innegable que existen diferentes tecnologas o familias para el desarrollo y construccin de

sistemas lgicos, de las cuales se destacan las siguientes familias:

1) Familia RTL: Lgica de Transistor-Resistencia.

2) Familia DTL: Lgica de Transistor-Diodo.

3) Familia TTL: Lgica de Transistor-Transistor.

4) Familia ECL: Lgica acoplada por emisor.

sta prctica se realizar con circuitos lgicos TTL, por ser sta una de las ms usadas en la

actualidad. En esta primera prctica no se realizarn bloques funcionales slo se realizar la

comprobacin de las tablas de la verdad de cada compuerta lgica bsica, as como determinar

la equivalencia de los estados lgicos 0 y 1 en voltios.

Marco terico

Compuerta lgica.

Tabla de verdad.

Desarrollo de la prctica

1) Compuerta OR (74LS32)

a) Montar el circuito de la figura 1.

Figura 1. Compuerta OR de dos entradas. Figura 2. Datos tcnicos del 74LS32.

b) Llenar la tabla 1 con los valores lgicos y de tensin medidos tanto en las entradas (I1

e I2) como en la salida (O3).

I1 I2 O3

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 1. Comportamiento de la compuerta OR.

2) Compuerta AND (74LS08)

c) Montar el circuito de la figura 3.

Figura 3. Compuerta AND de dos entradas. Figura 4. Datos tcnicos del 74LS08.

d) Llenar la tabla 2 con los valores lgicos y de tensin medidos tanto en las entradas (I1

e I2) como en la salida (O3).

I1 I2 O3

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 2. Comportamiento de la compuerta AND.

3) Compuerta NOT (74LS04)

e) Montar el circuito de la figura 5.

Figura 5. Compuerta NOT. Figura 6. Datos tcnicos del 74LS32.

f) Llenar la tabla 3 con los valores lgicos y de tensin medidos tanto en la entrada (I1)

como en la salida (O2).

I1 O2

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 3. Comportamiento de la compuerta NOT.

4) Compuerta NOR (74LS02)

g) Montar el circuito de la figura 7.

Figura 7. Compuerta NOR de dos entradas. Figura 8. Datos tcnicos del 74LS02.

h) Llenar la tabla 4 con los valores lgicos y de tensin medidos tanto en las entradas (I1

e I2) como en la salida (O3).

I2 I3 O1

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 4. Comportamiento de la compuerta NOR.

5) Compuerta NAND (74LS00)

i) Montar el circuito de la figura 9.

Figura 9. Compuerta NAND de dos entradas. Figura 10. Datos tcnicos del 74LS00.

j) Llenar la tabla 5 con los valores lgicos y de tensin medidos tanto en las entradas (I1

e I2) como en la salida (O3).

I1 I2 O3

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 5. Comportamiento de la compuerta NAND.

6) Compuerta XOR (74LS86)

k) Montar el circuito de la figura 11.

Figura 11. Compuerta NAND de dos entradas. Figura 12. Datos tcnicos del 74LS86.

l) Llenar la tabla 6 con los valores lgicos y de tensin medidos tanto en las entradas (I1

e I2) como en la salida (O3).

I1 I2 O3

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Estado

lgico

Nivel de

tensin

Tabla 6. Comportamiento de la compuerta XOR.

Observaciones y conclusiones

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

_____________________________________________________________

Bibliografa

Electrnica digital y microprogramable; Jos Ma. Angulo Usategui, Juan Carlos

Hernndez Martn, Ma. ngeles Prieto Blanco, Mikel Etxebarria Isuskiza,

Ignacio Angulo Martnez; Editorial Paraninfo.

También podría gustarte

- Autoestima BienDocumento48 páginasAutoestima BienDjAngel Ďē La Ĉruž Rwaams100% (2)

- Metodos de Aplicación de LubricanteDocumento4 páginasMetodos de Aplicación de LubricanteDjAngel Ďē La Ĉruž RwaamsAún no hay calificaciones

- Desgaste Por CorrosionDocumento8 páginasDesgaste Por CorrosionDjAngel Ďē La Ĉruž Rwaams100% (1)

- Manual de Procedimiento A Instalaciones ElectricasDocumento8 páginasManual de Procedimiento A Instalaciones ElectricasDjAngel Ďē La Ĉruž Rwaams100% (2)

- Programa de Mantenimiento de Un Sistema de Aire AcondicionadoDocumento3 páginasPrograma de Mantenimiento de Un Sistema de Aire AcondicionadoDjAngel Ďē La Ĉruž Rwaams100% (1)

- Tarea Expresion Oral y EscritaDocumento7 páginasTarea Expresion Oral y EscritaDjAngel Ďē La Ĉruž RwaamsAún no hay calificaciones

- Repaso Prueba 1 - UaDocumento27 páginasRepaso Prueba 1 - Uaalfonso curayAún no hay calificaciones

- Citas BibliográficasDocumento5 páginasCitas Bibliográficasluis miguelAún no hay calificaciones

- SylabussDocumento9 páginasSylabussCristhian Taramuel GuerreroAún no hay calificaciones

- Accesibilidad Al Medio FísicoDocumento157 páginasAccesibilidad Al Medio FísicoAndre RodriguezAún no hay calificaciones

- Evalua 4Documento89 páginasEvalua 4Nelly Viviana López Jaña82% (11)

- Cruce TrihíbridoDocumento1 páginaCruce TrihíbridoSara VelásquezAún no hay calificaciones

- GM E1 Armijo Rico PilarDocumento8 páginasGM E1 Armijo Rico PilarPilarAún no hay calificaciones

- Episodio IX Duelo de Los DestinosDocumento201 páginasEpisodio IX Duelo de Los Destinospuebla492Aún no hay calificaciones

- La Etica Como Pilar de La Responsabilidad Social Del Perito Contable - Cpc. Carlos Pastor CarrascDocumento60 páginasLa Etica Como Pilar de La Responsabilidad Social Del Perito Contable - Cpc. Carlos Pastor CarrascCornelia Isuiza AmasifuenAún no hay calificaciones

- ResumenDocumento3 páginasResumenkathy AnchatuñaAún no hay calificaciones

- Conferencia 20 y 21 de FreudDocumento1 páginaConferencia 20 y 21 de FreudMirkoAún no hay calificaciones

- Resumen Capítulo 1, Vázquez-AyoraDocumento5 páginasResumen Capítulo 1, Vázquez-Ayoramarcio betancoAún no hay calificaciones

- Ept4 Tic4 U6Documento2 páginasEpt4 Tic4 U6Eusebio Huiza CuadrosAún no hay calificaciones

- Analisis Delictual PDFDocumento148 páginasAnalisis Delictual PDFrmaddio1100% (1)

- Atomo IIDocumento5 páginasAtomo IIAntonio Montalvo CorreaAún no hay calificaciones

- El Utilitarismo InglésDocumento4 páginasEl Utilitarismo InglésAndrésAún no hay calificaciones

- ReingenieríaDocumento3 páginasReingenieríaCANDY LORENA ARROYO ORTEGAAún no hay calificaciones

- Alineamiento Laser SENATIDocumento6 páginasAlineamiento Laser SENATIcar_linAún no hay calificaciones

- Series Taylor PDFDocumento3 páginasSeries Taylor PDFBryan AndersonAún no hay calificaciones

- Cargo Especialidad Código Cantidad Retribución Mensual Área Contratante DependenciaDocumento8 páginasCargo Especialidad Código Cantidad Retribución Mensual Área Contratante DependenciaGladys Alanoca RiveraAún no hay calificaciones

- 2-Presion CapilarDocumento28 páginas2-Presion Capilaryogiboy1789Aún no hay calificaciones

- PEDROSA, FERNANDO (Comp.), (2014), Lecturas para La Sociedad y El Estado, Buenos Aires, EUDEBA.Documento75 páginasPEDROSA, FERNANDO (Comp.), (2014), Lecturas para La Sociedad y El Estado, Buenos Aires, EUDEBA.AugustoAún no hay calificaciones

- Autoridades Mapuches ExplicaciónDocumento4 páginasAutoridades Mapuches Explicaciónyessy_11808633Aún no hay calificaciones

- UEFA C Área Entorno Módulo Clima de MotivaciónDocumento6 páginasUEFA C Área Entorno Módulo Clima de MotivaciónaromacoAún no hay calificaciones

- El Informe InstitucionalDocumento5 páginasEl Informe InstitucionalPablo D. Salinas100% (1)

- Plan - Mejora Continua - IespphDocumento5 páginasPlan - Mejora Continua - IespphValentin Esteban ValladolidAún no hay calificaciones

- Instrucciones Generales para La Ordenacion de Montes Arbolados CylDocumento97 páginasInstrucciones Generales para La Ordenacion de Montes Arbolados CylanchaferAún no hay calificaciones

- Señales de RastreoDocumento3 páginasSeñales de RastreoNicol SalinasAún no hay calificaciones

- Sistema Becas y BeneficiosDocumento37 páginasSistema Becas y BeneficiosNelson Mamani RojasAún no hay calificaciones

- Efecto de La Agricultura Intensiva en El Ciclo Del Carbono y Nitrógeno en Sistemas DulceacuícolasDocumento4 páginasEfecto de La Agricultura Intensiva en El Ciclo Del Carbono y Nitrógeno en Sistemas DulceacuícolasrocioAún no hay calificaciones