Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Aporte Cuatro Microelectronica Carlos Suarez

Aporte Cuatro Microelectronica Carlos Suarez

Cargado por

CAAM04070 calificaciones0% encontró este documento útil (0 votos)

8 vistas2 páginasDerechos de autor

© © All Rights Reserved

Formatos disponibles

DOCX, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

8 vistas2 páginasAporte Cuatro Microelectronica Carlos Suarez

Aporte Cuatro Microelectronica Carlos Suarez

Cargado por

CAAM0407Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOCX, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

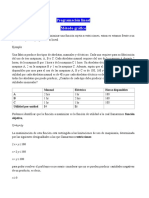

2.

CARACTERSTICAS DEL DISEO

CON PLDs

Los PLDs estn situados en una zona

intermedia entre los dispositivos a

medida y la lgica de catlogo

formada por los CI de funcin fija.

Tienen casi todas las ventajas de los

ASICs sin estar penalizados por un

costo elevado para pequeas series.

Adems el ciclo de diseo con PLDs

es mucho ms rpido que los de las

matrices de puertas o las clulas

normalizadas. En determinadas

aplicaciones, un PLD puede sustituir

desde unos pocos hasta unas

decenas de CI de funcin fija,

mientras que los grandes ASICs

pueden sustituir a cientos e incluso

miles de CI. En ocasiones, los PLD

se utilizan para realizar prototipos que

posteriormente se llevarn a un ASIC

ms complejo.

El trabajo con PLDs proporciona:

facilidad de diseo, prestaciones,

fiabilidad, economa y seguridad.

2.1. Facilidad de diseo

Las herramientas de soporte al

diseo con PLDs facilitan

enormemente este proceso. Las

hojas de codificacin que se

utilizaban en 1975 han dejado paso a

los ensambladores y compiladores de

lgica programable (PALASM,

AMAZE, ABEL, CUPL, OrCAD/PLD,

etc.). Estas nuevas herramientas

permiten expresar la lgica de los

circuitos utilizando formas variadas

de entrada tales como; ecuaciones,

tablas de verdad, procedimientos

para mquinas de estados,

esquemas, etc. La simulacin digital

posibilita la depuracin de los diseos

antes de la programacin de los

dispositivos. Todo el equipo de

diseo se reduce a un software de

bajo coste que corre en un PC, y a un

programador.

2.2. Prestaciones.

Los PLDs TTL que hay en el mercado

tienen tiempos de conmutacin tan

rpidos como los circuitos integrados

de funcin fija ms veloces. Los PLDs

ECL son todava ms rpidos. Sin

embargo, el incremento de velocidad

obtenido con los dispositivos CMOS,

que ya han igualado o superado en

prestaciones a los dispositivos TTL,

est provocando el abandono de la

tecnologa bipolar por parte de los

fabricantes. En cuanto al consumo de

potencia, los PLDs generalmente

consumen menos que el conjunto de

chips a los que reemplazan.

2.3. Fiabilidad.

Cuanto ms complejo es un circuito,

ms probabilidades hay de que

alguna de sus partes falle. Puesto

que los PLDs reducen el nmero de

chips en los sistemas, la probabilidad

de un fallo disminuye. Los circuitos

impresos con menor densidad de CI

son ms fciles de construir y ms

fiables. Las fuentes de ruido tambin

se reducen.

2.4. Economa.

En este apartado, hay aspectos que

resultan difciles de cuantificar. Por

ejemplo, los costes de prdida de

mercado por una introduccin tarda

de un producto. Otros son ms

claros, por ejemplo, la reduccin del

rea de las placas de circuito impreso

obtenida gracias a que cada PLD

sustituye a varios circuitos integrados

de funcin fija. Muchas veces se

consigue reducir el nmero de placas

de circuito impreso economizndose

en conectores. La reduccin de

artculos en almacn tambin aporta

ventajas econmicas.

De la misma manera que para altos

volmenes de produccin las

memorias ROM resultan de menor

coste que las EPROM, las HAL (Hard

Array Logic) o PLDs programados por

el fabricante proporcionan ahorros

adicionales en grandes cantidades.

También podría gustarte

- Iles Greg - El Prisionero de SpandauDocumento724 páginasIles Greg - El Prisionero de SpandauGermánPerrottaAún no hay calificaciones

- CAMINOS 01 y 02 (Segunda Semana) 04y05!09!2021 - CompressedDocumento113 páginasCAMINOS 01 y 02 (Segunda Semana) 04y05!09!2021 - CompressedCesar Rumiche HernándezAún no hay calificaciones

- PV - Taladros CalientesDocumento23 páginasPV - Taladros CalientesFernando Terán ToledoAún no hay calificaciones

- Recetario - 20 09 2022Documento56 páginasRecetario - 20 09 2022CINTIA CANTÓ ESTEVEAún no hay calificaciones

- Blanco, Henry - Entregable. Teorías de ComercioDocumento2 páginasBlanco, Henry - Entregable. Teorías de Comerciohblanco0425Aún no hay calificaciones

- Cartilla de 1º de Comunion 2017Documento41 páginasCartilla de 1º de Comunion 2017Emmanuel RamosAún no hay calificaciones

- Aparato Reproductor Masculino Final HOMBREDocumento8 páginasAparato Reproductor Masculino Final HOMBREMauricio SanchezAún no hay calificaciones

- 17 La Resurrección 15.05.28 PDFDocumento25 páginas17 La Resurrección 15.05.28 PDFHector SilvaAún no hay calificaciones

- Practica Calificada Teoria - CORROSIONDocumento4 páginasPractica Calificada Teoria - CORROSIONAnthony Rafael QuirozAún no hay calificaciones

- Estudio de Caso Agua ProducidaDocumento15 páginasEstudio de Caso Agua ProducidaGrisel GutierrezAún no hay calificaciones

- La Deshumanizacion Del Arte, Ortega y GassetDocumento5 páginasLa Deshumanizacion Del Arte, Ortega y GassetJuanma MartínAún no hay calificaciones

- 2021 Ficha Bloque ERNCCachipambaDocumento4 páginas2021 Ficha Bloque ERNCCachipambaCarlos LopezAún no hay calificaciones

- 797b2 Mazda3 Manual para El Propietario 8DZ9-SP-15J OMDocumento727 páginas797b2 Mazda3 Manual para El Propietario 8DZ9-SP-15J OMGerardo Marcelo PizarroAún no hay calificaciones

- Geometria Euclidiana y FractalDocumento48 páginasGeometria Euclidiana y FractalAle Hurtado100% (1)

- Profesionales Ingenieria CivilDocumento3 páginasProfesionales Ingenieria CivilFabio Forero TottoAún no hay calificaciones

- Modelo de Informe de AuxiliarDocumento4 páginasModelo de Informe de AuxiliarOscar QpAún no hay calificaciones

- Resumen Examen LegislacionDocumento10 páginasResumen Examen Legislacionamalfy fañaAún no hay calificaciones

- BRONCOSDocumento3 páginasBRONCOSSantiago AvilaAún no hay calificaciones

- Taller Mecanico y MetrologiaDocumento13 páginasTaller Mecanico y MetrologiaDenys PilamungaAún no hay calificaciones

- Determinación de Campos MagnéticosDocumento13 páginasDeterminación de Campos Magnéticosrgutierrez_778809Aún no hay calificaciones

- 7 Document A CioDocumento839 páginas7 Document A CioMahranBarhoumiAún no hay calificaciones

- TAREA 2 Estructura Molecular - Jessica TorresDocumento17 páginasTAREA 2 Estructura Molecular - Jessica TorresMarlen copete100% (1)

- 4.1 Programacion Lineal-Metodo graficoDIEGODocumento8 páginas4.1 Programacion Lineal-Metodo graficoDIEGODiego Hernández GuerreroAún no hay calificaciones

- Realidad Virtual en Rehabilitación NeurológicaDocumento6 páginasRealidad Virtual en Rehabilitación NeurológicaKatherine PucoAún no hay calificaciones

- Crema Cannabis y RomeroDocumento14 páginasCrema Cannabis y RomeroFanny Wiki MonteroAún no hay calificaciones

- Apunte Polinomio Interpolacion LagrangeDocumento6 páginasApunte Polinomio Interpolacion Lagrangescarleth andradesAún no hay calificaciones

- Guia PRIMEROS Metodo CientificoDocumento9 páginasGuia PRIMEROS Metodo CientificoJohanna Miranda RojasAún no hay calificaciones

- Triptico Aparato Reproductor MasculinoDocumento2 páginasTriptico Aparato Reproductor MasculinoDavid Hidalgo67% (3)

- Ley General de SaludDocumento27 páginasLey General de SaludMaggi Jimenez100% (1)

- Informe Vertedero Cresta AnchaDocumento8 páginasInforme Vertedero Cresta AnchaDiego Armando Gutierrez PerezAún no hay calificaciones