Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Intrfase Xilinix

Cargado por

duzter_jaguar0 calificaciones0% encontró este documento útil (0 votos)

8 vistas15 páginasTítulo original

IntrfaseXilinix

Derechos de autor

© Attribution Non-Commercial (BY-NC)

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Attribution Non-Commercial (BY-NC)

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

8 vistas15 páginasIntrfase Xilinix

Cargado por

duzter_jaguarCopyright:

Attribution Non-Commercial (BY-NC)

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 15

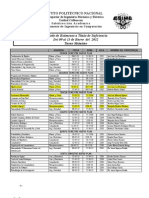

Manejo de la Intefaz ISE XILINIX

Este software se utiliza para crear proyectos con el Kit SPARTAN 3; el cual maneja un FPGA XC3S200. Este permite la simulacin e implementacin para la tarjeta con lenguaje HDL y VERILOG.

1) Creacin del proyecto 2) Archivo VHDL 3) Asignacin del entradas y salidas del chip 4) Grabacin del dispositivo

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del proyecto

1) Se entra al men principal Creacin del proyecto y seleccionamos la opcin nuevo proyecto, debemos asignar un nombre al proyecto, la ubicacin y por convencin usamos el mdulo principal como HDL y se continua dando siguiente:

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del proyecto

2) En el paso siguiente asignamos el manejador de tarjeta a usar, para este caso usamos el SPARTAN 3 y el chip XC3S200, no asignamos nada ms ya que usaremos valores estndar.

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del proyecto

4) En el paso siguiente asignamos el tipo de archivo a usar para la creacin del circuito, estos on de varios tipos, pero usaremos el mdulo VHDL

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del proyecto

5) En el paso siguiente asignamos el nombre para el archivo fuente a usar en el diseo.

Verificar este parmetro de encapsula do o la asignacin de pines no funciona

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del proyecto

6) En el paso siguiente asignamos el nombre de la entidad a crear y la asignacin de entradas y salidas ; esto ahorra la escrituracin en el lenguaje, si se deja el nombre de la arquitectura behavorial no hay problema, posteriormente tendremos la informacin generada para el proyecto y oprimimos el botn de finalizar.

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del archivo VHDL

1) El archivo HDL se genera de forma automtica asigna la numeracin de lneas al crear el proyecto. En la ventana del proyecto aparece el mdulo con el nombre propuesto en la creacin del proyecto.

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del archivo VHDL

2) El archivo HDL de manera automtica va colocando el color a cada variable y palabra clave auxiliando en la edicin del programa; es necesario establecer el comportamiento (funcionamiento) del circuito; debemos revisar su sintaxis para iniciar el proceso de implantacin en el chip.

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del archivo VHDL

3) En la ventana de proyecto aparece la opcin sntesis de XST, al orimir en la opcin de expansin de men (+) aparecer la opcin check syntaxis; debemos dar doble clic en esta para iniciar la revisin; si existen errores en la ventana de errores(parte inferior de la ventana) se mencionara la lnea donde se ubica y el tipo del mismo. Cuando hay error un tache de color rojo en la opcin check syntaxis.

Circuitos Lgicos II Carlos A. Estrada Arriaga

Creacin del archivo VHDL

3) En la ventana de proyecto aparece la opcin syntesize de XST, al oprimir en la opcin de expansin de men (+) aparecer la opcin check syntaxis; debemos dar doble clic en esta para iniciar la revisin; si existen errores en la ventana de errores(parte inferior de la ventana) se mencionara la lnea donde se ubica y el tipo del mismo. Cuando hay error un tache de color rojo en la opcin check syntaxis. Al corregir el error se realiza el proceso nuevamente hasta que se obtenga una verificacin satisfactoria (paloma verde)

Circuitos Lgicos II Carlos A. Estrada Arriaga

10

Asignacin de pines (1)

La asignacin de pines se establece al usar el men mostrado en la parte inferior Este se encarga de crear la asignacin de los pines dentro de un archivo de control de extensin UCF; a este se le debe dar doble clic par llamar al programa que realiza esa funcin.

Circuitos Lgicos II Carlos A. Estrada Arriaga

11

Asignacin de pines (2)

Los pines se asignan en la ventana de I/O del objeto, esta se encuentra parcialmente llena con los parmetros que da el sistema mismo

Los pines se asignan en la ventana de I/O del objeto, debemos usar para la tarjeta el valor mostrado para que se reconozca la terminal como TTL de baja velocidad en la tarjeta SPARTAN III de prueba. El pin del FPGA se coloca en esta casilla K13 la salida es K12 Los tipos de salida son optativos

Circuitos Lgicos II Carlos A. Estrada Arriaga

12

Grabacin del circuito

Se usa la opcin grabar Impact siguiendo los pasos: 1) Crear el archivo de salida y una vez que esta verificado

Circuitos Lgicos II Carlos A. Estrada Arriaga

13

Grabacin del circuito (2)

Se usa la opcin grabar Impact siguiendo los pasos: 1) Crear el archivo de salida y una vez que esta verificado

Circuitos Lgicos II Carlos A. Estrada Arriaga

14

Grabacin del circuito (1)

Dar aceptar: 1) Crear el archivo de salida y una vez que esta verificado

Circuitos Lgicos II Carlos A. Estrada Arriaga

15

También podría gustarte

- Python Power 1 PDFDocumento84 páginasPython Power 1 PDFGust Ral Tool100% (1)

- Seguridad en El Gestionamiento de La Informacion+UnamDocumento180 páginasSeguridad en El Gestionamiento de La Informacion+Unamduzter_jaguarAún no hay calificaciones

- Seguridad en El Gestionamiento de La Informacion+UnamDocumento180 páginasSeguridad en El Gestionamiento de La Informacion+Unamduzter_jaguarAún no hay calificaciones

- Unidad 1Documento53 páginasUnidad 1duzter_jaguarAún no hay calificaciones

- Capitulo7 PDFDocumento9 páginasCapitulo7 PDFduzter_jaguarAún no hay calificaciones

- Practica No 8Documento8 páginasPractica No 8Luisangelmtz MtzAún no hay calificaciones

- Guia2 AutomatasFinitos2012Documento8 páginasGuia2 AutomatasFinitos2012teletubie9999Aún no hay calificaciones

- Algebra BooleDocumento10 páginasAlgebra BooleFernando Repullo FuentesAún no hay calificaciones

- ReadmeDocumento1 páginaReadmesport0378Aún no hay calificaciones

- ETS 2012 ENERO .MatutinoDocumento3 páginasETS 2012 ENERO .Matutinoduzter_jaguarAún no hay calificaciones

- Practica Fisica ViernesDocumento8 páginasPractica Fisica Viernesduzter_jaguarAún no hay calificaciones

- Concurrencia y ColinealidadDocumento25 páginasConcurrencia y Colinealidadduzter_jaguarAún no hay calificaciones

- Corriente ElectricaDocumento16 páginasCorriente Electrica'Lau WeistAún no hay calificaciones

- ECAR Estudio continuo audiencia radialDocumento11 páginasECAR Estudio continuo audiencia radialJosepArizaAún no hay calificaciones

- British Standards InstitutionDocumento4 páginasBritish Standards InstitutioneeqdAún no hay calificaciones

- Ver notas ERP sistema universitarioDocumento3 páginasVer notas ERP sistema universitarioJavier CuayylaAún no hay calificaciones

- Circuitos Digitales Configurables Parte 1 (Modo de Compatibilidad) PDFDocumento23 páginasCircuitos Digitales Configurables Parte 1 (Modo de Compatibilidad) PDFFrank VillaAún no hay calificaciones

- Excel Aplicado A La Física Por M.Espinoza Andaluz y V.Velasco GalarzaDocumento8 páginasExcel Aplicado A La Física Por M.Espinoza Andaluz y V.Velasco GalarzaVíctor Velasco GalarzaAún no hay calificaciones

- SGBD preguntas repaso fundamentosDocumento5 páginasSGBD preguntas repaso fundamentosEduardo Aranhil Juarez LunaAún no hay calificaciones

- (PDS) Cap - 08 - DFT - 17 - IDocumento51 páginas(PDS) Cap - 08 - DFT - 17 - Iandré ackermanAún no hay calificaciones

- Pensum Ingenieria ElectronicaDocumento4 páginasPensum Ingenieria ElectronicaMelissa AustinAún no hay calificaciones

- Manual Basico de Android PDFDocumento21 páginasManual Basico de Android PDFNelly VazquezAún no hay calificaciones

- Estructura Del Informe Final de Prácticas PreprofesionalesDocumento4 páginasEstructura Del Informe Final de Prácticas PreprofesionalesJerilynnSanchoAún no hay calificaciones

- Reporte de Conexión Usando OracleDocumento10 páginasReporte de Conexión Usando OracleJuan DiegoAún no hay calificaciones

- Excel Funciones Solucion UpnDocumento11 páginasExcel Funciones Solucion Upnprofesormiguel241Aún no hay calificaciones

- Zoom InformeDocumento15 páginasZoom InformeBilly Rivas LópezAún no hay calificaciones

- Guia Rapida PlaneacionDocumento27 páginasGuia Rapida PlaneacionHermes HernandezAún no hay calificaciones

- CCI-Mapa Ruta Ciber Seguridad Industrial en España 2013-2018 PDFDocumento54 páginasCCI-Mapa Ruta Ciber Seguridad Industrial en España 2013-2018 PDFRubén Ayala RodríguezAún no hay calificaciones

- Resumen OCA Primer ExamenDocumento66 páginasResumen OCA Primer ExamenagnaranjoAún no hay calificaciones

- Guía para Mini Proyectos Tecnológicos en Colegio San JoséDocumento2 páginasGuía para Mini Proyectos Tecnológicos en Colegio San Josémetegol100% (1)

- Formación docentes secundaria Piura Tumbes 2019Documento1 páginaFormación docentes secundaria Piura Tumbes 2019Fanny SanchezAún no hay calificaciones

- Analisis Al Aislante LiquidoDocumento6 páginasAnalisis Al Aislante LiquidoEdgardoJesusQuinteroAponteAún no hay calificaciones

- Gym-001 Control de LimpiezaDocumento1 páginaGym-001 Control de LimpiezaJulian andres sanchez polaniaAún no hay calificaciones

- Modelo de Servidores MúltiplesDocumento4 páginasModelo de Servidores Múltiplesjose enrique sanchezAún no hay calificaciones

- Guia No 3 C++Documento24 páginasGuia No 3 C++Last_Bastard0% (1)

- Punto FlotanteDocumento6 páginasPunto Flotantefacu_falaAún no hay calificaciones

- Administración de Bases de Datos Con SQL Server 2008 (Ejemplo)Documento41 páginasAdministración de Bases de Datos Con SQL Server 2008 (Ejemplo)Mariano AlmonteAún no hay calificaciones

- Funciones algebraicas y trascendentesDocumento14 páginasFunciones algebraicas y trascendentesAlfonso MedinaAún no hay calificaciones

- Sistemas DistribuidosDocumento12 páginasSistemas DistribuidosEvelyn Mazache Vera100% (2)

- AtlasClimatologicosBolivia - Final VER PAGINA 225Documento250 páginasAtlasClimatologicosBolivia - Final VER PAGINA 225tortolitosAún no hay calificaciones

- Control LEDs RGB con ArduinoDocumento13 páginasControl LEDs RGB con ArduinoGerman RodriguezAún no hay calificaciones

- S5. Actividad 2.análisis y Abstracción de InformaciónDocumento3 páginasS5. Actividad 2.análisis y Abstracción de InformaciónJudith ReyesAún no hay calificaciones

- Selección de Alternativas Mutuamente Excluyentes Utilizando Analisis Beneficio / CostoDocumento4 páginasSelección de Alternativas Mutuamente Excluyentes Utilizando Analisis Beneficio / CostoRey Cav TecAún no hay calificaciones