Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Familias Logicas.

Cargado por

Maried KubotaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Familias Logicas.

Cargado por

Maried KubotaCopyright:

Formatos disponibles

Captulo

Familias lgicas

Familias lgicas

Introduccin

Como respuesta a la pregunta dnde estn las puertas? te diremos que integradas en unos dispositivos fabricados con semiconductores que seguramente habrs visto cuando destapas un aparato electrnico; se llaman chips y tienen el aspecto de una cucaracha con muchas patitas. Y con las prcticas que te propondremos tendrs la oportunidad de manejarlos. Los vers identificados tambin como circuitos integrados. Los circuitos integrados digitales estn constituidos internamente por mltiples componentes: resistencias, diodos, transistores, etc. Las familias lgicas se caracterizan segn los elementos utilizados en su fabricacin .

Contenido

3.3. Familia TTL: Lgica transistor-transistor

3.3.1. Caractersticas de transistor bipolar 3.3.2. DTL lgica diodo-transistor 3.3.3. TTL lgica transistor-transistor

Objetivos

Al completar este captulo: u Sers capaz de diferenciar las familias lgicas por sus parmetros caractersticos. u Conocers las subfamilias ms utilizadas. u Diferenciars claramente los dispositivos CMOS y TTL. u Conocers en las prcticas los encapsulados y caractersticas de funcionamiento de circuitos integrados TTL y CMOS. u Comprobars experimentalmente el comportamiento de diversos circuitos integrados montando circuitos prcticos como una alarma por el tacto, un temporizador, un comprobador de bateras y otros.

3.4. Familia CMOS: Lgica con transistores MOS complementarios

3.4.1. Caracterstica del transistor unipolar 3.4.2. Elaboracin de puertas lgicas mediante CMOS

Familias lgicas

3.3 Familia TTL: Lgica transistortransistor

3.3.1 Caractersticas de transistor bipolar

El transistor bipolar es el formado por tres capas de material semiconductor. Ese material semiconductor puede ser tipo p y tipo n. Cuando se juntan ambas capas constituyen un diodo. Y si agregamos una capa ms tenemos un transistor. El transistor podr ser npn o pnp. Ambos son tiles para implementar puertas lgicas y nosotros utilizaremos el npn para nuestro cometido. En la siguiente figura podrs observar la simbologa de un transistor tipo npn (T) al cual se le han conectado dos resistencias que nos permiten polarizar el transistor a fin de obtener los resultados previstos; es decir, conseguir dos estados bien diferenciados que representen los niveles lgicos 1 y 0.

(a)

(b)

Transistor polarizado + grfica Ic _ Vce

Junto al esquema elctrico hay una grfica que parece un tanto compleja, pero vers, a poco de analizarla, que no slo no es compleja sino que adems nos har ver muy claramente el comportamiento de nuestro amigo... el transistor. El transistor ha sido creado, bsicamente, como dispositivo amplificador, a tal punto que la corriente Ic que entra por el colector (c) y sale por el emisor (e) hacia masa guarda la siguiente relacin respecto a la corriente Ib que entra por la base (b) y sale por el emisor hacia masa: Ic = x Ib donde es el factor de amplificacin (valor tpico = 100)

Pongamos valores prcticos al circuito del transistor. Por ejemplo: +Vcc = 5 V y Rc = 100 &. Vamos a suponer que conectamos la base del transistor a una fuente variable a travs de una resistencia limitadora Rb = 10 k. Para comprender la grfica vamos a calcular los siguientes parmetros que colocaremos en una tabla resumen: Ib = VA/Rb Ic = x Ib V0 = Vcc Ic x Rc

VA (v) 0,0 0,5 1,0 1,5 2,0 2,5 Ib (ma) 0,00 0,05 0,10 0,15 0,20 0,25 Ic (ma) 0 5 10 15 20 25 V0 (v) 5,0 4,5 4,0 3,5 3,0 2,5

Valores tericos para el circuito de la figura (a) anterior.

ITES-PARANINFO

Familias lgicas

VA (v) 3,0 3,5 4,0 4,5 5,0

Ib (ma) 0,30 0,35 0,40 0,45 0,50

Ic (ma) 30 35 40 45 50

V0 (v) 2,0 1,5 1,0 0,5 0,0

Valores tericos para el circuito de la figura (a) anterior.

Lo que hemos conseguido en la tabla es ni ms ni menos que algunos puntos de la recta que corta a ambas coordenadas. Las curvas que aparecen en la grfica corresponden a valores de corriente de base y responden a condiciones reales, por lo cual vemos que nunca llegaremos a tener una tensin nula entre colector y emisor (o sea V0). Volveremos sobre esta cuestin cundo veamos los mrgenes de tensin que determinan cundo un nivel lgico es 0 o 1. Para acabar esta cuestin diremos que el transistor est en corte cuando la tensin aplicada a su base es 0 V y en saturacin cuando aplicamos Vcc. En la tabla siguiente analizamos la conclusin a la que llegamos despus de la experiencia que acabamos de realizar. En la parte de la derecha de la tabla utilizamos la notacin 0 y 1, segn el nivel de tensin correspondiente.

VA 0V 5V V0 5V 0V entrada 0 1 salida 1 0

Tabla de Verdad del circuito mostrado en la figura (a) anterior.

A esta altura ya te habrs dado cuenta de que el circuito analizado es la puerta NOT, verdad? A fin de contar con una forma sencilla de analizar los circuitos que conforman las distintas familias lgicas, vamos a simplificar el funcionamiento del transistor asocindolo a un interruptor. Veamos:

El transistor en corte (interruptor abierto) y en saturacin (interruptor cerrado)

3.3.2 DTL lgica diodo-transistor

En la figura siguiente te presentamos una puerta NAND implementada con lgica DTL. Como ya sabes, un diodo se comporta como un interruptor cerrado si est directamente polarizado y como uno abierto si lo est inversamente. Vamos a analizar el funcionamiento de esta puerta para que entiendas cmo trabaja el transistor bipolar.

ITES-PARANINFO

Familias lgicas

Puerta NAND con DTL y su smbolo lgico

Anlisis del circuito: Cuando el voltaje aplicado en VA, VB o VC sea 0 V (nivel 0), el diodo correspondiente estar directamente polarizado puesto que el nodo est conectado a +Vcc a travs de la resistencia R1 y el ctodo estar a masa. Entonces actuar como un interruptor cerrado. Cuando el voltaje aplicado sea de +5 V (nivel 1), el diodo en cuestin, en principio, no estara ni directa ni inversamente polarizado ya que tendr aplicada en sus dos extremos (nodo y ctodo) la misma tensin. Pero ya hemos visto que debemos superar una tensin de aproximadamente 0,6 V para que el diodo conduzca corriente. Cuando en el punto X tengamos una tensin de masa (cuando alguna de las tensiones de entrada est a nivel 0), el transistor T estar cortado, y cuando tengamos una tensin suficiente alta, T estar saturado. Cuando todas las entradas estn a nivel 1 (+5 V), todos los diodos estn cortados, por lo que la base de T estar recibiendo corriente suministrada por la fuente a travs de R1 y los diodos Dd y De que estarn directamente polarizados. R1 est dimensionada de forma que la corriente recibida por T es suficiente para saturarlo. Con estas herramientas podrs verificar si en la tabla que tienes ms abajo no hemos metido la pata... T tienes la palabra.

Va 0V 0V 0V 0V +5V +5V Vb 0V 0V +5V Vc 0V Da cerrado Db cerrado cerrado abierto abierto cerrado cerrado abierto abierto Dc cerrado abierto cerrado abierto cerrado abierto cerrado abierto Vx 0,6V 0,6V 0,6V 0,6V 0,6V 0,6V 0,6V T abierto +5V abierto +5V abierto +5V abierto +5V abierto +5V abierto +5V abierto +5V V0 ABC 000 001 010 011 100 101 110 111 S 1 1 1 1 1 1 1 0

+5V cerrado 0V cerrado

+5V +5V cerrado 0V 0V 0V +5V 0V abierto abierto abierto abierto

+5V +5V +5V +5V +5V

> 1,8V cerrado 0,6V

Tabla para verificar el correcto funcionamiento del circuito anterior

ITES-PARANINFO

Familias lgicas

3.3.3 TTL lgica transistor-transistor

Sub-familias Estndar Baja potencia Alta velocidad Schottky Schottky baja potencia Schottky avanzada Schottky avanzada y baja potencia Rpida Designacin (*) 74 --74 L --74 H --74 S --74 LS --74 AS --74 ALS --74 F ---

Subfamilias de la familia TTL

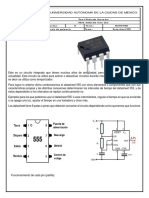

De todos los circuitos disponibles en TTL, nos centraremos en el anlisis de la tpica compuerta Nand con salida totem-pole.

3.3.3.1 TTL con salida totem-pole

En la figura siguiente podrs ver el circuito lgico tipo TTL con los valores tpicos de resistencia que corresponde a una NAND de tres entradas y presenta algunas diferencias respecto al tipo DTL analizado anteriormente. La configuracin de T3 y T4 es la que ha inspirado el nombre de totem-pole por la analoga con esos postes que los pieles rojas del oeste americano usaban para sus rituales. All solan atar a los prisioneros condenados a morir y que, en el ltimo segundo, eran salvados por el hroe de turno.

Circuito lgico NAND implementado con TTL y su smbolo lgico

Veamos la misin de los elementos que definen a esta familia: El transistor T1 tiene la particularidad de tener mltiples emisores. Cada uno de ellos equivale a un diodo tal como se usaba en el DTL. Y, adems, entre base y colector tenemos un diodo equivalente que cumple la funcin de Dd de la puerta DTL vista anteriormente. A continuacin te mostramos el circuito equivalente de T1 para aclarar lo que acabamos de describir. El transistor T2 viene a suministrar la corriente de saturacin de T4. Tenemos un transistor T3 que se encarga de suministrar la corriente de salida de la puerta cuando el nivel de salida es 1.

ITES-PARANINFO

Familias lgicas

Circuito equivalente al transistor T1

En las siguientes figuras podemos ver el comportamiento del circuito en el caso de que todas las entradas estn a 1 lgico (+5 V) y cuando alguna entrada est a nivel 0 (masa).

Funcionamiento de la puerta NAND cuando todas las entradas estn a nivel alto

Funcionamiento de la puerta NAND cuando alguna o algunas entradas estn a nivel bajo

ITES-PARANINFO

Familias lgicas

3.4 Familia CMOS: Lgica con transistores MOS complementarios

3.4.1. Caracterstica del transistor unipolar

Con posterioridad a la aparicin de los transistores bipolares se desarrollaron los unipolares, conocidos tambin como transistores tipo MOS (Metal-Oxido-Semiconductor). En funcin de las cargas que se mueven disponemos de transistores tipo NMOS y de transistores PMOS. En la siguiente figura podrs ver el smbolo de ambos. Cuando el funcionamiento se basa en el movimiento de cargas negativas el transistor se denomina NMOS y cuando son las cargas positivas las que se mueven, el transistor ser de tipo PMOS. De ah lo de su denominacin unipolar... Al igual que los transistores bipolares podemos controlar el flujo de corriente entre D y S aplicando las oportunas tensiones en la puerta G. Veamos, por ejemplo, cmo podramos implementar una puerta inversora mediante un transistor NMOS.

Si analizas la grfica VS = f (VA) podrs deducir que la salida VA se mantiene muy prximo al valor de tensin de fuente VDD (nivel lgico 1) cuando en la entrada aplicamos una tensin VA por debajo de VIL (prximo a la tensin de masa, o sea al nivel lgico 0). Por el contrario, cuando apliquemos una tensin VA que supere el valor VIH (muy prximo al valor de fuente VDD, o sea al nivel lgico 1) a la salida tendremos una tensin VS muy prxima a la tensin de masa, o sea al nivel lgico 0. De modo que podremos afirmar que: VS = VA A continuacin te mostramos la equivalencia del transistor MOS con un interruptor en funcin del nivel lgico aplicado a su puerta G (para ambos tipos de transistores).

ITES-PARANINFO

Familias lgicas

Debemos ser honestos contigo... en realidad estamos usando una simplificacin del smbolo de los transistores MOS. Su smbolo detallado es:

3.4.2. Elaboracin de puertas lgicas mediante CMOS Cuando en una puerta utilizamos un transistor tipo NMOS emparejado con uno

PMOS decimos que usamos transistores CMOS para indicar que son complementarios. Te proponemos analizar juntos el funcionamiento de la puerta NOR que se muestra en la Figura 3.5 del libro. A continuacin podrs ver como queda dicho circuito cuando reemplazamos cada transistor por un interruptor abierto o cerrado segn sean los niveles lgicos de entrada.

Estado de los transistores CMOS segn el nivel lgico de las entradas.

ITES-PARANINFO

También podría gustarte

- Laboratorio DigitalesDocumento15 páginasLaboratorio DigitalesPalmer DionicioAún no hay calificaciones

- 100 Circuitos de Proyectos EducacionalesDe Everand100 Circuitos de Proyectos EducacionalesCalificación: 5 de 5 estrellas5/5 (2)

- Análisis de circuito combinacional implementado con compuertas lógicasDocumento11 páginasAnálisis de circuito combinacional implementado con compuertas lógicaswilmer2528Aún no hay calificaciones

- Compuertas LogicasDocumento21 páginasCompuertas Logicasfer6669993Aún no hay calificaciones

- Sonda lógica 555: Construye un probador lógico TTL y CMOS sin osciloscopioDocumento2 páginasSonda lógica 555: Construye un probador lógico TTL y CMOS sin osciloscopioFernando EscobaresAún no hay calificaciones

- Práctica 2Documento6 páginasPráctica 2Julio UrzuaAún no hay calificaciones

- Familia DTLDocumento3 páginasFamilia DTLHenry LazoAún no hay calificaciones

- Tecnología TTL: Características y circuitos equivalentesDocumento6 páginasTecnología TTL: Características y circuitos equivalentesMarioAún no hay calificaciones

- Practica 2 DigitalDocumento5 páginasPractica 2 DigitalEddu BPAún no hay calificaciones

- Sol Lab 1Documento22 páginasSol Lab 1Michael PomaAún no hay calificaciones

- Entrenador DigitalDocumento16 páginasEntrenador DigitalJeisson Andres Cortes0% (1)

- Circuito LógicoDocumento26 páginasCircuito LógicotjsuniagaAún no hay calificaciones

- CuestionarioDocumento4 páginasCuestionarioRoky RbrAún no hay calificaciones

- Informe 3Documento13 páginasInforme 3luiGAún no hay calificaciones

- TTL y IILDocumento7 páginasTTL y IILAlan Pulido MusleraAún no hay calificaciones

- Familias Logicas TTL y CMOSDocumento8 páginasFamilias Logicas TTL y CMOSDaniel DzulAún no hay calificaciones

- Familas TTL y CmosDocumento20 páginasFamilas TTL y CmosXavi Mak100% (1)

- 12312312Documento7 páginas12312312Jorge AntonioAún no hay calificaciones

- Compuertas Logicas Laboratorio 1Documento9 páginasCompuertas Logicas Laboratorio 1Cristian GomezAún no hay calificaciones

- SaudiMartinez - Investigación 1Documento19 páginasSaudiMartinez - Investigación 1Saudi MartinezAún no hay calificaciones

- Informe 2 Aplicacion de TransistoresDocumento8 páginasInforme 2 Aplicacion de TransistoresFrank sanchezAún no hay calificaciones

- Tema7 FamLogicasDocumento15 páginasTema7 FamLogicasgeorgejr11Aún no hay calificaciones

- Miguel ValecillosDocumento13 páginasMiguel Valecillosjahv_2000Aún no hay calificaciones

- Control de Banda Transportadora - ClasificadorDocumento4 páginasControl de Banda Transportadora - ClasificadorWalter Quispe100% (1)

- Familias Lógicas TTL, DTL e I2LDocumento6 páginasFamilias Lógicas TTL, DTL e I2LFaby Lopez RezaAún no hay calificaciones

- 2da. Biom - Operadores Logicos Con Circuitos TTLDocumento9 páginas2da. Biom - Operadores Logicos Con Circuitos TTLCabrejo Oré MickyAún no hay calificaciones

- Práctica 10 - Protoboard - Transistor1Documento10 páginasPráctica 10 - Protoboard - Transistor1robyn100Aún no hay calificaciones

- Taller 4 - Conceptos de Lógica CMOS, TTL y Circuitos Lógicos CombinacionalesDocumento21 páginasTaller 4 - Conceptos de Lógica CMOS, TTL y Circuitos Lógicos CombinacionalesSebastian Guarnizo PerdomoAún no hay calificaciones

- Practica Ieesl MosfetDocumento7 páginasPractica Ieesl Mosfetenmanuel batista jiménezAún no hay calificaciones

- Inici PortesDocumento16 páginasInici PortesXavier Guillaumet MarquésAún no hay calificaciones

- Practica CompuertasDocumento5 páginasPractica CompuertasMiguel GonzálezAún no hay calificaciones

- Circuitos lógicos AND, OR, XOR y aplicación de votaciónDocumento5 páginasCircuitos lógicos AND, OR, XOR y aplicación de votaciónSaraAún no hay calificaciones

- 2.1 Practica 2Documento9 páginas2.1 Practica 2Sinai SanchezAún no hay calificaciones

- Practica 7Documento9 páginasPractica 7Darwin RamosAún no hay calificaciones

- Tarea 1 Timer 555 Ó Datasheet 555 PDFDocumento15 páginasTarea 1 Timer 555 Ó Datasheet 555 PDFjhonatanAún no hay calificaciones

- Práctica 10 y 11 - Brigada 6Documento12 páginasPráctica 10 y 11 - Brigada 6julia gabriela hernandez nievesAún no hay calificaciones

- Punta Lógica TTL de Tres EstadosDocumento8 páginasPunta Lógica TTL de Tres EstadosMiguel Lop100% (1)

- Guia Practica 1 2024Documento8 páginasGuia Practica 1 2024Marcelo Azpilcueta RubinaAún no hay calificaciones

- ReporteDocumento21 páginasReporteSamanta MRSAún no hay calificaciones

- GUÍA DE ELECTRÓNICA DIGITAL Resuelta 2Documento20 páginasGUÍA DE ELECTRÓNICA DIGITAL Resuelta 2Melissa Santillán SalazarAún no hay calificaciones

- Multivibradores CD4541 y CD4047Documento14 páginasMultivibradores CD4541 y CD4047tutesamAún no hay calificaciones

- VlsiDocumento10 páginasVlsiOscar RodriguezAún no hay calificaciones

- Tecnicas DigitalesDocumento25 páginasTecnicas DigitalesHector VallejosAún no hay calificaciones

- Nociones IntroductoriasDocumento8 páginasNociones IntroductoriasJosé CoronaAún no hay calificaciones

- DossierDocumento77 páginasDossierBryan AguilarAún no hay calificaciones

- Familias LogicasDocumento23 páginasFamilias LogicasisaiAún no hay calificaciones

- Compuertas LógicasDocumento14 páginasCompuertas LógicasAchicAún no hay calificaciones

- Característica de Transferencia de Una Compuerta TTL NANDDocumento7 páginasCaracterística de Transferencia de Una Compuerta TTL NANDGabriel MartínezAún no hay calificaciones

- Familia Logica TTL-ResumenDocumento4 páginasFamilia Logica TTL-Resumenpepeluis666Aún no hay calificaciones

- Familias LógicasDocumento12 páginasFamilias LógicasJair Tamayo Gtz100% (1)

- Funcionalidad de Las DTLDocumento7 páginasFuncionalidad de Las DTLMargot BautistaAún no hay calificaciones

- Kedi U1 A1 EdpjDocumento7 páginasKedi U1 A1 EdpjJosé LuisAún no hay calificaciones

- Punta Logica de Prueba InformeDocumento17 páginasPunta Logica de Prueba InformeAngel OrtizAún no hay calificaciones

- Informe #1 de Laboratorio de Circuitos DigitalesDocumento14 páginasInforme #1 de Laboratorio de Circuitos DigitalesCarlos RodriguezAún no hay calificaciones

- Sesion 02 - Familias LogicasDocumento36 páginasSesion 02 - Familias LogicasWilliam Yoel CcalloAún no hay calificaciones

- Proyecto 3 (TTL)Documento4 páginasProyecto 3 (TTL)Rodrigo QuintanillaAún no hay calificaciones

- Compuertas AND y OR Con DiodosDocumento5 páginasCompuertas AND y OR Con DiodosLalo OlivosAún no hay calificaciones

- Introducción Al Diseño EléctricoDocumento1 páginaIntroducción Al Diseño EléctricoMaried KubotaAún no hay calificaciones

- Tres Generaciones de RoversDocumento1 páginaTres Generaciones de RoversMaried KubotaAún no hay calificaciones

- Problemas de BloqueoDocumento1 páginaProblemas de BloqueoMaried KubotaAún no hay calificaciones

- ReleDocumento27 páginasReleMaried Kubota0% (1)

- Transformada Laplace Diferenciales Ejercicios PropuestosDocumento4 páginasTransformada Laplace Diferenciales Ejercicios PropuestosMaried KubotaAún no hay calificaciones

- Manual Procedimientos AcademicosDocumento43 páginasManual Procedimientos AcademicosMaried KubotaAún no hay calificaciones

- CUADRIPOLOS Marzo 2010Documento40 páginasCUADRIPOLOS Marzo 2010Maried KubotaAún no hay calificaciones

- 31VDocumento11 páginas31VMaried KubotaAún no hay calificaciones

- Conta Antología Sistemas de Infromación IIIDocumento64 páginasConta Antología Sistemas de Infromación IIIAlberto AguilarAún no hay calificaciones

- Ej 10 Equivalencias Logicas UnahurDocumento3 páginasEj 10 Equivalencias Logicas UnahurJavier MenderAún no hay calificaciones

- Tarea 7 y 8 de Procesos Cognitivos.Documento12 páginasTarea 7 y 8 de Procesos Cognitivos.Juneiri RodríguezAún no hay calificaciones

- Logica Tema 10, 11 y 12Documento5 páginasLogica Tema 10, 11 y 12Pedro GutierrezAún no hay calificaciones

- 7 Entrevista A Andres JaumeDocumento4 páginas7 Entrevista A Andres JaumeRedimi21 Películas.SeriesAún no hay calificaciones

- Gadamer - Qué Es La Verdad (1957)Documento8 páginasGadamer - Qué Es La Verdad (1957)Elizabeth McdonaldAún no hay calificaciones

- Rosa NassifDocumento32 páginasRosa Nassifgramatologia100% (1)

- Resume NDocumento1 páginaResume NErick LemusAún no hay calificaciones

- Ejercicios de Deducción NaturalDocumento3 páginasEjercicios de Deducción NaturalMarta gutiérrezAún no hay calificaciones

- Demostraciones de ConjuntosDocumento7 páginasDemostraciones de ConjuntosLeandro HristovAún no hay calificaciones

- Corrientes Del Pensamiento Filosófico2Documento12 páginasCorrientes Del Pensamiento Filosófico2Fran JarmaAún no hay calificaciones

- Ricardo DiCesare Control3Documento6 páginasRicardo DiCesare Control3Ricardo Di CesareAún no hay calificaciones

- Conocimiento HessenDocumento19 páginasConocimiento HessenAdacelsaAún no hay calificaciones

- Ayudantia 1 Logica Proposicional Mate 1 FAE 1s 2019 JC 346873Documento2 páginasAyudantia 1 Logica Proposicional Mate 1 FAE 1s 2019 JC 346873Sebastian GonzalezAún no hay calificaciones

- Matemática: Ecuaciones y funcionesDocumento10 páginasMatemática: Ecuaciones y funcionesJuan Luis Llanos Aedo JLAún no hay calificaciones

- Tesis Maestria2020 DWRJDocumento183 páginasTesis Maestria2020 DWRJRobertoAvilaVázquezAún no hay calificaciones

- Circuito protección incendios compuertas lógicasDocumento19 páginasCircuito protección incendios compuertas lógicascarlos leonAún no hay calificaciones

- Marti Sánchez Gramática en La ActualidadDocumento29 páginasMarti Sánchez Gramática en La ActualidadMarcos RaballAún no hay calificaciones

- Reglas de InferenciaDocumento7 páginasReglas de InferenciaJuan DiegoAún no hay calificaciones

- Chalmers - ¿Qué Es Esa Cosa Es Esa Cosa Llamada Ciencia? ResumenDocumento5 páginasChalmers - ¿Qué Es Esa Cosa Es Esa Cosa Llamada Ciencia? Resumenluishb78100% (1)

- Proposiciones LogicasDocumento20 páginasProposiciones LogicasChristian PariAún no hay calificaciones

- Ecuaciones Diferenciales (1-7)Documento23 páginasEcuaciones Diferenciales (1-7)Cristhian Raul Rodriguez Sucapuca100% (1)

- Pragmática LingüísticaDocumento31 páginasPragmática LingüísticaigorytooAún no hay calificaciones

- I. Kant - Crítica de La Razón Pura. Guía de Lectura #4. Analítica de Los ConceptosDocumento2 páginasI. Kant - Crítica de La Razón Pura. Guía de Lectura #4. Analítica de Los ConceptosIvánAún no hay calificaciones

- Metodo de La Investigacion Cientifica Monografia PDFDocumento37 páginasMetodo de La Investigacion Cientifica Monografia PDFJaneo Pérez GutiérrezAún no hay calificaciones

- Algebra de Boole y Mapas de KarnaughDocumento27 páginasAlgebra de Boole y Mapas de KarnaughDC AlbinAún no hay calificaciones

- Heurística y producción de conocimiento nuevo en la CTSDocumento25 páginasHeurística y producción de conocimiento nuevo en la CTSAdrianGalindoAún no hay calificaciones

- Guía Diario Reflexivo Unidades 5 y 6Documento4 páginasGuía Diario Reflexivo Unidades 5 y 6AndreaAún no hay calificaciones

- Chavarin Bryan Tarea 5Documento3 páginasChavarin Bryan Tarea 5Bryan Chavarin EscobedoAún no hay calificaciones

- Ejercicios de SilogismosDocumento3 páginasEjercicios de SilogismosValeria Narváez QuantAún no hay calificaciones