Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Procesadores - Syllabus

Cargado por

Gerard MesaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Procesadores - Syllabus

Cargado por

Gerard MesaCopyright:

Formatos disponibles

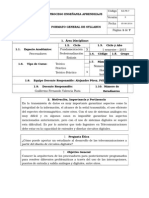

PROCESO ENSEANZA APRENDIZAJE

FORMATO GENERAL DE SYLLABUS

Cdigo

EA-FR-7

Versin

Fecha

05-08-2014

Pgina 1 de 7

1. rea Disciplinar:

1.1.

Espacio Acadmico:

1.2. Ciclo

Fundamentacin

Procesadores

Profesionalizacin

1.3.

X

Ciclo y Ao

1.4.

1 semestre 2015

Cdigo

1.5. Grupo

1.7.

Nmero de Crditos

nfasis

1.6.

Tipo de Curso:

Terico

Prctico

Terico-Prctico

1.8.

Nmero de Horas Aula

x

Horas Trabajo

Independiente

Equipo Docente Responsable: Alejandro Prez, Flix Gmez Devia

1.9.

Docente Responsable:

Guillermo Fernando Valencia Plata

1.10. Nmero de

Estudiantes

2. Motivacin, Importancia y Pertinencia

En la transmisin de datos es muy importante garantizar aspectos como la

integridad de la informacin, el alcance de la seal transmitida, el uso eficiente

del espectro electromagntico, entre otros. Con el uso de sistemas anlogos era

muy difcil y en algunos casos es imposible garantizar los aspectos

mencionados anteriormente, pero con el uso de sistemas digitales se super

esta dificultad. Es por lo anterior que todo Ingeniero en Telecomunicaciones

debe estar en la capacidad de entender y disear circuitos digitales.

1. Pregunta tica

Cmo puede aportar un estudiante al desarrollo de las telecomunicaciones a

partir del diseo de circuitos digitales?

2. Objetivo General

Conocer la arquitectura de los procesadores para posteriormente programarlos

para resolver diferentes problemticas a travs del uso de las interrupciones,

puertos de entrada y salida anlogos y digitales, entre otros.

3

5

4

PROCESO ENSEANZA APRENDIZAJE

EA-FR-7

Versin

Fecha

FORMATO GENERAL DE SYLLABUS

2.1.

Cdigo

05-08-2014

Pgina 2 de 7

Objetivos Especficos

Conocer el lenguaje assembler.

Reconocer la arquitectura de un procesador.

Diferenciar los diferentes tipos de puertos que tiene un procesador.

Implementar circuitos digitales.

3. Competencias del Programa

3.1.

3.2. Nivel de

Desempe

o

Competencia

Indagacin y modelacin

Alto

3.3. Indicadores de

Competencia

Capacidad

para

resolver

problemas

usando

micro

procesadores.

Capacidad para disear un

Diseo de sistemas

Alto

circuito digital dependiendo de

sus entradas y salidas.

Capacidad

Comunicarse en forma efectiva en el

vocabulario profesional e idiomas

Medio

pertinentes

de

comunicarse

usando los nombres de los

diferentes

dispositivos

digitales.

4. Planeador de metodologa de Aprendizaje por Contenido

4.1.

Contenidos

Temticos

Lenguaje de descripcin de

hardware para circuitos

integrados de muy alta

velocidad (VHDL)

Lgica de

transferencia entra

registros.

4.2.

Estrategias

pedaggica

s

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

Trabajo independiente

4.3. De

preparacin

Lecturas,

exposiciones,

talleres guiados y

laboratorios

guiados.

Lecturas,

exposiciones,

talleres guiados y

laboratorios

guiados.

4.4. De

resultado

s

Comprensin y

aprehensin de los

temas abordados

Comprensin y

aprehensin de los

temas abordados

PROCESO ENSEANZA APRENDIZAJE

Cdigo

EA-FR-7

Versin

Fecha

FORMATO GENERAL DE SYLLABUS

05-08-2014

Pgina 3 de 7

4. Planeador de metodologa de Aprendizaje por Contenido

4.1.

Contenidos

Temticos

4.2.

Lenguajes de

mquina de

procesadores.

Arquitectura

procesador.

de

un

Interfaces

Interrupciones

Estrategias

pedaggica

s

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

Ctedra magistral del

profesor con la

participacin efectiva

y permanente de los

estudiantes.

5. Unidad

5.1.

Comprensin y

aprehensin de los

temas abordados

Comprensin y

aprehensin de los

temas abordados

Comprensin y

aprehensin de los

temas abordados

Comprensin y

aprehensin de los

temas abordados

5.2.

del

Tema

docente

los

estudiantes, presentacin del programa por

de una arquitectura en VHDL. Tipos y

Libreras y paquetes.

Elementos de diseo estructural, de flujo de

datos, basados en el comportamiento. La

dimensin tiempo y simulacin. Sntesis.

velocidad (VHDL).

Lgica de transferencia

de

constantes. Funciones y procedimientos.

Lenguaje de descripcin de

integrados de muy alta

Especificaciones y sintaxis de una entidad y

2

velocidad (VHDL).

hardware para circuitos

4.4. De

resultado

s

parte del docente, repaso general.

Flujo de diseo. Estructura del programa.

Lenguaje de descripcin de

integrados de muy alta

Lecturas,

exposiciones,

talleres guiados

laboratorios

guiados.

Lecturas,

exposiciones,

talleres guiados

laboratorios

guiados.

Lecturas,

exposiciones,

talleres guiados

laboratorios

guiados.

Lecturas,

exposiciones,

talleres guiados

laboratorios

guiados.

Presentacin

anteriores.

hardware para circuitos

4.3. De

preparacin

Sema

na

Introduccin al curso y repaso

de temas vistos en cursos

Trabajo independiente

Transferencia entre registros. Micro

PROCESO ENSEANZA APRENDIZAJE

FORMATO GENERAL DE SYLLABUS

5. Unidad

5.1.

Sema

na

5.2.

Cdigo

EA-FR-7

Versin

Fecha

05-08-2014

Pgina 4 de 7

Tema

operaciones aritmticas lgicas y de

entra registros.

desplazamiento. Proposiciones condicionales

de control.

Primer Corte

Evaluacin de los temas abordados

Datos binarios de punto fijo y punto

Lgica de transferencia

entra registros.

Lenguajes de mquina

de procesadores.

Lenguajes de mquina

de procesadores.

Arquitectura de un

procesador.

flotante, sobrecapacidad, desplazamientos

aritmticos. Cdigos de instruccin. Diseo

de un procesador de datos sencillo.

Cdigos de operacin y de instruccin.

Creacin de las instrucciones para

movimientos de datos.

Creacin de las instrucciones aritmticolgicas.

Creacin de las instrucciones de salto

incondicional y de parada.

Creacin de las instrucciones de salto

condicional. Formatos de instrucciones y

creacin de arquitecturas para ejecucin de

ramificaciones condicionales. Creacin de

las instrucciones de llamado a subrutina y

anidamientos de subrutinas.

Diagrama de bloques de un procesador:

procesador de operandos, procesador de

instrucciones y procesador de direcciones.

Caractersticas de las arquitecturas Harvard

y Von-Neumann.

Camino de datos de un procesador:

diagrama de bloques de un computador y de

un procesador, unidad de control, camino

de datos, transferencia entre registros y

microoperaciones.

Segundo Corte

10

Evaluacin de los temas abordados

Arquitectura de un

procesador.

11

Unidad de control discreta: organizacin de

la unidad de control, entradas y salidas de

control, ejemplos de diseo. Unidad de

control microprogramada: organizacin de la

unidad de control microprogramada, control

con mltiples ciclos. Conjunto de

instrucciones de un procesador: operandos,

modos de direccionamiento, instrucciones

aritmticas, lgicas y de desplazamiento,

saltos, interrupciones, aritmtica de punto

PROCESO ENSEANZA APRENDIZAJE

FORMATO GENERAL DE SYLLABUS

5. Unidad

5.1.

Sema

na

Interfaces

12

Interfaces

13

Interrupciones

14

Interrupciones

15

Tercer corte

16

5.2.

Cdigo

EA-FR-7

Versin

Fecha

Pgina 5 de 7

Tema

flotante.

Interfaces de entrada

Interfaces de salida

Interfaces bidireccionales

Interfaces programables

Jerarquizacin de interrupciones.

Interrupciones no enmascarables y

enmascarables. Generacin de

interrupciones desde interfaces.

Activaciones por interrupciones externas.

Activaciones por interrupciones internas:

desbordamiento de los temporizadores,

finalizacin de la escritura de memoria

interna, reset, etc

Evaluacin de los temas abordados

6. Evaluacin

6.1.

Corte

6.2.

Evaluaci

n

Primer corte

Actividades

de

evaluacin

Pruebas escritas

Prcticas de laboratorio

05-08-2014

6.3.

Parmetros de

evaluacin

Se aplicarn talleres

grupales en clase en los

que el estudiante podr

identificar,

resolver

formular

problemas

y

de

comunicaciones digitales,

con base en los conceptos

adquiridos.

Se realizar evaluacin

continua

determinar

fin

si

de

el

estudiante

ha

desarrollado

las

competencias propias del

curso.

Metodologa:

Autoevaluacin,

Coevaluacin,

6.4. Valor

porcentual

30%

PROCESO ENSEANZA APRENDIZAJE

FORMATO GENERAL DE SYLLABUS

Cdigo

EA-FR-7

Versin

Fecha

Pgina 6 de 7

6. Evaluacin

6.1.

Corte

6.2.

Evaluaci

n

Segundo corte

Actividades

de

evaluacin

6.3.

Parmetros de

evaluacin

Pruebas escritas

Heteroevaluacin

Se aplicarn talleres

Prcticas de laboratorio

grupales en clase en los

6.4. Valor

porcentual

30%

que el estudiante podr

identificar,

resolver

formular

problemas

y

de

comunicaciones digitales,

con base en los conceptos

adquiridos.

Se realizar evaluacin

continua

determinar

fin

si

de

el

estudiante

ha

desarrollado

las

competencias propias del

curso.

Metodologa:

Autoevaluacin,

Coevaluacin,

Tercer corte

Pruebas escritas

Heteroevaluacin

Se aplicarn talleres

Prcticas de laboratorio

grupales en clase en los

Proyecto

que el estudiante podr

identificar,

resolver

formular

problemas

y

de

comunicaciones digitales,

con base en los conceptos

adquiridos.

Se realizar evaluacin

continua

determinar

fin

si

de

el

estudiante

ha

desarrollado

las

competencias propias del

curso.

05-08-2014

40%

PROCESO ENSEANZA APRENDIZAJE

FORMATO GENERAL DE SYLLABUS

Cdigo

EA-FR-7

Versin

Fecha

Pgina 7 de 7

6. Evaluacin

6.1.

Corte

6.2.

Evaluaci

n

Actividades

de

evaluacin

6.3.

Parmetros de

evaluacin

6.4. Valor

porcentual

Metodologa:

Autoevaluacin,

Coevaluacin,

Heteroevaluacin

7. Fuentes de Informacin (Digitales o Impresos)

Sistemas digitales: principios y aplicaciones/ Ronald J. Tocci, Neal S.

Widmer, Gregory L. Moss; Tr. Alfonso Vidal Romero Elizondo, Rev tc.

Reynaldo Flix Acua.

Fundamentos de micro procesadores. Roger L. Tokheim. Mc Graw

Hill.

7.1.

Direcciones de Internet

8. E-mail

guillermo.valenciap@uniagustiniana.e

du.co

8.1.

3203368110

8.2.

Estudios de pregrado: Ingeniera Electrnica

8.3.

Estudios de postgrado:

Maestra en Telecomunicaciones

Telfono

05-08-2014

También podría gustarte

- PASTEURIZACIONDocumento17 páginasPASTEURIZACIONGerard MesaAún no hay calificaciones

- Lenguaje de Programación ArduinoDocumento51 páginasLenguaje de Programación ArduinoRodolfo Víctor Hilario Poma100% (2)

- Procesadores - SyllabusDocumento7 páginasProcesadores - SyllabusGerard MesaAún no hay calificaciones

- Clasificación de Las SeñalesDocumento3 páginasClasificación de Las SeñalesGerard Mesa0% (1)

- Caracteristicas Generales de Los Granos de CerealesDocumento12 páginasCaracteristicas Generales de Los Granos de CerealesGerard MesaAún no hay calificaciones

- Clasificación de Las SeñalesDocumento3 páginasClasificación de Las SeñalesGerard Mesa0% (1)

- 100 Ejercicios LinuxDocumento6 páginas100 Ejercicios LinuxIvan VienenAún no hay calificaciones

- Doing Business in Colombia - En.esDocumento59 páginasDoing Business in Colombia - En.esGerard MesaAún no hay calificaciones

- Tema 1 Part 2 Metodes Numerics-4722 PDFDocumento30 páginasTema 1 Part 2 Metodes Numerics-4722 PDFJose Pablo Castro RuizAún no hay calificaciones

- Configuración de DHCPDocumento7 páginasConfiguración de DHCPGerard MesaAún no hay calificaciones

- Apuntes de Diseño de Circuitos Integrados 1Documento352 páginasApuntes de Diseño de Circuitos Integrados 1Nemoz ZrAún no hay calificaciones

- Amplificador DiferencialDocumento3 páginasAmplificador DiferencialGerard Mesa100% (1)

- 9999 PNNRDocumento0 páginas9999 PNNRGerard MesaAún no hay calificaciones

- BECERRIL ESPINOSA JOSE VENTURA Ecuaciones Diferenciales Tecnicas de Solucion y AplicacionesDocumento252 páginasBECERRIL ESPINOSA JOSE VENTURA Ecuaciones Diferenciales Tecnicas de Solucion y AplicacionesMGDArmas33% (3)

- Manual ASPDocumento40 páginasManual ASPGerard MesaAún no hay calificaciones

- Etapas de La Licitacion Publica en ColombiaDocumento2 páginasEtapas de La Licitacion Publica en ColombiaGerard Mesa100% (1)

- Tabla)Documento2 páginasTabla)Gerard MesaAún no hay calificaciones

- Mantenimiento Pro ExpoDocumento23 páginasMantenimiento Pro Expomiguel carrascoAún no hay calificaciones

- Actividad Valor Posiconal N°1Documento4 páginasActividad Valor Posiconal N°1Ayleen Francisca Valdivia MaldonadoAún no hay calificaciones

- Inspección de Ensambles Electrónicos Norma A-610 - Nivel I - Agosto 2015Documento52 páginasInspección de Ensambles Electrónicos Norma A-610 - Nivel I - Agosto 2015TDFRIOGRANDEAún no hay calificaciones

- Cargador Baterías 18650Documento15 páginasCargador Baterías 18650carnesdehesaAún no hay calificaciones

- Bsi g03 Es-1Documento8 páginasBsi g03 Es-1Javier InzaurgaratAún no hay calificaciones

- Lista de Útiles Escolares Primer Grado 2022Documento1 páginaLista de Útiles Escolares Primer Grado 2022Jose Quispe67% (3)

- Qué Son Los Circuitos en Serie y Circuitos en ParaleloDocumento2 páginasQué Son Los Circuitos en Serie y Circuitos en Paraleloclugo78Aún no hay calificaciones

- Taller CondicionalesDocumento2 páginasTaller CondicionalesLIZ DAYANA ROJAS CORTESAún no hay calificaciones

- 16 4 PA - FyQ - 3ESODocumento117 páginas16 4 PA - FyQ - 3ESOFelicitas MassaAún no hay calificaciones

- Informe MultiplexadoDocumento12 páginasInforme MultiplexadoJJ Ochoa AlvarezAún no hay calificaciones

- LG 32lf510b Manual de UsuarioDocumento50 páginasLG 32lf510b Manual de Usuariolucho1967Aún no hay calificaciones

- Dixell España XR75CX RTC SP r1 A 15 02 2011Documento6 páginasDixell España XR75CX RTC SP r1 A 15 02 2011Carlos RiveroAún no hay calificaciones

- Distintos Tipos de CámarasDocumento8 páginasDistintos Tipos de CámarasNahuel VilaAún no hay calificaciones

- Decisiones Comerciales en ZaraDocumento5 páginasDecisiones Comerciales en ZaraYerty Reyes LuceroAún no hay calificaciones

- T2 - Seguridad y Salud OcupacionalDocumento12 páginasT2 - Seguridad y Salud OcupacionalMüller Andre Benites SolorzanoAún no hay calificaciones

- Ficha 2Documento45 páginasFicha 2JoseKaztilloAún no hay calificaciones

- Comandos Basicos para La Configuración Del ROUTERDocumento4 páginasComandos Basicos para La Configuración Del ROUTERjesus danielAún no hay calificaciones

- Unidad 1 Introducción A La Gestión de ProyectosDocumento6 páginasUnidad 1 Introducción A La Gestión de ProyectosPablo AlegríaAún no hay calificaciones

- Diseño e Implementación de Una Aplicación Web para El Monitoreo de Egresados de Ingeniería de Sis PDFDocumento200 páginasDiseño e Implementación de Una Aplicación Web para El Monitoreo de Egresados de Ingeniería de Sis PDFluisrincon782165Aún no hay calificaciones

- Jeep WranglerDocumento370 páginasJeep WranglerPablo Daniel Jacamo Shmeisser0% (1)

- Talleres de Java NetbeansDocumento3 páginasTalleres de Java NetbeansLynn HerreñoAún no hay calificaciones

- Influencia de La Tecnología en La EducaciónDocumento15 páginasInfluencia de La Tecnología en La EducaciónDiana Gomez ArbelaezAún no hay calificaciones

- Actividad S9 Permisos en Linux PDFDocumento7 páginasActividad S9 Permisos en Linux PDFyefersondiazAún no hay calificaciones

- Introducción en Excel Con MACROSDocumento37 páginasIntroducción en Excel Con MACROSManrique FredAún no hay calificaciones

- Adquisicion Del ConocimientoDocumento34 páginasAdquisicion Del ConocimientoCassan HecAún no hay calificaciones

- Guia de Instalación y Prácticas para El ESP32Documento9 páginasGuia de Instalación y Prácticas para El ESP32Xa SierraAún no hay calificaciones

- Ambiente de Medicion de Los Registros Electricos deDocumento146 páginasAmbiente de Medicion de Los Registros Electricos deJose FernandezAún no hay calificaciones

- Guia 1 Manejo Protoboard - EletricidadDocumento12 páginasGuia 1 Manejo Protoboard - EletricidadRom Kno San100% (2)

- DS 25233Documento12 páginasDS 25233L Abdón ArceAún no hay calificaciones

- Modelo de Referencia OSIDocumento7 páginasModelo de Referencia OSIDeleresiSanIsidroAún no hay calificaciones