Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Digitales Capitulo 3

Digitales Capitulo 3

Cargado por

Angel Adrian Ayala LopezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Digitales Capitulo 3

Digitales Capitulo 3

Cargado por

Angel Adrian Ayala LopezCopyright:

Formatos disponibles

Captulo 3: Lenguaje de

Descripcin del Hardware (VHDL)

SISTEMAS DIGITALES I

HDL: Lenguaje de Descripcin

del Hardware

Similar a un lenguaje de computadora excepto que un

HDL describe Hardware que luego de simulado puede ser

construido.

Existen 2 HDL que son estndares IEEE: VHDL (Very High

Speed Integrated Circuit Hardware Description Lenguage)

y Verilog HDL.

Speed Integrated Circuit Hardware Description Lenguage)

y Verilog HDL.

El VHDL es ms popular pero ambos se usan a nivel

industrial.

Inicio en 1980 en el Departamento de Defensa (DoD).

Luego en 1983 formalmente empezaron el proyecto VHDL

con: Intermetrics, Texas Instruments e IBM.

IEEE empez la estandarizacin en 1984 que luego se

aprob en 1987 con el nmero 1076.

En 1994 el IEEE public la revisin del estandar IEEE Std

1076-1993 que es la que se encuentra vigente.

VHDL

Trabaja con diseo jerrquico: top down o down - top.

Independencia tecnolgica que permite disear circuitos

cuya descripcin no depende de la forma de

implementacin fsica posterior.

Universalidad, es decir compatibilidad con un gran Universalidad, es decir compatibilidad con un gran

nmero de herramientas CAD.

Diferentes tipos de Descripciones: Sistema, algortmico,

RTL, Lgico, Conmutacin, Elctrico, Fsico.

Caractersticas: Se declara una caja negra (entity) con

un identificador para el circuito, y sus terminales de

entrada y salida. Tambin se declaran las direcciones de

los terminales (in, out) y el tipo de datos que admiten.

Luego se describe el circuito en s dentro del cuerpo de

una arquitectura. Esta descripcin difiere segn el nivel.

Estructura de un programa en

VHDL

Cuando se utiliza VHDL, un sistema digital se divide en varios bloques para

efectuar el proceso lo ms comprensible y que sea fcil de probar y de dar

mantenimiento. En VHDL, cada porcin del diseo es considerado un

bloque, que es descrito en el lenguaje, mediante una entidad y una

arquitectura. arquitectura.

La entidad me describe el exterior de mi circuito y la arquitectura su

comportamiento interno.

Bloque 1

Bloque 3 Bloque 2

Bloque 4

arquitectura 1

Arquitectura 3 arquitectura 2

arquitectura 4

entidad 1

entidad 2 entidad 3

entidad 4

Ejemplo de entidad y arquitectura

ENTITY nand2 IS

PORT(I1,I2: IN BIT;

O : OUT BIT);

END nand2;

I2

O

I1

END nand2;

ARCHITECTURE C1 OF nand2 IS

BEGIN

O<=NOT(I1 AND I2);

END C1;

Adicionalmente el archivo de texto creado se graba con extensin vhd.

Para nuestro ejemplo: nand2.vhd

Estructura Bsica de un programa VHDL.

Se inicia declarando las bibliotecas que se usarn en el

programa.

Ej: LIBRARY ieee;

USE ieee.std_logic_1164.all; USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

Luego se indica la entidad con sus entradas, salidas y los

modos y tipos de datos.

Modo: IN OUT BUFFER INOUT

Entrada Salida Salida realimentada Bidireccional

Tipo: BIT, STD_LOGGIC, STD_LOGIC_VECTOR

Despus se lista la arquitectura.

Estructura Bsica de un programa VHDL.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.all;

ENTITY <nombre_entidad> IS

PORT(<nombre_pin>: <modo><tipo>; PORT(<nombre_pin>: <modo><tipo>;

<nombre_pin>: <modo><tipo>);

END <nombre_entidad>;

ARCHITECTURE <nombre_arquitectura> OF <nombre_entidad> IS

BEGIN

<sentencia>; <comentario>

<sentencia>; <comentario>

END <nombre_arquitectura>;

Tipos de datos

Ejemplos de tipos de datos

BIT: describe valores binarios. Rango: 0, 1

Ejemplo:

ENTITY nand2 IS

PORT(A,B: IN BIT;

F : OUT BIT); F : OUT BIT);

END nand2;

BIT_VECTOR: describe cadenas de bits. Rango: conjunto de

bits. Se escribe entre comillas: 1010

Ejemplo:

ENTITY manejador IS

PORT (S: IN BIT_VECTOR (3 DOWNTO 0);

X: OUT BIT_VECTOR (1 TO 7));

END manejador;

Ejemplos de tipos de datos

CHARACTER: describe caracteres. Rango:

son los 256 caracteres del estandar ISO

8859-1: 1987 los 128 primeros son los

caracteres ASCII. caracteres ASCII.

a

STRING: describe cadenas de caracteres.

Rango: conjunto de caracteres.

abcde

Estructura de un programa

escrito en VHDL

En VHDL una arquitectura

tiene dos partes: La

regin de las declaraciones

y el cuerpo de la

arquitectura.

ARCHITECTURE nombre_arq OF nombre_ent IS

[Declaracin de seales]

[Declaracin de tipos]

[Declaracin de variables]

arquitectura.

La regin de declaraciones

precede la palabra clave

BEGIN. Puede ser usada

para declarar seales,

variables y constantes.

Tambin puede ser usada

para declarar componentes

y especificar atributos.

[Declaracin de variables]

[Declaracin de constantes]

[Declaracin de componentes]

[Especificacin de atributos]

BEGIN

{Instanciacin de componentes}

{Enunciado concurrente}

{Enunciado secuencial [Proceso]}

END nombre_arq;

Tipos de descripciones dentro

de la arquitectura

Estructural o lgica: Descripcin exacta

del esquema lgico que resuelve la

funcin objeto del diseo. funcin objeto del diseo.

De flujo de datos o RTL.

Comportamental o algortmica

(descripcin funcional).

Descripcin Estructural o lgica

En la descripcin estructural el cuerpo

de la arquitectura se transforma en una

descripcin exacta del esquema lgico.

En la descripcin estructural VHDL usa

las declaraciones de componentes

component nombre_componente

port (seales_entrada: modo tipo;

seales_salida: modo tipo);

las declaraciones de componentes

La cantidad de declaraciones de

componentes debe de corresponder con

la cantidad de componentes distintas

que formarn parte del circuito fsico

que realiza la funcin lgica a disear.

La declaracin component posee una

estructura similar a la de una entidad,

pero no tiene la misma connotacin.

seales_salida: modo tipo);

end component;

Descripcin Estructural o lgica

En la seccin de declaraciones de la

arquitectura (regin ubicada entre la

palabra reservada architecture y la

palabra begin) puede existir la necesidad

de realizar algunas declaraciones de

ARCHITECTURE nombre_arq OF nombre_ent IS

[Declaracin de tipos]

[Declaracin de seales]

[Declaracin de variables]

de realizar algunas declaraciones de

seales internas, las cuales intervienen

en la descripcin del circuito, pero que

no tienen acceso a los terminales

externos del diseo (no estn declaradas

en la entidad.

Aparecen en maysculas las palabras

reservadas del lenguaje VHDL para

resaltarlas, pero no es necesario ya que

el VHDL no es sensible al tipo de letra

[Declaracin de variables]

[Declaracin de constantes]

[Declaracin de componentes]

[Especificacin de atributos]

BEGIN

Instanciacin de componentes

. . .

Instanciacin de componentes

END nombre_arq;

Descripcin Estructural o lgica

Ej: Realizar la

descripcin en VHDL de

tipo estructural de la

operacin EXOR

A

B

Y

operacin EXOR

Y = AB + AB

ENTITY XOR IS

PORT (A,B: IN BIT;

Y: OUT BIT);

END XOR;

Descripcin Estructural o lgica

La arquitectura puede ser la siguiente:

Architecture XOR1 of XOR is

- - declaracin de seales

signal AN, BN : bit;

signal ANB, ABN : bit; signal ANB, ABN : bit;

- - declaracin de componentes

component INV

port (I: in bit;

O: out bit);

end component;

component AND2

port (I1, I2: in bit;

O: out bit);

end component;

component OR2

port (I1, I2: in bit;

O: out bit);

end component;

A

B

Y

AN

BN

ANB

ABN

Descripcin Estructural o lgica

Estamos usando 3 tipos

de componentes: un

inversor (declarado INV),

una compuerta AND de

dos entradas (declarada

AND2) y una compuerta

begin

-- instanciacin de componentes

U1: INV port map (A,AN);

U2: INV port map (B,BN);

U3: AND2 port map (AN,B,ANB);

AND2) y una compuerta

OR de dos entradas

(declarada OR2).

Para la descripcin de la

funcin lgica XOR se

emplearon dos instancias,

U1 y U2 de INV; dos

instancias U3 y U4 de

AND2 y una instancias U5

de OR2.

U3: AND2 port map (AN,B,ANB);

U4: AND2 port map (A,BN,ABN);

U5: OR2 port map (ANB,ABN,Y);

end XOR1;

Descripcin Estructural o lgica

En la asociacin nominal o

explcita se vuelve

irrelevante el orden de los

parmetros, por cuanto

component OR2

port (I1, I2: in bit;

O: out bit);

end component;

parmetros, por cuanto

dentro del parntesis se

indican explcitamente las

seales que se conectan a

los terminales de las

componentes, mediante el

smbolo => de asignacin

begin

. . .

- - asociacin explcita

U5: OR2 port map(O=>Y, I1=>ANB,

I2=>ABN);

end XOR1;

Descripcin Estructural o lgica

ENTITY XOR IS

PORT (A, B: IN BIT;

Y: OUT BIT);

END XOR;

Architecture XOR1 of XOR is

- declaracin de seales

component AND2

port (I1, I2: in bit;

O: out bit);

end component;

component OR2

port (I1, I2: in bit;

O: out bit);

Evidentemente, el estilo estructural de la escritura de una arquitectura

es extenso, incluso para circuitos relativamente pequeos, por lo que si

el circuito es grande su escritura puede ser tediosa y propensa a

cometer errores.

- declaracin de seales

signal AN, BN : bit;

signal ANB, ABN : bit;

- declaracin de componentes

component INV

port (I: in bit;

O: out bit);

end component;

O: out bit);

end component;

begin

- instanciacin de componentes

U1: INV port map(A,AN);

U2: INV port map(B,BN);

U3: AND2 port map(AN,B,ANB);

U4: AND2 port map(A,BN,ABN);

U5: OR2 port map(ANB,ABN,Y);

end XOR1;

Descripcin Estructural o lgica

Uno de los tipos de seales

con que trabaja en VHDL es

el arreglo de seales, tanto

del tipo bit_vector, como del del tipo bit_vector, como del

tipo std_logic_vector. Esto

permite escribir de forma

ms compacta los diseos en

VHDL.

Ellos representan un arreglo

de bits y se utilizan con

dispositivos multiterminales.

Descripcin Estructural o lgica

Ej: Realizar la

descripcin VHDL de

tipo estructural de un

decodificador de 2 decodificador de 2

entradas y 4 salidas,

activadas con el nivel

bajo, y una entrada

de habilitacin,

tambin activa en el

nivel bajo.

Descripcin Estructural o lgica

Lo primero es realizar la

declaracin de la entidad. La

declaracin de la arquitectura

del decodificador, en su

primera parte, corresponde a

architecture decod_a of decod2x4 is

-- declaracin de seales

signal AN(1),AN(0), EN: bit;

-- declaracin de componentes

primera parte, corresponde a

la declaracin de los

diferentes tipos de

componentes. Se usan dos

tipos de componentes: INV,

un inversor y NAND3, una

compuerta NAND de 3

entradas.

-- declaracin de componentes

component INV

port (I: in bit;

O: out bit);

end component;

component NAND3

port (I1, I2, I3: in bit;

O: out bit);

end component;

Descripcin Estructural o lgica

En el cuerpo de la

arquitectura se observa la

instanciacin de los 7

begin

--instanciacin de componentes

U1: INV port map (A(0),AN(0));

U2: INV port map (A(1),AN(1)); arquitectura se observa la

instanciacin de los 7

componentes, los cuales

son conectados usando la

clusula port map con

asociacin implcita.

U2: INV port map (A(1),AN(1));

U3: INV port map (NEN,EN);

U4: NAND3 port map (EN, AN(1), AN(0), NY(0));

U5: NAND3 port map (EN, AN(1), A(0), NY(1));

U6: NAND3 port map (EN, A(1), AN(0), NY(2));

U7: NAND3 port map (EN, A(1), A(0), NY(3));

end decod_a;

Descripcin por flujo de datos

o RTL

En la descripcin por flujo de datos, la

arquitectura describe como fluyen las

seales de entrada por el circuito hacia seales de entrada por el circuito hacia

los terminales de salida.

Este estilo de escritura de la

arquitectura es llamada descripcin de

transferencia de registros RTL (Register

Transfer Language).

Descripcin por flujo de datos

o RTL

En la aproximacin por flujo de

datos se utilizan declaraciones

de asignacin de seales, as

como operadores lgicos que

Ejemplo: La arquitectura por descripcin

de flujo de datos de una compuerta XOR

de dos entradas es:

architecture XOR2 of XOR is

begin

como operadores lgicos que

no se emplean en el estilo de

escritura estructural.

Los operadores lgicos que

tiene el VHDL en sus libreras

son: not, and, or, nand, nor,

xor y xnor.

--asignacin de seales

Y <= (not A and B) or (A and not B);

end XOR2;

Descripcin por flujo de datos

o RTL

La forma de descripcin de la

arquitectura mediante la

aproximacin por flujo de datos

simplifica los diseos VHDL, pues

los hace ms compactos.

Despus de la palabra clave begin

Ejemplo: La existencia del operador XOR

compacta extraordinariamente el cuerpo

de la arquitectura de la entity XOR

Architecture XOR3 of XOR is

Despus de la palabra clave begin

se produce la asignacin del flujo

de datos de las seales del

miembro de la derecha hacia la

seal Y, del miembro de la

izquierda (salida).

El miembro de la derecha del

operador de asignacin <= se le

conoce como expresin, cuyo valor

se obtiene evalundola completa.

Begin

- asignacin de seales

Y <= A xor B;

End XOR3

Descripcin por flujo de datos

o RTL

El VHDL, como otros

lenguajes de programacin

posee un conjunto de

operadores que se usan con

Lgicos: AND, OR, XOR, NOT, NAND,

NOR y XNOR

Aritmticos: +, -, * (multiplicacin solo

por 2)

operadores que se usan con

las seales o con las

variables declaradas en sus

diseos.

por 2)

De relacin: =, /=, <, >, <=, >=

De concatenacin: &

Descripcin por flujo de datos

o RTL

La tabla presentada a

continuacin contiene

una clasificacin de los

operadores definidos en

el lenguaje VHDL, as

como los tipos de datos

Definidos para los tipos

Bit, Boolean, Bit_vector,

std_logic y std_logic_vector

Lgicos:

Operadores

como los tipos de datos

sobre los que se pueden

operar los mismos.

Los operadores lgicos

han sido extendidos al

uso en cualquier tipo de

seal lgica, ya sea

bit_vector, std_logic, o

std_logic_vector.

Integer, Bit, y Bit_vector

Integer

Bit, Bit_vector y para las

cadenas

De relacin:

Aritmticos:

Concatenacin:

Descripcin por flujo de datos

o RTL

Cuando los operadores lgicos

se usan con los tipos de

seales std_logic o bit, ellos

poseen su significado usual.

Los valores '0' y '1' son valores

Un ejemplo de operaciones lgicas con el

tipo de datos vector es el siguiente:

Los valores '0' y '1' son valores

constantes y deben estar

encerrados entre apstrofes.

Cuando el tipo de seal usada

es declarada std_logic_vector

o bit_vector, entonces los

valores deben estar encerrados

entre comillas.

tipo de datos vector es el siguiente:

01100101xor10101101=11001000

Descripcin por flujo de datos

o RTL

Existe un operador interno del

VHDL, que es el signo & y que

realiza la concatenacin de

seales o variables de distinta

longitud.

Ejemplo: Sean las siguientes

declaraciones:

Signal a: bit_vector(1 to 4);

Signal b: bit_vector(1 to 8);

longitud.

En el ejemplo para concatenar la seal a, a la mitad de la

derecha del vector b y no tener incongruencias en los

resultados con vectores se realizan las asignaciones

siguientes. El smbolo & aade el vector a (de 4 bits) al

final de una secuencia de 4 ceros 0000 para realizar

exitosamente la asignacin al vector b, que fue declarado

como un vector de 8 bits.

b<=0000&a;

Descripcin por flujo de datos

o RTL

En el cuerpo de la arquitectura de un

diseo VHDL por RTL se usan,

sentencias concurrentes de asignacin

de seales, cuyo formato se presenta

a continuacin.

-- asignacin de seales

Nombre de la seal<=expresion;

-- asignacin condicional de seales

Nombre de la seal<=expresin1

when expresin booleana else

a continuacin.

En una descripcin RTL, el valor de la

expresin del miembro de la derecha

de la asignacin de seales ( <= ), se

lo transfiere al nombre de la seal del

miembro de la izquierda.

Ambos miembros deben ser del

mismo tipo, para que no existan

incompatibilidades.

when expresin booleana else

expresin2

Nombre de la seal<=expresin1

when expresin booleana else

Nombre de la seal<=expresin1

when expresin booleana else

Expresin2;

Descripcin por flujo de datos

o RTL

Ejemplo 8:

Realice una descripcin en VHDL de

la arquitectura de un comparador

de dos entradas, a y b, de 4 bits

cada una y una salida E de 1 bit.

En esta arquitectura se describe

Entity comp is

Port (a, b: in bit_vector (3 downto 0);

E: out bit);

End comp;

Architecture comparador_1 of comp is

En esta arquitectura se describe

cmo los datos se mueven desde

los terminales de entrada, de seal

en seal, hasta la salida.

Se necesita del conocimiento del

circuito lgico del comparador, del

cual obtener la funcin E de salida:

E=(a0b0)(a1b1)(a2b2)(a3b3)

Architecture comparador_1 of comp is

Begin

--asignacin de seales

E<= not(a(0)xorb(0))

and not(a(1)xorb(1))

and not(a(2)xorb(2))

and not(a(3)xorb(3))

end comparador_1;

Descripcin por flujo de datos

o RTL

Ejemplo 8:

Realice una descripcin en

VHDL de la arquitectura de

un comparador de dos

entradas, a y b, de 4 bits

cada una y una salida E de 1

Library ieee;

Use ieee.std_logic_1164.all;

Entity comp is

Port (a, b: in bit_vector(3 downto 0);

E: out bit);

End comp;

entradas, a y b, de 4 bits

cada una y una salida E de 1

bit.

Otra solucin ms compacta

se puede construir usando la

estructura when else. Esta

solucin no necesita del

conocimiento del circuito

lgico del comparador.

End comp;

Architecture comparador_2 of comp is

Begin

--asignacin de seales

E<=1 when (a=b) else 0;

end comparador_2;

Descripcin por flujo de datos

o RTL

En VHDL, cuando una seal cambia de valor se dice que

se ha producido un evento. La existencia de eventos da

lugar a otro evento (cambio de valores en las expresiones

en los miembros de la derecha de los operadores de

asignacin). De esta manera se actualizan los valores de asignacin). De esta manera se actualizan los valores de

las seales.

En el ejemplo anterior, un cambio en las entradas a o b,

o en ambas provocar un cambio en la expresin. Este

cambio es asignado a la seal de salida E, actualizando

su valor.

E <= '1' when (a=b) else '0';

Descripcin por flujo de datos

o RTL

Otro tipo de sentencia de asignacin

concurrente usada en la descripcin

por flujo de datos es la asignacin

de seal seleccionada, cuya sintaxis

se expresa a continuacin. Este tipo

de declaracin de asignacin utiliza

la estructura with select when

--asignacin de seal seleccionada

with expresin select

de declaracin de asignacin utiliza

la estructura with select when

En esta estructura se evala la

expresin que acompaa a la

declaracin with y cuando el valor

coincide con una de las alternativas

sealadas despus de la palabra

clave when, entonces el valor

correspondiente a esta alternativa se

lo asigna al nombre de la seal.

seal <= valor1 de la seal when alternativa 1,

valor2 de la seal when alternativa 2,

. . .

valorn de la seal when alternativa n;

Descripcin por flujo de datos

o RTL

Las alternativas contenidas

despus de la palabra clave

when pueden ser varias o una

sola. Si son varias, las

alternativas deben ser todas

Valor de la seal when alternativa1 |

alternativa2 | alternativa3 | ..

| alternativaN,

Las barras verticales (|) tienen el

alternativas deben ser todas

distintas y cubrir todos los

posibles valores de stas.

Cuando el valor de la seal

para varias alternativas es el

mismo, pueden ser

expresadas como una lista de

valores separados por barras

verticales ( | )

Las barras verticales (|) tienen el

mismo significado que la operacin OR

Descripcin por flujo de datos

o RTL

Cuando no se cubren todos

los posibles valores de las

alternativas, se debe usar la

palabra clave de VHDL

others, con el ltimo when

--asignacin de seal seleccionada

with expresin select

others, con el ltimo when

en este tipo de asignacin

de seales.

Este tipo de declaracin de

asignacin utiliza la

estructura with select

when others

seal <= valor1 de la seal when alternativa 1,

valor2 de la seal when alternativa 2,

. . .

valorn de la seal when others;

Descripcin por flujo de datos

o RTL

Ejemplo 9:

Escriba en VHDL una

descripcin de la

siguiente funcin:

Entity circuito is

port (m: in integer range (31 downto 0);

T: out std_logic);

End circuito;

siguiente funcin:

T(x,y,z,u,v) =

(0,4,18,19,22,23,25,29) +

(14,16,20,24)

End circuito;

Architecture RTL of circuito is

Begin

-- asignacin de seal seleccionada

With m select

T <= 1 when 0 | 4 | 18 | 19 | 22 | 23 |25 | 29,

- when 14 | 16 | 20 | 24, -- opcionales

0 when others;

end RTL;

Descripcin por flujo de datos

o RTL

Ejemplo 10:

Escriba en VHDL la

descripcin de un circuito

combinacional, el cual recibe

entity detector is

port (N: in integer range (15 downto 0);

P: out std_logic);

end detector;

architecture num_par of detector is

combinacional, el cual recibe

en sus entradas los dgitos del

sistema decimal codificados

en NBCD y tiene una salida P,

que va a 1 cuando se detecta

en sus entradas un dgito par.

architecture num_par of detector is

Begin

-- asignacin de seal seleccionada

with N select

P <= 1 when 0 | 2 | 4 | 6 | 8,

0 when 1 | 3 | 5 | 7 | 9,

- when others; -- opcionales

end num_par;

Descripcin por flujo de datos

o RTL

Ejemplo 11:

Realizar la descripcin por

flujo de datos de un MUX

4 a 1. 4 a 1.

Descripcin por flujo de datos

o RTL

architecture MUX1 of MUX is

signal x: bit_vector(3 downto 0);

Begin

--asignacin de seales

La arquitectura basada en flujo de datos utilizando

operadores lgicos necesita del circuito final de este MUX

X(3) <= S(1) and S(0) and D(3);

X(2) <= S(1) and not S(0) and D(2);

X(1) <= not S(1) and S(0) and D(1);

X(0) <= not S(1) and not S(0) and D(0);

F <= x(3) or x(2) or x(1) or x(0);

end MUX1;

Descripcin por flujo de datos

o RTL

Ejemplo 12: Otra solucin usando

with select.

Como se observa, esta

descripcin de la arquitectura

architecture mux2 of mux is

begin

-- asignacin de seal seleccionada

descripcin de la arquitectura

es ms simple que la anterior y

no necesita del conocimiento

de la lgica interna del circuito.

-- asignacin de seal seleccionada

with S select

F <= D(0) when 00,

D(1) when 01,

D(2) when 10,

D(3) when 11;

end mux2

Descripcin por flujo de datos

o RTL

Ejemplo 13: Disee un

buffer con tercer estado

cuyo circuito se

muestra.

--file: ejemplo13.vhd

library ieee;

muestra.

library ieee;

use ieee.std_logic_1164.all;

entity ejemplo13 is

port (EN_L, A: in std_logic;

Y : out std_logic);

end ejemplo13;

architecture buffer of ejemplo13 is

begin

Y <= A when EN_L = 1 else Z;

end buffer;

Descripcin por flujo de datos

o RTL

Ejemplo 14: Disee un

circuito que multiplique

dos nmeros enteros

positivos de dos bits cada

uno. Debe tener adems

--file: ejemplo14.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ejemplo14 is

uno. Debe tener adems

una entrada habilitadora

EN_L activa en nivel bajo,

tal que la salida est en

un tercer estado de alta

impedancia si EN_L = H

entity ejemplo14 is

port (EN_L: in bit;

A, B: in std_logic_vector(1 downto 0);

P: out std_logic_vector(3 downto 0));

end ejemplo14;

architecture producto of ejemplo14 is

begin

with EN_L select

P <= A*B when 1,

ZZZZ when 0;

end producto;

Descripcin por flujo de datos

o RTL

Ejemplo 15:

Empaquetar el diseo

del buffer con tercer

estado cuyo circuito se

library ieee;

use ieee.std_logic_1164.all;

PACKAGE bufferPCK is

component ejemplo13

estado cuyo circuito se

muestra en la figura.

component ejemplo13

port( EN_L, A: in std_logic;

Y: out std_logic);

end component;

end bufferPCK;

File: bufferPCK.vhd

Sentencias Concurrentes

Introduccin

Las sentencias concurrentes son aquellas que se

ejecutan simultneamente en la simulacin. Se utilizan

para el modelado del hardware, deben formar parte para el modelado del hardware, deben formar parte

siempre del cuerpo de arquitecturas o de bloques y son

las siguientes:

Procesos

Asignaciones concurrentes a seal

Llamadas concurrentes o procedimientos

Instanciaciones de componentes

Sentencia when - else

Permite realizar asignaciones condicionales de valores, expresiones u

objetos o seales. Su sintaxis de declaracin es:

[etiqueta:] seal <= valor_1 when condicin_1 else

valor_2 [when condicin_2] [else valor_2 [when condicin_2] [else

] [else

valor_n when condicin_n] [else unaffected];

La seal recibe una asignacin u otra (valor_1valor_n) en funcin de

las condiciones que aparecen tras when. Para la opcin de no

asignacin puede (no cambio en la funcin) utilizarse la keyword

unaffected

Ejemplo de sentencia when - else

Modelo de un sumador de un bit con retencin de la suma

entity SUMADOR is:

port(A, B: in bit; ENABLE: in bit ;

SUMA: out bit_vector (1 downto 0)); SUMA: out bit_vector (1 downto 0));

end SUMADOR;

architecture CON_WHEN of SUMADOR is

begin

SUMA <= 00when (A=0 and B= 0 and ENABLE = 1) else

01when (A=1 and B= 0 and ENABLE = 1) else

01when (A=0 and B= 1 and ENABLE = 1) else

10when (A=1 and B= 1 and ENABLE = 1) else

unaffected;

end CON_WHEN

Sentencia with-select

Su sintaxis es la siguiente:

[etiqueta:] with expresin select

seal <= valor_1 when resultado_1[, seal <= valor_1 when resultado_1[,

valor_2 when resultado_2] [,

..] [,

valor_n when resultado_n] [,

unaffected when others];

El valor asignado depende de la evaluacin de la expresin que aparece

entre las palabras reservadas with y select. El resultado se compara con

los valores tras when y se ejecuta la asignacin que resulta verdadera.

Ejemplo de sentencia with-select

El sumador anterior puede ser descrito tambin del siguiente modo:

architecture CON_WITH_SELECT of SUMADOR is

begin

with (ENABLE & A & B ) select with (ENABLE & A & B ) select

SUMA <= 00 when 100,

01 when 101,

01 when 110,

10 when 111,

unaffected when others;

end CON_WITH_SELECT;

Sentencias Secuenciales

Introduccin

Las sentencias secuenciales son aquellas que

solamente pueden aparecer dentro de procesos y

subprogramas. Se ejecutan ordenadamente, de tal subprogramas. Se ejecutan ordenadamente, de tal

manera que el simulador finaliza completamente

una sentencia antes de pasar a la siguiente.

Todo lo contrario de lo que ocurre en las sentencias

concurrentes en donde no importa el orden.

Sentencia wait

Es una de las ms utilizadas en el modelado de circuitos sncronos,

wait detiene la ejecucin de un proceso o un procedimiento en

espera de que se satisfaga una determinada condicin. Su sintaxis es

la siguiente:

[etiqueta:] wait [on seal_1, seal_2,..]

[until condicin]

[for expresin_temporal];

Por tanto puede haber tres tipos de argumentos de ellos, o bien

ninguno. En este ltimo caso el proceso queda detenido hasta el final

de la simulacin.

Sentencia Wait on

Wait on produce el mismo efecto que la lista de sensibilidad de un

proceso. Por ejemplo:

PROCESO_1: process(A,B)

begin begin

end process PROCESO_1;

PROCESO_2: process

begin

wait on A,B;

end process PROCESO_2

Case - when

La sentencia case-when permite seleccionar una entre varias

alternativas excluyentes entre s de una expresin determinada, su

sintaxis general es la siguiente:

[etiqueta:] case expresin is [etiqueta:] case expresin is

when caso_1[ caso_2 ] => sentencias secuenciales

....

end case [etiqueta];

De este modo una arquitectura alternativa para el mismo sumador

anterior podra ser como se muestra a continuacin.

Ejemplo de Case-When

architecture CON_CASE of SUMADOR is

begin

process

variable X: bit_vector(2 downto 0);

begin begin

X<= ENABLE & A & B;

case X is

when 100=> SUMA <=00;

when 101| 110 => SUMA <=01;

when 111 => SUMA <= 10;

when others => null;

end case;

end process;

end CON_CASE

Bucles

Para la ejecucin de bucles en VHDL se utiliza la palabra reservada

loop. Existen tres formas de definir un bucle:

- Con for-loop siempre se hace referencia a un bucle finito, - Con for-loop siempre se hace referencia a un bucle finito,

-Con while-loop a uno finito o infinito (depende de la condicin) y

-Con simplemente loop a uno infinito

A continuacin analizaremos estas tres opciones.

For - Loop

Esta sentencia causa la ejecucin de un bucle un numero fijo de veces,

su sintaxis es la siguiente:

[etiqueta:] for indice in rango loop [etiqueta:] for indice in rango loop

sentencias secuenciales

end loop [etiqueta];

Es necesaria las indicaciones de un ndice y un rango. El ndice es una

variable discreta, enumerada o entera, que no es preciso declarar y que

cambia su valor en una unidad por cada ejecucin del bucle a lo largo

del rango especificado.

Ejemplo For-loop

Contar el numero de unos de una seal binaria de 32 bits.

.

for I in 0 to 31 loop for I in 0 to 31 loop

if SENAL (I)=1 then NUMERO_UNOS:= NUMERO_UNOS+1;

end if;

end loop;

.

While - Loop

El siguiente tipo de bucle utiliza la palabra reservada while para

imponer la condicin de repeticin. Su sintaxis es la siguiente:

[etiqueta:] while condicin loop [etiqueta:] while condicin loop

sentencias secuenciales

end loop [etiqueta];

El bucle se repite en tanto que la condicin que aparece tras while sea

verdadera.

Ejemplo While-loop

.

I:=0;

while (I>32) loop

if SEAL (I)=1 then NUMERO_UNOS:= NUMERO_UNOS+1;

end if

I:= I+1;

end loop;

....

Ahora si se nesecita declarar una variable (I) para poder establecer la

condicin del bucle, no resulta ventajosa con respecto a for loop.

Loop

Ejecuta un bucle infinito y su sintaxis es as:

[etiqueta:] loop

sentencias secuenciales

end loop [etiqueta];

También podría gustarte

- Solucionario Ej - Impares Análisis de Circuitos en Ingeniería - W. Hayt - 7ed PDFDocumento255 páginasSolucionario Ej - Impares Análisis de Circuitos en Ingeniería - W. Hayt - 7ed PDFShelene Guzman Garza61% (28)

- Manual Motoniveladora Volvo G930Documento2 páginasManual Motoniveladora Volvo G930alexander gasca100% (2)

- Cotizacion AscensoresDocumento10 páginasCotizacion AscensoresDeivi Emilio Camacho Boada100% (1)

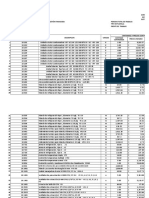

- Cable Electrico - Planilla GeneralDocumento44 páginasCable Electrico - Planilla GeneralFernando CahueñasAún no hay calificaciones

- RecetarioDocumento25 páginasRecetarioFernando Cahueñas100% (2)

- Recetario Navidad PronacaDocumento46 páginasRecetario Navidad PronacaMaria Soledad Tolosa CardenasAún no hay calificaciones

- Informe Proyecto Telefonia CelularDocumento21 páginasInforme Proyecto Telefonia CelularAcvd MiloAún no hay calificaciones

- Examen Final Alumno FinalDocumento8 páginasExamen Final Alumno FinalFernandoAún no hay calificaciones

- JumpersDocumento8 páginasJumpersRafael García HernándezAún no hay calificaciones

- Memoria de Calculo Estructural de Plataforma de OperaciónDocumento12 páginasMemoria de Calculo Estructural de Plataforma de OperaciónRamos JavierAún no hay calificaciones

- Como Instalar y Configurar Un Localizador de GPSDocumento4 páginasComo Instalar y Configurar Un Localizador de GPSEDUAR EDGARDO RAMOS TAPIASAún no hay calificaciones

- Agreement ENGLISH-SPANISHDocumento5 páginasAgreement ENGLISH-SPANISHAbril FerreyraAún no hay calificaciones

- Virus TroyanoDocumento3 páginasVirus TroyanoJORGEAún no hay calificaciones

- Normas ICONTEXDocumento19 páginasNormas ICONTEXDiegoAún no hay calificaciones

- Generador HimoinsaDocumento12 páginasGenerador HimoinsabarriosedwardAún no hay calificaciones

- ML2 CML 01B C 11B Svis Iered Dis PL 7801 01Documento1 páginaML2 CML 01B C 11B Svis Iered Dis PL 7801 01Geraldo DonayreAún no hay calificaciones

- Formulario Unidades de ConversiónDocumento2 páginasFormulario Unidades de ConversiónNelsy Visa50% (2)

- Certificado de Calibracion - ROTAMETRO - 122606Documento4 páginasCertificado de Calibracion - ROTAMETRO - 122606Amaya FerAún no hay calificaciones

- Resumen IRAMDocumento6 páginasResumen IRAMloli1707Aún no hay calificaciones

- Bus Actuadores y Sensores As-IDocumento47 páginasBus Actuadores y Sensores As-IPhilip J. FryAún no hay calificaciones

- Propiedades de Fluidos y Accesorios Mec Fluid IIDocumento35 páginasPropiedades de Fluidos y Accesorios Mec Fluid IIrubiAún no hay calificaciones

- HDLC EjemplosDocumento60 páginasHDLC EjemplosJanner A. García0% (2)

- Manejo DefensivoDocumento40 páginasManejo Defensivojose luisAún no hay calificaciones

- Curso BPNM UmlDocumento28 páginasCurso BPNM UmlAndres Ignacio Slim Show100% (1)

- BIOFISICADocumento5 páginasBIOFISICAVialy SantanaAún no hay calificaciones

- Intercambiabilidad y Normas de Ajustes y ToleranciasDocumento17 páginasIntercambiabilidad y Normas de Ajustes y ToleranciasAlfred JimenezAún no hay calificaciones

- 98-366 Fundamentos de RedesDocumento204 páginas98-366 Fundamentos de Redesmarkby50% (2)

- Volcan, Ssomac A IcmDocumento36 páginasVolcan, Ssomac A IcmcabalaestebanAún no hay calificaciones

- Especificaciones Tecnicas Material de Puesta A TierraDocumento9 páginasEspecificaciones Tecnicas Material de Puesta A TierracarlosherbayAún no hay calificaciones

- Foro de Las Normas IsoDocumento4 páginasForo de Las Normas IsoHellen AlvarezAún no hay calificaciones

- Avaya G650 Media GatewayDocumento2 páginasAvaya G650 Media GatewayElio MolinaAún no hay calificaciones

- Gestion de La Produccion Unidad 3Documento10 páginasGestion de La Produccion Unidad 3MaryLuna0% (1)

- 1 GPON Despliegue - Proceso y SistemasDocumento17 páginas1 GPON Despliegue - Proceso y Sistemasprovenser electricAún no hay calificaciones

- Ficha Acero ArcelorMittalDocumento1 páginaFicha Acero ArcelorMittalRamiro Saborio100% (1)