Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Contador Ascendente y Descendente Utilizando Flipflops

Contador Ascendente y Descendente Utilizando Flipflops

Cargado por

Oscar Julian Casadiego MachucaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Contador Ascendente y Descendente Utilizando Flipflops

Contador Ascendente y Descendente Utilizando Flipflops

Cargado por

Oscar Julian Casadiego MachucaCopyright:

Formatos disponibles

Universidad Austral de Chile

Facultad de Ciencias de la Ingeniera

Trabajo prctico 2.

Contadores

Sistemas Lgicos Binarios ELEL-170

Integrantes: Fernando Nanco

Andrs Snchez

Juan Luis Almendras

Profesor: Dr. A. Madalinski

28/06/2012

Resumen

El presente informe trata sobre disear dos tipos de contadores: ascendente y descendente.

Ambos contadores son de dcadas, es decir, de 0 a 9. Para una mayor comprensin de como

funcionan los contadores se analiza desde uno de los componentes ms esenciales que es el

flip-flop, los cuales pueden ser de cualquier tipo, pero para ste diseo se utilizo el flip-flop

JK. Luego se comprender que es lo que sucede al conectar estos flip-flops en cascada y para

que uso se da en los contadores.

Comprendiendo la materia prima, se da inicio a los contadores, analizando sus diagramas de

impulso para poder obtener los nmeros deseados, pues primero contaban en hexadecimal (de

1 a F), por lo que se le agrego una compuerta NAND al contador ascendente y compuertas OR

junto con un flip-flop D al contador descendente. El flip-flop D fue utilizado para crear un

lapso de tiempo entre los pulsos del reloj, ya que haba un salto de numeracin en el contador

desde 1 a 9 saltando el 0.

Los resultados obtenidos fueron satisfactorios a lo propuesto para los diseos, junto con n

gran aprendizaje sobre como funcionan los contadores y por sobre todo la dificultad para

crear un contador descendente. Cabe mencionar que se pudo crear de otra manera este timo,

utilizando una resistencia con un condensador, pero la intencin del informe era disear los

contadores con flip-flops.

INTRODUCCIN

En la actualidad, los sistemas digitales son muy utilizados y variados para diferentes tipos de

aplicaciones las cuales en su mayora son aplicadas en la industria y en mayor parte de los equipos

electrnicos, adems de esto el diseo de un contador puede ser abarcado por un microcontrolador o

algn tipo de dispositivo ms avanzado, sin embargo comparando costos y siendo una aplicacin

sencilla el diseo de estos dispositivos pueden ser empleados por flip flop que se pueden encontrar

en forma comercial y a un bajo costo.

Es por esto que a continuacin le presentamos el siguiente trabajo, destinado a comprender de mejor

manera cmo funcionan los contadores, mediante su diseo, siendo estos ascendentes y

descendentes, utilizando flip flops. Por otra parte en el desarrollo del diseo uno de los mtodos

utilizados fue mediante el anlisis de impulsos y as ir creando las distintas compuertas como son

las NAND, OR, y flip flops.

El flip-flop J-K. Contadores

Los flip-flop son uno de los elementos ms importantes, si no el ms importante, en el arsenal de los

bloques fundamentales de los circuitos lgicos conocidos como secuenciales. Este elemento es

el flip-flop J-K y se representa con el smbolo de la figura 1:

Figura 1. Simbolo de un flip-flop JK.

Como puede verse en el smbolo del flip-flop J-K, este posee dos salidas complementarias Q y

al

junto con dos entradas, J y K.

Las caractersticas del flip-flop J-K son las siguientes:

(1) Cuando J=1 y K=1, al ir la entrada de la terminal de reloj C (clock) de 1 a 0 nada ocurre y el

flip-flop J-K retiene el estado que posea anteriormente.

(2) Cuando J=1 y K=0, al ir la entrada C de 1 a0 el flip-flop J-K tomar el estado Q=1

independientemente del estado en el que se encontraba anteriormente.

(3) Cuando J=0 y K=1, al ir la entrada C de 1 a 0 el flip-flop J-K tomar el estado Q=0

independientemente del estado en el que se encontraba anteriormente.

(4) Cuando J=0 y K=0, al ir la entrada C de 1 a 0 el flip-flop J-K tomar un estado opuesto a aqul

en el cual se encontraba anteriormente. Esto quiere decir que si antes de la transicin en la

terminal C de 1 a 0 el flip-flop J-K se encontraba en el estado Q=1, entonces tomar el estado Q=0

despus de la transicin. Asimismo, si se encontraba en el estadoQ=0 antes de la transicin,

entonces tomar el estado Q=1 despus de la transicin.

En resumidas cuentas se hace una tabla de verdad para mayor comprensin, ver tabla 1.

Modo operacin A B Q

Mantenimiento 0 0

Reset 0 1 0 1

Set 1 0 1 0

conmutacin 1 1

Tabla 1. Tabla de verdad Flip flop JK.

Divisor de frecuencia

La funcin

(invertir el estado anterior) de un flip-flop JK significa contar siguiendo la serie 0 -

1 - 0 - 1 etc.

Conectando en cascada dos flip-flops JK, el primer flip-flop puede suministrar en su salida la seal

de reloj para el segundo flip-flop. Empleando este principio se pueden implementar tanto un

contador, como un divisor de frecuencia. Como se muestra en la figura 2, tenemos cmo ocurre la

divisin de frecuencia.

Figura 2. Diseo para un divisor de frecuencias junto su diagrama de impulso.

Como se observa en el grafico si tomamos a Q

0

como LSB (dgito menos significativo) y a Q

3

como

MSB (dgito ms significativo), se pueden interpretar los impulsos como nmeros binarios tal como

muestra la tabla 2:

Hexadecimal Q3 Q2 Q1 Q0

0 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

10 1 0 1 0

11 1 0 1 1

12 1 1 0 0

13 1 1 0 1

14 1 1 1 0

15 1 1 1 1

Tabla 2. Nmeros decimales producidos por las salidas de Q

0

hasta Q

3

.

Como ya se mencion anteriormente, el diseo de un contador contar, valga la redundancia, en

forma ascendente desde 0 hasta 15 en teora, pues en realidad el display mostrar nmeros desde el

0 hasta el 9 y luego smbolos especiales. Tambin el contador es anlogo a un circuito divisor de

frecuencia con flip flops JK, que es capaz de dividir la frecuencia de entrada hasta ocho veces.

Notamos que hemos generado un contador binario capas de contar hasta 1111

2

(binario)

15

10

(decimal) y adems que sigue un ciclo repetitivo.

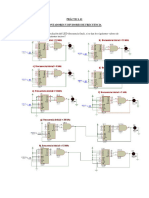

Contador A: Diseo para un contador binario ascendente desde 0 hasta 9 decimal.

Nuestro diseo para un contador ascendente, se basa bsicamente en flip flop JK en cascada, tal

como un divisor de frecuencias, cabe mencionar que estos van en configuracin de flip flop T. En

nuestro caso se nos pide contar de 0 a 9, entonces para ello se deben usar 4 bits, y por lo que se

requieren 4 flip flop JK, dado que no se encontraron en el mercado flip flop JK asncrono, se opto

por hacer el diseo con flip-flops sncronos, en cuanto al flanco positivo o negativo, de por s no es

importante en este diseo, pues es tan bsico que se puede hacer con flancos de subida, as como

flancos de bajada, sus nicas diferencias sern las configuraciones entre la salida Q conectadas con

las entradas de reloj del siguiente flip-flop. Por lo anteriormente mencionado el diseo del contador

utilizar flip-flop JK con flanco de bajada, adems con set y reset negados, tal como los flancos del

reloj, en este diseo las entradas set y reset pueden o no ser negadas pues si se utilizan ms

adelante, no quiere decir que sea necesaria su negacin. Por lo que se muestra el contador

ascendente en la figura 3.

Figura 3. Contador ascendente con flip flop JK.

Se observa que el diseo de la figura 3 es igual al divisor de frecuencias de la figura 2, esto quiere

decir que el displey mostrar nmeros desde el 0 hasta el 9 y luego smbolos especiales (en este

caso mostrara letras desde la A hasta la F), para evitar los smbolos no deseados se utiliza una

compuerta NAND con entrada Q

1

y Q

3

, esto quiere decir que cuando se activen ambas entradas, la

salida ser un 0 lgico, y la salida del NAND va conectada a las entradas reset de cada flip-flop,

provocando as un reinicio en cada flip-flop pues estos se reiniciarn con un 0 lgico ya que su reset

se encuentra negado. Ver figura 4.

Figura 4. Contador ascendente de dcadas con flip flop JK.

De esta manera obtenemos nuestro contador decimal de 0 a 9 ya que al llegar 10 se activa el reset en

todos los flip-flop, devolviendo a 0 el contador. En cuanto a la tabla de verdad para este contador es

igual a la tabla 1, con la diferencia de que llega solo hasta 9.

Contador B: Diseo para un contador binario descendiente desde 9 hasta 0 decimal.

El contador descendente se creo basando la misma manera que el ascendente, es decir, 4 flip-flop

JK con flanco de bajada, reset y set negados y reloj flanco de bajada. La diferencia al anterior

contador son las salidas desde Q

0

hasta Q

3

las cuales salen desde los

de cada flip flop JK, tal

como se ve en la figura 5.

Figura 5. Diseo para un contador descendente de 4 bits con flip flop JK.

La tabla de verdad para cada Q

n

es la misma tabla que utiliza el contador ascendente, pues como se

dijo anteriormente, los contadores estn diseados como divisores de frecuencia, adems en la

figura 6 se observan los diagramas de impulsos formados por este contador.

Cl

k

5 4 3 2 1 0 15(F

)

14(E

)

13(

D)

12(

C)

11(

B)

10(

A)

9 8 7 6

Q

0

Q

1

Q

2

Q

3

Figura 6. Diagrama de pulsos para un contador descendente de 4 bits, en rojo el reloj, en verde las salidas

Q

n

.

Como se ve en el diagrama de la figura 6, el display BCD mostrar nmeros desde la letra F hasta el

nmero 0, lo cual an no se logra el objetivo para un contador descendente de dcadas. La solucin

a este problema es agregando tres compuertas OR junto con un flip-flop D, tal como muestra la

figura 7.

Figura 7. Diseo para un contador descendiente de dcadas con flip-flop JK y D.

La intencin de conectar las compuertas OR en esa configuracin, es tener a la salida de estos un 0

solamente cuando el conteo llegue hasta 0, en otras palabras, hasta que todas las Q

n

se encuentren

en 0 lgico, pes las entradas en los flip-flop JK de reset se encuentran negadas, al igual que las set.

Provocando as un reseteo (desactivacin) en Q

1

y Q

2

junto con una activacin en Q

0

y Q

3

, dando

como resultado un 9 binario.

El flip-flop D tiene flanco de subida, a diferencia de los JK con flancos de bajada, pues su intencin

es retener la seal de reseteo para que la salida muestre un 0 decimal. ste flip-flop se coloc ya

que de otra manera cuando se llegaba de 1 a 0 decimal, el reset se aplicaba inmediatamente,

provocando un salto desde 1 hasta 9 sin mostrar 0.

El diagrama de impulso para el diseo del contador de la figura 7 se observa en la figura 8.

Clk

5 4 3 2 1 0 9 8 7 6 5 4 3 2 1 0

Q

0

Q

1

Q

2

Q

3

D

Figura 8. Diagrama de impulsos para un contador descendiente de dcadas, en rojo el reloj, en verde las

salidas Q

n

, en amarillo la salida Q en el flip flop D.

Otra forma de evitar este salto sera utilizando un condensador junto con una resistencia, esto

provocara un tiempo de carga en el condensador y as atrasar el impulso para el reseteo de los Q

1

y

Q

2

.

Conclusin

En el desarrollo de este informe, se ha tratado de explicar el funcionamiento de un flip flop JK y con

ello algunas aplicaciones, como en el caso de ste, un contador ascendente de 0 a 9 y descendente de 9

a 0, donde podemos decir que su funcionamiento es basado de un circuito divisor de frecuencias con 4

flip flop JK, para el contador ascendente, cabe mencionar que para poder que este solo cuente hasta 9

se debe hacer una conexin con una compuerta NAND sino al llegar a nueve seguir la cuenta y

enviar datos errneos, mas bien smbolos especiales, hasta que la cuenta binaria llegue a 1111 o en

hexadecimal 15, para ello, es imprescindible el uso de esta compuerta en las salidas Q2 y Q4 del

circuito. Luego para el contador descendente podemos inferir que es un caso algo mas complejo que el

anterior, el cual est compuesto de compuertas OR y 5 flip flop JK, donde el objetivo de esto fue tener

a la salida de estos un 0 solamente cuando el conteo llegue hasta 0, en otras palabras, hasta que todas

las Qn se encuentren en 0 lgico, pes las entradas en los flip-flop JK de reset se encuentran negadas,

al igual que las set. Provocando as un reseteo (desactivacin) en Q1 y Q2 junto con una activacin en

Q0 y Q3, dando como resultado un 9 binario, el cual cabe mencionara que se tuvo como dificultad

mayor al pasar de 1 a 0 dado que es necesario tener un tau, para que este no pase directo de 1 a 9 en

cuenta regresiva, lo cual se pudo resolver poniendo un quinto flip flop, un tipo D, para as tener este

valor y contar en forma descendente de 9 a 0.

Cabe destacar la importancia de esta tarea, para entender el comportamiento y algunas de las

innumerables aplicaciones de los flip flop y las compuertas lgicas, dado que en electrnica es

imprescindible tener el dominio de este tema.

También podría gustarte

- Registro DesplazamientosDocumento6 páginasRegistro DesplazamientosElvis Paucar SocasiAún no hay calificaciones

- Contadores y RegistrosDocumento19 páginasContadores y RegistrosElymar91Aún no hay calificaciones

- Contador Flip-Flop Tipo JKDocumento5 páginasContador Flip-Flop Tipo JKOvanio MolinaAún no hay calificaciones

- Pre Informe Lab - 5 Sistemas DigitalesDocumento10 páginasPre Informe Lab - 5 Sistemas DigitalesJosue Mendoza RuedaAún no hay calificaciones

- Practica 8G2 Contador Sincrono FlipFlop DLDocumento4 páginasPractica 8G2 Contador Sincrono FlipFlop DLAlexander Robles CaicedoAún no hay calificaciones

- Flip-Flop J-KDocumento15 páginasFlip-Flop J-KWalter CMAún no hay calificaciones

- Práctica 3 Sensores Generadores PDFDocumento4 páginasPráctica 3 Sensores Generadores PDFAdriánAún no hay calificaciones

- Termometro HDBLDocumento5 páginasTermometro HDBLJonathan Raul Alvarez LopezAún no hay calificaciones

- Informe 06 - RodrigoCabezasDocumento13 páginasInforme 06 - RodrigoCabezasArturo Armando100% (1)

- Contador de 0-99 Con AlarmaDocumento3 páginasContador de 0-99 Con AlarmaMarvin GarcíaAún no hay calificaciones

- Reloj Digital ProyectoDocumento6 páginasReloj Digital ProyectoJavier Alberto MontañaAún no hay calificaciones

- Ejercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialDocumento7 páginasEjercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialWilmer Villegas CodenaAún no hay calificaciones

- Contadores y RegistrosDocumento16 páginasContadores y RegistrosLaura VallejoAún no hay calificaciones

- Contador DijitalDocumento10 páginasContador Dijitaltomkito100% (1)

- Capitulo 4. Transformada de Fourier - Rev1Documento12 páginasCapitulo 4. Transformada de Fourier - Rev1Raul GonzalesAún no hay calificaciones

- Flip Flop JKDocumento14 páginasFlip Flop JKYessenia López0% (1)

- Codigo en VHDLDocumento6 páginasCodigo en VHDLGabriel Ch MendezAún no hay calificaciones

- l09 Puerto SerialDocumento8 páginasl09 Puerto SerialJavier ParedesAún no hay calificaciones

- Movimiento de RototraslacionDocumento6 páginasMovimiento de RototraslacionFranciscoAún no hay calificaciones

- Laboratorio - Reg Desplazamiento y Contadores - VHDLDocumento12 páginasLaboratorio - Reg Desplazamiento y Contadores - VHDLvickysalazar6165Aún no hay calificaciones

- Examen de Aljebra de BooleDocumento7 páginasExamen de Aljebra de BooleJohann RodríguezAún no hay calificaciones

- Contador Digital 7490 Modulo 2Documento15 páginasContador Digital 7490 Modulo 2nestorAún no hay calificaciones

- Informe Proyecto Seguidor de LineaDocumento33 páginasInforme Proyecto Seguidor de LineaDavid Lema100% (1)

- Practica 4 EEB PDFDocumento2 páginasPractica 4 EEB PDFrubenpr17Aún no hay calificaciones

- Comparador de Ventana Amplificadores OperacionalesDocumento2 páginasComparador de Ventana Amplificadores OperacionalesFredy Nava100% (1)

- Ensayo"Inversor DC/AC de Onda Pura para Cargas Monofasicas A Traves de SPWM Con Microcontroladores"Documento4 páginasEnsayo"Inversor DC/AC de Onda Pura para Cargas Monofasicas A Traves de SPWM Con Microcontroladores"Jaime Potes PardoAún no hay calificaciones

- SimonSays FPGA FinalDocumento10 páginasSimonSays FPGA FinalnalytoolsAún no hay calificaciones

- Divisores de Frecuencia Con Flip FlopDocumento2 páginasDivisores de Frecuencia Con Flip FlopLeonardo CorredorAún no hay calificaciones

- Problemas SimuladosDocumento6 páginasProblemas SimuladosRaúl Dylan CapchaAún no hay calificaciones

- Proyecto Circuito Contador AutomaticoDocumento4 páginasProyecto Circuito Contador AutomaticoSantiago Xavier Yepez LeitonAún no hay calificaciones

- El Circuito Integrado 7476 Consta de 2 FlipDocumento4 páginasEl Circuito Integrado 7476 Consta de 2 FlipalexanderRuizSAún no hay calificaciones

- Flip FlopDocumento9 páginasFlip FlopCarlosAndresMirandaHernandesAún no hay calificaciones

- Optativa Informe 1Documento4 páginasOptativa Informe 1Henry D. LópezAún no hay calificaciones

- ADC0804 Descripción GeneralDocumento2 páginasADC0804 Descripción GeneralFranco RibaAún no hay calificaciones

- Practica - 1 Sis Digis 2Documento7 páginasPractica - 1 Sis Digis 2Mathy MerinoAún no hay calificaciones

- Configuracion ADC PIC16F887Documento8 páginasConfiguracion ADC PIC16F887Gabriel OrtizAún no hay calificaciones

- Diagramas de BodeDocumento12 páginasDiagramas de BodeAlex SuáMAún no hay calificaciones

- Desarrollo de Experiencia 4 Caja FuerteDocumento4 páginasDesarrollo de Experiencia 4 Caja FuerteLucas CastilloAún no hay calificaciones

- Fundamentos de Diseño Digital LecturaDocumento316 páginasFundamentos de Diseño Digital LecturaJuan PerezAún no hay calificaciones

- Lab, Control PDFDocumento2 páginasLab, Control PDFjair eduardo mendez gonzalesAún no hay calificaciones

- Electronica Digital FlipFlopDocumento83 páginasElectronica Digital FlipFlopGustavo BurbanoAún no hay calificaciones

- Práctica No.2 InstrumentacionDocumento9 páginasPráctica No.2 InstrumentacionJose Refugio BoshAún no hay calificaciones

- Cronómetro DigitalDocumento7 páginasCronómetro DigitalJhoselyn Pamela GuachaminAún no hay calificaciones

- ASHG2Documento55 páginasASHG2Daniela AlzateAún no hay calificaciones

- Adquisicion de DatosDocumento19 páginasAdquisicion de DatosLeonidas MianoAún no hay calificaciones

- Aplicaciones Del SCR 1 2 4xsc1rDocumento3 páginasAplicaciones Del SCR 1 2 4xsc1rDaniela ToaingaAún no hay calificaciones

- Proteus Practica 2 AscensorDocumento1 páginaProteus Practica 2 AscensorGregorio Caballero RosalesAún no hay calificaciones

- Pic16f877 PDFDocumento74 páginasPic16f877 PDFCarliTos Javier100% (1)

- DIVISOR DE FRECUENCIA (Flip Flop) PDFDocumento6 páginasDIVISOR DE FRECUENCIA (Flip Flop) PDFMichael Cáseres ArmijosAún no hay calificaciones

- Informe Control PidDocumento9 páginasInforme Control PidByron ArgosAún no hay calificaciones

- Diseño Flip FlopDocumento8 páginasDiseño Flip FlopLuis GonzálezAún no hay calificaciones

- Rectificadores Trifasicos y Multifasicos de Onda Completa, InformeDocumento6 páginasRectificadores Trifasicos y Multifasicos de Onda Completa, InformeVíctor •Aún no hay calificaciones

- Ejercicos en Atmega 164p Uso de Inteepciones de Los PorticosDocumento4 páginasEjercicos en Atmega 164p Uso de Inteepciones de Los PorticosWilmer Villegas CodenaAún no hay calificaciones

- ContadoresDocumento11 páginasContadoresDan GoldmannAún no hay calificaciones

- Diseño de ContadoresDocumento5 páginasDiseño de ContadoresOvanio MolinaAún no hay calificaciones

- Apuntes Contadores - 1da ParteDocumento5 páginasApuntes Contadores - 1da ParteRoxana LeivaAún no hay calificaciones

- Contador FFDocumento5 páginasContador FFFranLeonRafaelAún no hay calificaciones

- Practica de Oac-IDocumento9 páginasPractica de Oac-ILuis Alberto Sota OrellanaAún no hay calificaciones

- Contadores Sincrónicos Binarios y BCDDocumento5 páginasContadores Sincrónicos Binarios y BCDStuardo SagastumeAún no hay calificaciones

- Circuitos ContadoresDocumento11 páginasCircuitos Contadoresdark_0Aún no hay calificaciones

- COMOHABLARENPUBLICODocumento16 páginasCOMOHABLARENPUBLICOReflexión GtAún no hay calificaciones

- Tabla de Codigos para LetrasDocumento3 páginasTabla de Codigos para LetrasJheinso Alberto Sierra RiveraAún no hay calificaciones

- Cubo LEDDocumento8 páginasCubo LEDJuan Diego Sanabria Martines100% (1)

- Hombre de Honor HechoDocumento2 páginasHombre de Honor HechoAlex FrostWellAún no hay calificaciones

- Saber EDocumento75 páginasSaber EEmilio Xia100% (5)