Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Diseno de Bloques de Memoria

Diseno de Bloques de Memoria

Cargado por

RobErto OrtiizDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Diseno de Bloques de Memoria

Diseno de Bloques de Memoria

Cargado por

RobErto OrtiizCopyright:

Formatos disponibles

Diseo de mapas de memoria

DISEO DE BLOQUES DE MEMORIA

La ampliacin de componentes es una caracterstica del diseo y en el caso de las memorias tiene dos objetivos: � Incrementar el tamao de las palabras. � Incrementar el nmero de palabras de memoria. Un sistema basado en microprocesador tiene una capacidad de direccionamiento y anchura de palabra en funcin de las caractersticas del microprocesador de acuerdo al bus de direcciones y del de datos respectivamente. Siendo el bus de control, especfico al microprocesador. De esta manera, la capacidad del sistema depende de: Direccionamiento del sistema Ancho de palabra

2n siendo n el n de bits del bus de direcciones del P

siendo m el n de bits del bus de datos del P

Bus de control depende del P, siendo las seales tpicas para la memoria la de lectura ( R ) y la de escritura (W)

Procedimiento para el diseo de un mapa de memoria de un sistema basado en microprocesador:

1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. 3. Construir el mapa de memoria. 4. Determinar el tamao de pgina y disear la tabla de direcciones y ocupacin de cada circuito integrado. 5. Determinar la circuitera auxiliar necesaria para el control del circuito. 6. Dibujar el circuito completo de la memoria. Para analizar el procedimiento tomaremos como base el siguiente ejemplo: � Disear el mapa de memoria de un sistema basado en microprocesador para el 8085 de INTEL (A0..A15, D0..D7), suponiendo que se necesitan 8K8 de memoria ROM, 4K8 de memoria RAM. Se disponen de circuitos integrados ROM de 2K8 y circuitos integrados RAM de 2K8 y que la memoria est situada a partir de la direccin $0 empezando por la ROM y colocando a continuacin la RAM. 1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 8K8 de memoria ROM 4K8 de memoria RAM 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. Circuitos integrados ROM ROM =

N _ bits _ necesitados 8 K 8 = 4 _ circuitos _ ROM = 2K 8 N _ bits _ por _ CI N _ bits _ necesitados 4 K 8 = 2 _ circuitos _ RAM Circuitos integrados RAM RAM = = 2K 8 N _ bits _ por _ CI

IC0 (2K8) IC1 (2K8) IC2 (2K8) IC3 (2K8) IC4 (2K8) IC5 (2K8) Libre Libre

3. Construir el mapa de memoria. ROM ROM ROM ROM RAM RAM

Pgina 1

Diseo de mapas de memoria

4. Determinar el tamao de pgina y disear la tabla de direcciones y ocupacin de cada circuito integrado. � Determinaremos los bits del bus de direcciones en funcin del tamao total de la memoria:

8K _ ROM + 4 K _ RAM = 12 K

213 = 8192bytes 2 = 16384bytes

14

214 = 16384bytes

bus de direcciones A0..A13

bus de datos D0..D7 � El tamao de pgina en este caso ser de 2K ya que todos los circuitos integrados son de 2K

211 = 2048bytes

�

A0..A10

3

A11, A12, A13 2 = 8 pginas de las Bits de seleccin de pgina A11 A13 cuales las 6 primeras se usan por los circuitos integrados y las dos ltimas quedan libres. Tabla de direcciones

Selec. Pgina Agrup hexadecim. A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 Dir hexadec. $0000 $07FF $0800 $0FFF $1000 $17FF $1800 $1FFF $2000 $27FF $2800 $2FFF Cir. Integrado

IC0 IC1 IC2 IC3 IC4 IC5

5. Determinar la circuitera auxiliar necesaria para el control del circuito.

Como se puede observar el nmero de pginas es de 6, pero el mnimo que podemos controlar es de 8, es por lo que necesitaremos un decodificador de 3 a 8, de forma que las lneas del bus de direcciones del sistema A11, A12 Y A13 se conectarn a las entradas I0, I1 e I2 respectivamente y cada una de las salidas de O0 a O5 se conectarn a los Chip Select (CS) de cada los circuitos integrados de IC0 a IC5.

Pgina 2

Diseo de mapas de memoria

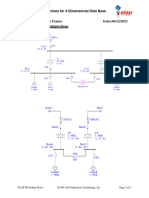

6. Dibujar el circuito completo de la memoria.

MEMORIA DE 8Kx8 DE ROM Y 4Kx8 DE RAM

D[0..7]

U1 36 1 2 5 6 9 8 7 10 11 29 33 39 35 RST-IN X1 X2 SID TRAP RST 5.5 RST 6.5 RST 7.5 INTR INTA S0 S1 HOLD READY 8085 ALE W\R\ R\D\ IO/M\ RST-OT CLKO SOD HLDA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 12 13 14 15 16 17 18 19 21 22 23 24 25 26 27 28 30 31 32 34 3 37 4 38

A8 A9 A10 A11 A12 A13 A14 A15

D0 D1 D2 D3 D4 D5 D6 D7

3 4 7 8 13 14 17 18 11 1

U3

D1 D2 D3 D4 D5 D6 D7 D8 CLK CLR

Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

2 5 6 9 12 15 16 19

A0 A1 A2 A3 A4 A5 A6 A7

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

IC0

8 7 6 5 4 3 2 1 23 22 19 18 20 21 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O\E\ VPP O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19

18 20 21

IC1 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O\E\ VPP O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19

18 20 21

IC2 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O\E\ VPP O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

74ABT273

ROM

ROM

ROM

A11 A12 A13

1 2 3 6 4 5

U4

A B C G1 G2A G2B

74F138

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

15 14 13 12 11 10 9 7

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

IC3 8 7 6 5 4 3 2 1 23 22 19 18 20 21 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O\E\ VPP

IC3

O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19

18 20 21

IC4

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

A0 8 A1 7 A2 6 A3 5 A4 4 A5 3 A6 2 A7 1 A8 23 A9 22 A10 19

18 20 21

IC5

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 C\E\ O0 O1 O2 O3 O4 O5 O6 O7 9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

ROM

RAM

RAM

R/W\

R/W\

A[0..15]

Pgina 3

Diseo de mapas de memoria

� Disear el mapa de memoria de un sistema basado en microprocesador para el 8085 de INTEL (A0..A15, D0..D7), suponiendo que se necesitan 8K8 de memoria ROM, 1K8 de memoria RAM y 2 entrada/salida de 8 bits en el bus de direcciones. Se disponen de circuitos integrados ROM de 8K1, circuitos integrados RAM de 1K4 y de las correspondientes entrada/salida y que la memoria est situada a partir de la direccin $0 empezando por la ROM, colocando a continuacin la RAM y por litimo las entradas/salidas 1. Detallar las necesidades del sistema en cuanto a direccionamiento, anchura de palabra y tipo de memoria a utilizar (RAM/ROM). 8K8 de memoria ROM 1K8 de memoria RAM 2 entrada/salida 2. Determinar los circuitos integrados de que se dispone, tanto en longitud como en anchura de palabras y definir los que se necesitan. Circuitos integrados ROM

N _ bits _ necesitados 8K 8 = = 8 _ circuitos _ ROM N _ bits _ por _ CI 8K 1 Circuitos integrados RAM RAM = N _ bits _ necesitados = 1K 8 = 2 _ circuitos _ RAM N _ bits _ por _ CI 1K 4 ROM =

3. Construir el mapa de memoria.

ICO

IC1

IC2

IC3

IC4

IC5

IC6

IC7

ROM (8K*8) RAM (1K*8) (E/S) (E/S)

IC8 IC10 (E/S) IC11 (E/S)

IC9

4. Determinar el tamao de pgina y disear la tabla de direcciones y ocupacin de cada circuito integrado. � Determinaremos los bits del bus de direcciones en funcin del tamao total de la memoria:

8 K _ ROM + 1K _ RAM + 2 K _ E / S = 11K

213 = 8192bytes 2 = 16384bytes

14

214 = 16384bytes

bus de direcciones A0..A13

bus de datos D0..D7 � El tamao de pgina en este caso ser de 1K ya que se puede elegir entre el tamao mayor (8K , el menor 256Bytes (E/S) o el intermedio (RAM de 1K). La circuitera menos complicada y con un aprovechamiento relativamente ptimo se consigue con el valor intermedio (1K).

210 = 1024bytes

�

A0..A9

A10, A11, A12, A13

Bits de seleccin de pgina A10 A13

2 4 = 16 pginas

de las

cuales las 11 primeras se usan por los circuitos integrados y las cinco ltimas quedan libres.

Pgina 4

Diseo de mapas de memoria

� Tabla de direcciones

Selec. Pgina Agrup hexadecim. A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 X X X X X X X X 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Dir hexadec. $0000 $1FFF $2000 $23FF $2400 $27FF $2800 $2BFF Cir. Integrado

IC0 a IC7 IC8 + IC9 IC10 IC11

5. Determinar la circuitera auxiliar necesaria para el control del circuito.

Como se puede observar el nmero de pginas es de 11, pero el mnimo que podemos controlar es de 16, es por lo que necesitaremos un decodificador de 4 a 16, de forma que las lneas del bus de direcciones del sistema A10, A11, A12 Y A13 se conectarn a las entradas I0, I1, I2 e I3 respectivamente y cada una de las salidas de O0 a O12 se conectarn a los Chip Select (CS) de cada los circuitos integrados de IC0 a IC11, teniendo en cuenta que como la ROM de 8Kx8 ocupa 8 pginas se debern conectar las 8 primeras salidas a una puerta AND que conectar su salida al CS del integrado ROM.

Pgina 5

Diseo de mapas de memoria

6. Dibujar el circuito completo de la memoria.

MEMORIA DE 8Kx8 DE ROM, 1Kx8 DE RAM Y 2 E/S

D[0..7]

U1 36 1 2 5 6 9 8 7 10 11 29 33 39 35 RST-IN X1 X2 SID TRAP RST 5.5 RST 6.5 RST 7.5 INTR INTA S0 S1 HOLD READY 8085 ALE W\R\ R\D\ IO/M\ RST-OT CLKO SOD HLDA AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 12 13 14 15 16 17 18 19 21 22 23 24 25 26 27 28 30 31 32 34 3 37 4 38

A8 A9 A10 A11 A12 A13 A14 A15

D0 D1 D2 D3 D4 D5 D6 D7

3 4 7 8 13 14 17 18 11 1

U3

D1 D2 D3 D4 D5 D6 D7 D8 CLK CLR

Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8

2 5 6 9 12 15 16 19

A0 A1 A2 A3 A4 A5 A6 A7

A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21

A11 23 A12 2 20 22

IC0 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D0

A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21

A11 23 A12 2 20 22

IC1 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D1

A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21

A11 23 A12 2 20 22

IC2 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11 D2

A0 10 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A8 25 A9 24 A10 21

A11 23 A12 2 20 22

IC3 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D3

74ABT273

A10 A11 A12 A13 .

2 3 21 22 1 23

U8

D1 D2 D3 D4 ST INH

S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15

11 9 10 8 7 6 5 4 18 17 20 19 14 13 16 15

1 2 3 4 5 6 11 12

U9

A010 A1 9 A2 8 A3 7 A4 6 A5 5 A7 3 A825 A924 A10 21

A11 23 A12 2 20 22 4

IC4 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D4

5430

A010 A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21

A11 23 A12 2 20 22

IC5 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D5

10 9 8 7 6 5 4 3 25 24 21 A11 23 2 A12 20 22

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

IC6 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D6

A1 9 A2 8 A3 7 A4 6 A5 5 A6 4 A7 3 A825 A924 A10 21

A1123 A12 2 20 22

10

IC7 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 CE OE ROM 8K*1 O0

11

D7

74HC4515

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9

8 7 6 5 4 3 2 1 23 22 18 20

IC8 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 CE R/W RAM 1K*8 O0 O1 O2 O3

9 10 11 13

D0 D1 D2 D3

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9

8 7 6 5 4 3 2 1 23 22 18 20

IC9 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 CE R/W RAM 1K*8 O0 O1 O2 O3

9 10 11 13

D4 D5 D6 D7

A0 A1 A2 A3 A4 A5 A6 A7

8 7 6 5 4 3 2 1

IC10 A0 A1 A2 A3 A4 A5 A6 A7 O0 O1 O2 O3 O4 O5 O6 O7

9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

A0 A1 A2 A3 A4 A5 A6 A7

8 7 6 5 4 3 2 1

IC11 A0 A1 A2 A3 A4 A5 A6 A7 O0 O1 O2 O3 O4 O5 O6 O7

9 10 11 13 14 15 16 17

D0 D1 D2 D3 D4 D5 D6 D7

18 20

CE R/W 8255

18 20

CE R/W 8255

A[0..15]

Pgina 6

Diseo de mapas de memoria

2.- Supngase una memoria RAM de 1024 palabras 16 bits/palabra construida empleando circuitos integrados de memoria RAM de 128 palabras 8 bits/palabra. A fin de permitir el direccionamiento de las palabras de la memoria, el bus de direcciones: A) Tiene 10 lneas, 7 de ellas comunes a todos los mdulos. B) Tiene 10 lneas, 3 de ellas comunes a todos los mdulos. C) Tiene 10 lneas, todas ellas comunes a todos los mdulos. D) Ninguna de las anteriores es verdadera.

1 semana

3.- Se considera un procesador que dispone de 12 lneas de direcciones A11-A0. Para la construccin de su unidad de memoria se dispone de mdulos de 2K palabras, utilizndose la lnea A1 para la seleccin de cada mdulo (A0 es la lnea menos significativa). Indique cul de las siguientes afirmaciones es verdadera: A) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en el mismo mdulo de memoria. B) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en diferentes mdulos de memoria. C) El mdulo en que se encuentra almacenada una direccin de memoria queda determinado por el valor de A10. D) Ninguna de las anteriores es verdadera.

7.- Se considera un procesador que dispone de 12 lneas de direcciones A11-A0. Para la construccin de su unidad de memoria se dispone de mdulos de 1K palabras, utilizndose las lneas menos significativas (A1-A0) para la seleccin de cada mdulo. Indique cul de las siguientes afirmaciones es verdadera: A) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en el mismo mdulo de memoria. B) Las direcciones hexadecimales C89 y C8A se encuentran almacenadas en diferentes mdulos de memoria. C) El mdulo en que se encuentra almacenada una direccin de memoria queda determinado por el valor de D) Ninguna de las anteriores es verdadera.

2.- Un computador con 13 lneas de direcciones tiene una memoria de 3211 palabras y utiliza entrada/salida localizada en memoria. Cul es el nmero mximo de perifricos que pueden conectarse, suponiendo que cada uno de ellos utiliza 16 direcciones? A) 211. B) 27 C) 2. D) Ninguna de las anteriores.

Junio del 2000 2 Semana

8.- Se considera un procesador que dispone de 12 lneas de direcciones A11-A0. Para la construccin de su unidad de memoria se dispone de mdulos de 1K palabras, utilizndose las lneas ms significativas (A11-A10) para la seleccin de cada mdulo. En el mapa de memoria, la direccin base (primera direccin de cada mdulo) en notacin hexadecimal de los sucesivos bloques de memoria es: Solucin: $00 $400 $800 y $C00

Septiembre del 2003

6.- Se quiere disear una memoria para un computador que tiene una arquitectura basada en palabras de 16 bits y un bus de direcciones de 20 lneas de manera que disponga de 500 Kpalabras de memoria RAM y 240 Kpalabras de memoria ROM. Sabiendo que se disponen de mdulos de memoria RAM de 128 Kpalabras x 8 bits/palabra, 128 Kpalabras x 16 bits/palabra; y de mdulos de memoria ROM de 128 Kpalabras x 8 bits/palabra, 128 Kpalabras x 16 bits/palabra, I. Si es posible realizar el diseo que se solicita. II. El menor nmero de mdulos necesarios para realizar el circuito con las especificaciones requeridas es 4 mdulos RAM de 128 Kpalabras x 16 bits/palabra y 2 mdulos ROM de 128 Kpalabras x 16 bits/palabra. A) I si, II si B) I: si, II no C) I no, II si D) I no, II no

Pgina 7

Diseo de mapas de memoria

Pgina 8

También podría gustarte

- Simulación de circuitos electrónicos con OrCAD® PSpice®De EverandSimulación de circuitos electrónicos con OrCAD® PSpice®Aún no hay calificaciones

- Iniciación al diseño de circuitos impresos con Altium DesignerDe EverandIniciación al diseño de circuitos impresos con Altium DesignerAún no hay calificaciones

- Deber No1 Segundo ParcialDocumento4 páginasDeber No1 Segundo ParcialPablo Villavicencio0% (2)

- Banco de MemoriaDocumento28 páginasBanco de MemoriaLa Torre Paul100% (1)

- Ejerciciosleccion 8Documento11 páginasEjerciciosleccion 8samuelgvAún no hay calificaciones

- Ej T5Ftos SolucionesDocumento23 páginasEj T5Ftos SolucionesCristhian CjAún no hay calificaciones

- Conferencia No. 4Documento19 páginasConferencia No. 4steven somarribaAún no hay calificaciones

- Trabajo Practico de Aula #1 (2012) - AlanDocumento23 páginasTrabajo Practico de Aula #1 (2012) - AlanRaul AsisAún no hay calificaciones

- Ejercicio 1Documento4 páginasEjercicio 1Luis Miguel BarrenoAún no hay calificaciones

- Ejercicios RAMDocumento11 páginasEjercicios RAMSergio AramayoAún no hay calificaciones

- EC1ProblemasMEMORIAS 0708Documento9 páginasEC1ProblemasMEMORIAS 0708Darku Dark Dark100% (1)

- Clase Practica No2 MicroprocesadoresDocumento11 páginasClase Practica No2 MicroprocesadoresJose Euclides Rocha SolanoAún no hay calificaciones

- Control Externo DecodificadorDocumento7 páginasControl Externo DecodificadorPablo ObesoAún no hay calificaciones

- Mapas de MemoriasDocumento36 páginasMapas de MemoriasgoddaaaaaAún no hay calificaciones

- 14 La Memoria y El z80Documento15 páginas14 La Memoria y El z80Anonymous qTKCWlxAún no hay calificaciones

- Lab OratorioDocumento3 páginasLab OratorioAlexis MorochoAún no hay calificaciones

- Clase Practica - Unidad IiDocumento3 páginasClase Practica - Unidad IiAder Hariel Treminio MontoyaAún no hay calificaciones

- Mapa de Memorias - Ing. Jhon PilataxiDocumento5 páginasMapa de Memorias - Ing. Jhon PilataxiJhon PilataxiAún no hay calificaciones

- Lab04 As 1it-141 DcdeDocumento7 páginasLab04 As 1it-141 DcdeAngelica StanziolaAún no hay calificaciones

- S06 ITEC1304A TipoMemoriaDocumento25 páginasS06 ITEC1304A TipoMemoriaAdrian Rafael CanalesAún no hay calificaciones

- Lab 8 Memorias 2013 2Documento3 páginasLab 8 Memorias 2013 2juanjo20_11Aún no hay calificaciones

- Interfaz MemoriasDocumento7 páginasInterfaz MemoriasErick Jesús Rodríguez DávilaAún no hay calificaciones

- Examen Final II Arquitectura ComputadorasDocumento11 páginasExamen Final II Arquitectura ComputadorasHector ChecasovichAún no hay calificaciones

- Ejercicios T5 (2022-23 Q1) DSBM UPCDocumento327 páginasEjercicios T5 (2022-23 Q1) DSBM UPCMain YasuoAún no hay calificaciones

- Monografia Proyecto SistemasDocumento15 páginasMonografia Proyecto SistemasPercy Vicente LeivaAún no hay calificaciones

- Tarea 02 de Circuitos Digitales II 2018-II (Unmsm)Documento7 páginasTarea 02 de Circuitos Digitales II 2018-II (Unmsm)walterAún no hay calificaciones

- Pantallas LCDDocumento22 páginasPantallas LCDIrcarod Zurk DivadAún no hay calificaciones

- Lab 8 Memorias 2016 2Documento4 páginasLab 8 Memorias 2016 2Vanessa VásquezAún no hay calificaciones

- Ejercicio - Instrucciones de TransferenciaDocumento17 páginasEjercicio - Instrucciones de Transferenciagusti072Aún no hay calificaciones

- ASM 68kDocumento26 páginasASM 68kRomell Ap LanAún no hay calificaciones

- Pinout de ROM de Máscara - NESdev WikiDocumento5 páginasPinout de ROM de Máscara - NESdev WikiJoséAún no hay calificaciones

- Banco 8088 y 8086Documento12 páginasBanco 8088 y 8086Brayhan Torres100% (1)

- Chips de Entrada y de SalidaDocumento15 páginasChips de Entrada y de SalidaLuis Jorge Lozano Domínguez100% (1)

- Examen No3 (Práctico)Documento8 páginasExamen No3 (Práctico)Jaime JdAún no hay calificaciones

- Ecbol4 PDFDocumento7 páginasEcbol4 PDFFerdy Casaverde LopezAún no hay calificaciones

- Practica Memoria RomDocumento12 páginasPractica Memoria RomSaid HadadAún no hay calificaciones

- Practica 2Documento2 páginasPractica 2Weymar Ronhaldo Ventura MarcaAún no hay calificaciones

- Ejercicios Con PLDDocumento2 páginasEjercicios Con PLDCeliina Narumii Román HigaAún no hay calificaciones

- Reporte 2Documento6 páginasReporte 2Eduardo NAún no hay calificaciones

- Problemas Mapas SOLDocumento16 páginasProblemas Mapas SOLNoelia Guerrero ÁlvarezAún no hay calificaciones

- Cap 8 - Acoplamiento - Diseño CompletoDocumento24 páginasCap 8 - Acoplamiento - Diseño CompletoGuidoAún no hay calificaciones

- Memorias 2 PDFDocumento23 páginasMemorias 2 PDFElifio MirandaAún no hay calificaciones

- Construccion de Un PLC Con Pic Saber ElectronicaDocumento14 páginasConstruccion de Un PLC Con Pic Saber ElectronicaJuancito Apaza Maraza100% (1)

- Memoria Eeprom 28c64Documento12 páginasMemoria Eeprom 28c64Joel AlconAún no hay calificaciones

- Boletines Edc Isw 2023 24Documento26 páginasBoletines Edc Isw 2023 24kinturbo 66Aún no hay calificaciones

- 02 Decodificadores de Memoria y PerifericosDocumento16 páginas02 Decodificadores de Memoria y PerifericosJunior TB100% (1)

- Informe RamDocumento9 páginasInforme RamStalinCazaAún no hay calificaciones

- Actividades Tema 2Documento8 páginasActividades Tema 2mari5525Aún no hay calificaciones

- Trabajo Práctico Nro 2: Mapeo - DecodificaciónDocumento6 páginasTrabajo Práctico Nro 2: Mapeo - DecodificaciónDiego Garcia Pacheco100% (1)

- Maquinas de Estado Alarcon MatuttiDocumento10 páginasMaquinas de Estado Alarcon MatuttiRogerEspinoza87Aún no hay calificaciones

- CapacidadDocumento14 páginasCapacidadAlíanLeltSwnMAún no hay calificaciones

- Diseno de Bloques de MemoriaDocumento9 páginasDiseno de Bloques de MemoriaIsmael ChoixAún no hay calificaciones

- Guia de Clase 1 - Lectura y ProgramacionDocumento52 páginasGuia de Clase 1 - Lectura y ProgramacionPedro DiazAún no hay calificaciones

- Memoria y PLDDocumento10 páginasMemoria y PLDRoberto Hipolito LomaAún no hay calificaciones

- UntitledDocumento2 páginasUntitledINGRID LISSETH DE PAZ CASTAÑEDAAún no hay calificaciones

- Tarea 1 Sistemas DigitalesDocumento2 páginasTarea 1 Sistemas DigitalesAlejandro RodriguezAún no hay calificaciones

- Display de Cristal Liquido (LCD) : Pampas - 2015Documento12 páginasDisplay de Cristal Liquido (LCD) : Pampas - 2015vidAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Inspección óptica automatizada: Avances en la tecnología de visión por computadoraDe EverandInspección óptica automatizada: Avances en la tecnología de visión por computadoraAún no hay calificaciones

- Gráficos rasterizados: Comprender los fundamentos de los gráficos rasterizados en visión por computadoraDe EverandGráficos rasterizados: Comprender los fundamentos de los gráficos rasterizados en visión por computadoraAún no hay calificaciones

- Etiquetas Aire Dividido Gtronic ModDocumento3 páginasEtiquetas Aire Dividido Gtronic Modoesnes.contingenciartAún no hay calificaciones

- Laboratorio de Circuitos Electricos 2 N6Documento23 páginasLaboratorio de Circuitos Electricos 2 N6xd S:Aún no hay calificaciones

- Radiaciones ElectromagnéticasDocumento12 páginasRadiaciones ElectromagnéticasGissel LeonAún no hay calificaciones

- Grundfosliterature 3207416Documento26 páginasGrundfosliterature 3207416GamberiniAún no hay calificaciones

- Clase 7Documento10 páginasClase 7Jerson absalon Chicana menaAún no hay calificaciones

- 18a Celdas ElectroquímicasDocumento5 páginas18a Celdas ElectroquímicasAdriana TejadaAún no hay calificaciones

- Análisis de Fallas POWER WORLDDocumento4 páginasAnálisis de Fallas POWER WORLDJoséDavidAbrilBaño100% (1)

- Informe Descriptivo INTELSIDocumento19 páginasInforme Descriptivo INTELSIRonal Rojas AranaAún no hay calificaciones

- Dahua Distribuidor Marzo 2018Documento35 páginasDahua Distribuidor Marzo 2018pepejuan2Aún no hay calificaciones

- Pulsador de InyectoresDocumento4 páginasPulsador de InyectoresAlejandro Marcial Lucio0% (1)

- NORMAS de Referencia InternetDocumento4 páginasNORMAS de Referencia InternetMartin Quito AriasAún no hay calificaciones

- Actividades HC250Documento9 páginasActividades HC250Jonathan Giròn BolivarAún no hay calificaciones

- PRÁCTICA 4 Campo Eléctrico y Superficies Equipotenciales - ReporteDocumento7 páginasPRÁCTICA 4 Campo Eléctrico y Superficies Equipotenciales - ReporteFernanda DelgadoAún no hay calificaciones

- PTS-MIN-020 Aislación y BloqueoDocumento13 páginasPTS-MIN-020 Aislación y BloqueoElizabethAún no hay calificaciones

- Práctica 5 - CarlosAnguianoDocumento5 páginasPráctica 5 - CarlosAnguianoCarlos AnguianoAún no hay calificaciones

- Electronica Analogica Lab 6Documento14 páginasElectronica Analogica Lab 6Luis Diego Cuzcano RomoAún no hay calificaciones

- Térmica de Circuitos Contra Sobrecargas Breakers 104/105/106 - ..Documento5 páginasTérmica de Circuitos Contra Sobrecargas Breakers 104/105/106 - ..Anonymous OgrzO6Aún no hay calificaciones

- QUIZ 1 Ccna 1Documento13 páginasQUIZ 1 Ccna 1jpardiniAún no hay calificaciones

- Ejercicios Tema 4Documento8 páginasEjercicios Tema 4Salvador Morales BecillaAún no hay calificaciones

- LAb 08 Etap Flujo de Potencia Mendoza Jean FrancoDocumento8 páginasLAb 08 Etap Flujo de Potencia Mendoza Jean FrancoJean Franco Mendoza ZamoraAún no hay calificaciones

- 03 Taller - Yeikob BermúdezDocumento9 páginas03 Taller - Yeikob BermúdezSteven BermudezAún no hay calificaciones

- Consulta - Schuberth VillacresesDocumento6 páginasConsulta - Schuberth VillacresesschuberthjoseAún no hay calificaciones

- 01 T1 ExtraDocumento3 páginas01 T1 ExtraAlberto OcampoAún no hay calificaciones

- SPL 0159Documento108 páginasSPL 0159Jorge Eduardo Cerda OrtizAún no hay calificaciones

- Lab 4Documento8 páginasLab 4sebastianAún no hay calificaciones

- Lab 6 PDSDocumento6 páginasLab 6 PDSmis_apuntesAún no hay calificaciones

- Manual Del Equipo TTCapacitivosDocumento8 páginasManual Del Equipo TTCapacitivosJONATHAN GARY DE LA CRUZ DE LA CRUZAún no hay calificaciones

- Amplificadores OperacionalesDocumento19 páginasAmplificadores OperacionalesAlejandro GilAún no hay calificaciones

- Memoria Instalacion ElectricaDocumento11 páginasMemoria Instalacion Electricavp h1Aún no hay calificaciones

- CronogramaDocumento2 páginasCronogramaAlejandro LeonAún no hay calificaciones