Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Diseño Combinacional de Bajo Consumo

Diseño Combinacional de Bajo Consumo

Cargado por

Raul MaldonadoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Diseño Combinacional de Bajo Consumo

Diseño Combinacional de Bajo Consumo

Cargado por

Raul MaldonadoCopyright:

Formatos disponibles

7.

Diseño de circuitos CMOS de baja potencia

Diseño de Circuitos Digitales para Comunicaciones

Disipación de Calor en los μP

Diseño de Circuitos Digitales para Comunicaciones

Evolución de la densidad de potencia

Diseño de Circuitos Digitales para Comunicaciones

Disipación de potencia en circuitos CMOS

. Consumo de potencia dinámica:

Carga y descarga de las capacidades

. Corrientes en corto circuito:

Durante la conmutación hay un camino de corriente

entre VDD y GND.

. Fugas:

Corrientes de fuga de diodos y transistores

Diseño de Circuitos Digitales para Comunicaciones

Consumo de potencia dinámica

Vdd

Vin Vout

CL

Energy/transition = CL * Vdd2 Ciclo completo: L → H, H → L

Power = Energy/transition * f = CL * Vdd2 * f

Not a function of transistor sizes!

Need to reduce CL , Vdd, and f to reduce power.

Diseño de Circuitos Digitales para Comunicaciones

Consumo de Potencia Dinámica

Power = Energy/transition * transition rate

= CL * Vdd2 * f01

= CL * Vdd2 * P01* f

= CEFF * Vdd2 * f

Power Dissipation is Data Dependent

Function of Switching Activity , f 0 → 1

CEFF = Effective Capacitance = CL * P01

Diseño de Circuitos Digitales para Comunicaciones

El consumo de potencia depende de los datos

Example: Static 2 Input NOR Gate

Assume:

P(A=1) = 1/2

P(B=1) = 1/2

Then:

P(Out=1) = 1/4

P(0 1)

= P(Out=0).P(Out=1)

= 3/4 1/4 = 3/16

CEFF = 3/16 * CL

Diseño de Circuitos Digitales para Comunicaciones

Probabilidades de transición de puertas básicas

= (1 – P1) P1 = (1 – P0) P0

Diseño de Circuitos Digitales para Comunicaciones

Probabilidad de transición de la puerta NOR de 2 entradas

Diseño de Circuitos Digitales para Comunicaciones

Circuitos dinámicos

VDD

Mp

Out

In1

In2 PDN

In3

Me

Power is Only Dissipated when Out=0!

CEFF = P(Out=0).CL

Diseño de Circuitos Digitales para Comunicaciones

NOR dinámica de 2 entradas

Example: Dynamic 2 Input NOR Gate

Assume:

P(A=1) = 1/2

P(B=1) = 1/2

Then:

P(Out=0) = 3/4

CEFF = 3/4 * CL

Switching Activity Is Always Higher in Dynamic Circuits

Diseño de Circuitos Digitales para Comunicaciones

Probabilidad de transición de puertas dinámicas

P(out = 0)

Switching Activity for Precharged Dynamic Gates

P01 = P0

Diseño de Circuitos Digitales para Comunicaciones

Carreras en circuitos CMOS estáticos

also called: dynamic hazards

A X A: 1 → 0

B

B: 0 → 0

Z

C C: 1 → 0 Instantáneamente

X: 0 → 1 Tras un retardo

ABC 101 000

X

. X = 0, C = 0 → Z = 1 espurio

Z . X = 1, C = 0 → Z = 0

Unit Delay

Observe: No glitching in dynamic circuits

Diseño de Circuitos Digitales para Comunicaciones

Cadena de puertas NAND

out1 out2 out3 out4 out5

1

...

6.0

out8

4.0 out6

out4

V (Volt)

out2

2.0

out1

out3

out5

out7

0.0

0 1 2 3

t (nsec)

Diseño de Circuitos Digitales para Comunicaciones

Circuito sumador

Cin Add0 Add1 Add2 Add14 Add15

S0 S1 S2 S14 S15

Sum Output Voltage, Volts

4.0 4

S15

6

2.0 3

S10

Cin

5

S1

2

0.0

0 5 10

Time, ns

Diseño de Circuitos Digitales para Comunicaciones

Soluciones para evitar las carreras

0

F1 0

1 F1 1

F2 0

0 2

F3

0 F3

0

0 F2 1

0

Equalize Lengths of Timing Paths Through Design

Diseño de Circuitos Digitales para Comunicaciones

Corriente en cortocircuito (sólo en lógica estática)

Vdd

Energía consumida por período de conmutación:

Vin Vout

I picot r I picot f tr t f

E dp ( )VDD VDD I pico

CL 2 2 2

0.15

0.10

IVDD (mA)

0.05

0.0 1.0 2.0 3.0 4.0 5.0

Vin (V)

Diseño de Circuitos Digitales para Comunicaciones

Influencia de los tiempos de subida y bajada sobre la

corriente en cortocircuito

VDD VDD

ISC ISC IMAX

Vout Vout

Vin Vin

CL Vout CL

P lineal (a)

P saturación (b)

(a)Large capacitive load Vin (b) Small capacitive load

El peor caso

Psc mínima: tr/f salida >> tr/f entrada : Solución local

Diseño de Circuitos Digitales para Comunicaciones

La energía en cortocircuito en función de la relación

de pendientes

E / E W/L|P = 7.2 m/1.2 m

W/L|N = 2.4 m/1.2m

8 VDD = 5 V

7

6

5 r = (tr/f │input) / (tr/f │output)

4

3 r = 1, Psc = 10 % Pdin

2 VDD = 3.3 V

VDD↓ → Psc↓

1

0 r

0 1 2 3 4 5 Si VDD < Vtn + │Vtp│, Psc = 0

(a) CL >> (b) CL <<

The power dissipation due to short circuit currents is

minimized by matching the

rise/fall times of the input and output signals.

Diseño de Circuitos Digitales para Comunicaciones

Consumo de potencia estática

Lógica pseudo-NMOS

Vdd

Istat

Vout

CL

Vin=5V

Pstat = P(In=1).Vdd . Istat

• Dominates over dynamic consumption

• Not a function of switching frequency

Diseño de Circuitos Digitales para Comunicaciones

Corriente de fugas

Vdd

Vout

Drain Junction

Leakage

Sub-Threshold

Current

Sub-Threshold Current Dominant Factor

Pstat = Istat * VDD

Diseño de Circuitos Digitales para Comunicaciones

Corriente sub-umbral

ID

Si VT ↓ → ID (VGS =0) ↑

│VT│ > 0.5 – 0.6 V

VT =0.2 VT =0.6 VGS

Lower Bound on Threshold to Prevent Leakage

Diseño de Circuitos Digitales para Comunicaciones

Análisis del consumo de potencia mediante SPICE

Circuito integrador cuya salida es la potencia media, Vout = Pav

VDD Pav

C

i DD

+ Circuit k iDD R

- Under Test

Equivalent Circuit for Measuring Power in SPICE

1 T VDD T

T 0 T 0

Pav P (t ) dt i DD (t )dt

k/C = VDD/T

Diseño de Circuitos Digitales para Comunicaciones

Diseño para el peor caso

V DD

VDD

1 1 B 4

A A 2

B

F C 4

2 CL

B D 2

F

2 A 2

D 1

A

B 2C 2

Here it is assumed that Rp = Rn

Diseño de Circuitos Digitales para Comunicaciones

Potencia = CL*VDD2*P 0→1*f = CEFF*VDD2*f. Si f

1.- Reducción de VDD es constante, la potencia disminuye si:

1.- VDD disminuye

2.- CEFF disminuye

2.a.- Capacidad física

2.b.- Actividad de conmutación

1.5

NORMALIZED POWER-DELAY PRODUCT

1.00 P x td = E t = CL * Vdd 2

0.70

0.50

0.30

0.20

E(Vdd=2) (CL) * (2)2

0.15 quadratic dependence =

E(Vdd=5) (CL) * (5)2

0.1

51 stage ring oscillator

0.07

E(Vdd=2) 0.16 E(Vdd =5)

0.05

8-bit adder

0.03

1 2 5

Vdd (volts)

Strong function of voltage (V 2 dependence).

Relatively independent of logic function and style.

Power Delay Product Improves with lowering VDD.

Diseño de Circuitos Digitales para Comunicaciones

La disminución de Vdd aumenta el retardo

7.50 multiplier

7.00

clock generator

2.0m technology CL * Vdd

6.50 Td =

6.00

I

NORMALIZED DELAY

5.50

5.00

4.50 I ~ (Vdd - Vt)2

4.00

3.50

ring oscillator

3.00

2.50

Td(Vdd=2) (2) * (5 - 0.7)2

microcoded DSP chip =

2.00 Td(Vdd=5) (5) * (2 - 0.7)2 VT = 0.7 V

1.50 adder

1.00 adder (SPICE) 4

2.00 4.00 6.00

V dd (volts)

v2 1

t p CL dv

Relatively independent of logic function and style. 0 i (v )

56 – 44000 transistores

VDD↓ → PDP↓ pero tp↑

Diseño de Circuitos Digitales para Comunicaciones

Disminución de la tensión umbral

Delay I

D

2V t Vdd Vt = 0 Vt = 0.2 VGS

Reduces the Speed Loss, But Increases Leakage

C LVDD 1 1

tp ( )

2 K n (VDD VTN ) 2 K (V V 2

p DD Tp

Interesting Design Approach:

DESIGN FOR PLeakage == PDynamic

Diseño de Circuitos Digitales para Comunicaciones

2.a.-Disminución de la capacidad física: dimensionamiento

de los transistores

Lower Capacitance (*) Higher Voltage

Small W/L’s

Large W/L’s

Higher Capacitance (*) Lower Voltage

CL 1 1

(*) Para mantener la velocidad constante: t p ( )

2VDD K n K p

Larger sized devices are useful only when interconnect dominated.

Minimum sized devices are usually optimal for low-power.

Diseño de Circuitos Digitales para Comunicaciones

Dimensionamiento de los transistores

para minimizar el consumo de potencia

N = 1 (r ≡ referencia)

CL 1 1 C (1 ) 1 1

t p ,r ( ) int ( ) N

2VDD,r K n,r K p ,r 2VDD,r K n,r K p ,r

N

CL 1 1 C (N ) 1 1 CL

tp ( ) int ( )

2VDD K n K p 2VDD NKn,r NK p ,r

tp,r = tp CL = Cext + N Cint

→ 1 N N = Cint (N + α)

VDD VDD,r

VDD,r NVDD N (1 )

Ejemplo: N =3, α=2:

3 2 5

VDD VDD,r VDD,r

3(1 2) 9

(Si W ↑, VDD ↓)

Diseño de Circuitos Digitales para Comunicaciones

Energía normalizada

CL = Cint (N + α) ,, CL,r = Cint (1 + α)

P td = E = CLVDD2

Er = CL,rVDD,r2 = Cint (1 + α)VDD,r2 CL,r

E = Cint(N + α)VDD2 = Cint (N + α) VDD,r2

(N )2 Cint (1 ) ( N )3 2

V

(1 ) 2 N 2 (1 ) (1 ) 2 N 2

DD, r

(N ) 3

E Er

(1 ) 3 N 2

dE dE E r d [( N ) 3 / N 2

Minimización de E: 0 0

dN dN (1 ) 3

dN

3(N+α)2N2 = 2N(N+α)3 ,, 3N = 2 (N+α) → N = 2α

Diseño de Circuitos Digitales para Comunicaciones

Dimensionamiento de los transistores

Cg = W/L CMIN

Sólo si α >1 (domina Cext) tiene sentido hacer transistores grandes

I W/L CMIN

CMIN = Minimum sized gate (W/L=1)

W /L after sizing

CP = Cwiring + CDF

Cext = Cr + C fanout = CP / (K CMIN) = Cext / Cint

CL= Cext + Cint

10

HIGH PERFORMANCE 7

=0

NORMALIZED ENERGY

5

W/L >> CP / (K C MIN) =α 4 CL = 0

3 = 0.5

LOW POWER 2

1.5 =1

W/L 2 CP / (K CMIN) = 2α

(if CP K CMIN) adder

1.0 = 1.5

ELSE W/L = 1 0.7 =2

tp constante → (W/L)↑, VDD ↓ 0.5

1 3 10

W/L

Diseño de Circuitos Digitales para Comunicaciones

Reducción de la capacidad efectiva

Global bus architecture Local bus architecture

Área vs. potencia

Shared Resources incur Switching Overhead

Diseño de Circuitos Digitales para Comunicaciones

2.b.- Reducción de la actividad de conmutación:

. Reordenamiento de señales

. Lógica estática mejor que lógica dinámica

• Reordenamiento de las señales:

P(A=1) = 0.5

A x P(B=1) = 0.2

1 P(C=1) = 0.1

B

Z

C

P0→1 (x) = (1-PAPB)PAPB = (1-0.5*0.2)(0.5*0.2) = 0.09

B x

2

C

Z

A

P0→1 (x) = (1-PBPC)PBPC = (1-0.2*0.1)(0.2*0.1) = 0.0196

Diseño de Circuitos Digitales para Comunicaciones

También podría gustarte

- Señales ProgramaciónDocumento11 páginasSeñales ProgramaciónJeniferAún no hay calificaciones

- Fms200904 Calculo de La Banda Transportadora 304 SPDocumento16 páginasFms200904 Calculo de La Banda Transportadora 304 SPFernando Omar ArenaAún no hay calificaciones

- Protocolos de Pruebas Fat y SatDocumento4 páginasProtocolos de Pruebas Fat y SatRaul Maldonado100% (2)

- MarlboroDocumento13 páginasMarlboroRaul MaldonadoAún no hay calificaciones

- Tabla Comparativa de Sensores y ActuadoresDocumento15 páginasTabla Comparativa de Sensores y ActuadoresRaul Maldonado100% (1)

- Tabla Comparativa de Sensores y ActuadoresDocumento15 páginasTabla Comparativa de Sensores y ActuadoresRaul Maldonado100% (1)

- GIGABYTE Presenta BRIX La PC Ultra Compacta VFDocumento6 páginasGIGABYTE Presenta BRIX La PC Ultra Compacta VFTecnología 21Aún no hay calificaciones

- Informe - Rectificador Trifasico de Onda CompletaDocumento5 páginasInforme - Rectificador Trifasico de Onda CompletaJhon TorresAún no hay calificaciones

- Antena y TiltDocumento31 páginasAntena y TiltElio Jose Aguilar RomeroAún no hay calificaciones

- Ensayo CPUDocumento4 páginasEnsayo CPUTatiana OrdoñezAún no hay calificaciones

- Ganancia Directiva Y Ganancia de PotenciaDocumento2 páginasGanancia Directiva Y Ganancia de PotenciaDani JdAún no hay calificaciones

- Int Dos y BiosDocumento28 páginasInt Dos y BiosDRYKKON100% (2)

- Circuitos Astables o AestablesDocumento5 páginasCircuitos Astables o AestablesJazmin LoveAún no hay calificaciones

- Fundamento Teorico Del Laboratorio 1Documento6 páginasFundamento Teorico Del Laboratorio 1Elvis Nelson Ventura QuispeAún no hay calificaciones

- Apuntes AVRDocumento9 páginasApuntes AVRirving_asAún no hay calificaciones

- Desempeño Del Sector de Telecomunicaciones, 1T2021Documento23 páginasDesempeño Del Sector de Telecomunicaciones, 1T2021Ale San11Aún no hay calificaciones

- Catalogo Actualizado 28 AgostoDocumento35 páginasCatalogo Actualizado 28 AgostofelipenintendofortniteAún no hay calificaciones

- Algunos Aspectos Técnicos de Las Comunicaciones de Socorro en Situaciones de CatástrofeDocumento85 páginasAlgunos Aspectos Técnicos de Las Comunicaciones de Socorro en Situaciones de CatástrofemenssesAún no hay calificaciones

- DMC-FZ5 Manual Spanish BirlarioDocumento116 páginasDMC-FZ5 Manual Spanish BirlarioMagdalena Marín CampillosAún no hay calificaciones

- Popular Transistors BALASTRODocumento6 páginasPopular Transistors BALASTROMechín Rodriguez EjvrAún no hay calificaciones

- Mi Experiencia de Ensamble de Equipo de ComputoDocumento6 páginasMi Experiencia de Ensamble de Equipo de ComputoYOHANA TORRESAún no hay calificaciones

- Informe 9 Labo Antenas.Documento27 páginasInforme 9 Labo Antenas.Abel Isaac Huaytalla CotrinaAún no hay calificaciones

- Fibra ÓpticaDocumento4 páginasFibra ÓpticaHugo ArizaAún no hay calificaciones

- Planificación de InformáticaDocumento10 páginasPlanificación de Informáticajuands16440% (1)

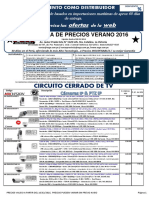

- Lista de Precios Sego Verano 2016Documento18 páginasLista de Precios Sego Verano 2016Jabath MárquezAún no hay calificaciones

- Arq de ComputadorasDocumento20 páginasArq de ComputadorasSamuel AguilarAún no hay calificaciones

- Preparatorio 13 Dario Orosco PDFDocumento3 páginasPreparatorio 13 Dario Orosco PDFDario OroscoAún no hay calificaciones

- 1 Redes Guia de Aprendizaje Tecnico SistemasDocumento3 páginas1 Redes Guia de Aprendizaje Tecnico SistemasCarlos Andres Loaiza RendonAún no hay calificaciones

- Gira JENEFFER BARBERANDocumento10 páginasGira JENEFFER BARBERANJeneffer Barberan MoreiraAún no hay calificaciones

- Componentes Del Sistema de Encendido ElectronicoDocumento20 páginasComponentes Del Sistema de Encendido ElectronicoZumel Garcia SebastiánAún no hay calificaciones

- 4 Microprocesador 8086Documento41 páginas4 Microprocesador 8086Carlos Rafael ContrerasAún no hay calificaciones

- Tarjeta Madre y Sus Tiposo FormatosDocumento18 páginasTarjeta Madre y Sus Tiposo FormatosFrancisco Javier Benavides ZuluagaAún no hay calificaciones

- Ejercicios Unidad 4Documento3 páginasEjercicios Unidad 4Madeline ReynosoAún no hay calificaciones

- Puente HDocumento12 páginasPuente HCuenta PersonalAún no hay calificaciones

- Estructura de Los PLCDocumento9 páginasEstructura de Los PLCTkozl BerghAún no hay calificaciones