Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Examen II 2021

Examen II 2021

Cargado por

jeaustin0 calificaciones0% encontró este documento útil (0 votos)

3 vistas8 páginasEste documento contiene un examen de Sistemas Operativos que consta de 50 preguntas de opción múltiple. El examen incluye preguntas sobre temas como paginación, memoria virtual, TLB, fragmentación interna, algoritmos de reemplazo, sincronización y problemas clásicos de concurrencia. Cada pregunta vale 2 puntos para un total de 100 puntos en el examen.

Descripción original:

Una

Título original

Examen_II_2021

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoEste documento contiene un examen de Sistemas Operativos que consta de 50 preguntas de opción múltiple. El examen incluye preguntas sobre temas como paginación, memoria virtual, TLB, fragmentación interna, algoritmos de reemplazo, sincronización y problemas clásicos de concurrencia. Cada pregunta vale 2 puntos para un total de 100 puntos en el examen.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

3 vistas8 páginasExamen II 2021

Examen II 2021

Cargado por

jeaustinEste documento contiene un examen de Sistemas Operativos que consta de 50 preguntas de opción múltiple. El examen incluye preguntas sobre temas como paginación, memoria virtual, TLB, fragmentación interna, algoritmos de reemplazo, sincronización y problemas clásicos de concurrencia. Cada pregunta vale 2 puntos para un total de 100 puntos en el examen.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 8

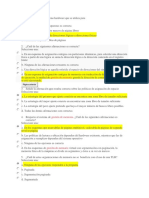

Examen II I Ciclo 2021

Sistemas Operativos Grupo Hora: ______

Nombre completo:________________________________ Cédula: _________________

Sección de respuestas:

1( )2( )3( )4( )5( )6( )7( )8( )9( )10( )11( )12( )13( )14( )15( )16( )17( )18( )19( )20( )

21( )22( )23( )24( )25( )26( )27( )28( )29( )30( )31( )32( )33( )34( )35( )36( )37( )38( )

39( )40( )41( )42( )43( )44( )45( )46( )47( )48( )49( )50( )

Son 50 preguntas de marcar con X, cada una vale 2 puntos

1. Si un Sistema Operativo pasa de usar 2. Cuando ha y un fallo de página se sube la

páginas de 4K a 18K: siguiente cantidad de páginas a la RAM:

a[ ] Disminuye la posibilidad de a[ X] La cantidad que hay en el sector

inanición del disco

b[ ] Mejora la Razón de Acierto b[ ] Una

c[ ] Produce menos Fragmentación c[ ] Las necesarias para subir el nuevo

Interna método

d[ X] Disminuye los fallos de página d[ ] Depende del tamaño del proceso

e[ ] Mejora el cambio de contexto e[ ] 32

3. El mapeo de direcciones lógicas a físicas 4. La localidad de referencia se refiere a:

se aligera mediante: a[ ] La paginación por demanda pura

a[ ] El uso de una TLB grande b[ X] Que los procesos usan mucho la

b[ ] La colaboración del paginador página recién referenciada

inteligente c[ ] El intercambio de páginas entre

c[ X ] La colaboración de la MMU TLB y RAM

d[ ] La localidad de referencia d[ ] Fallos de páginas innecesarios

e[ ] Un buen algoritmo de reemplazo e[ ] Al algoritmo de envejecimiento

5. El grado de multiprogramación se ve 6. Los cerrojos mutex representan la técnica

limitado por una cantidad constante de fundamental de sincronización usada en:

procesos cuando la administración de la a[ ] Round Robin

memoria se hace con b[ X ] Pthreads

a[ ] Memoria compartida c[ ] Bloqueos

b[ ] Bloques de tamaño variable d[ ] Colas

c[ ] Paginación e[ ] Semáforos

d[ ] Un paginador perezoso

e[X ] Bloques de tamaño fijo

7. El Algoritmo de reemplazo que usan los 8. En Windows y en Linux el tamaño de

SO actuales es: página es:

a[ a[

Envejecimiento 4096 bytes

X] X]

b[ ] Primera en entrar, primera en salir b[ ] Variable

(FIFO) c[ ] 3072 bytes

c[ ] No usada recientemente d[ ] 8 K

d[ ] Segunda oportunidad e[ ] 1024 bytes

e[ ] Menos usada recientemente

9. Una arquitectura garantiza una Razón de 10. La arquitectura A1 tiene una RA de 98%

Acierto de 80%, con 80ns para leer en y la A2 una RA de 80% ¿Cuál tiene mejor

RAM y 10ns en el TLB. El Tiempo TEA?:

Efectivo de Acceso es: a[ ] La A1

a[ ] 90 ns b[ ] La A2

b[ ] 20 ns c[ Depende de los tiempos de acceso a

c[ X] RAM y TLB

106 ns

X] d[ ] Depende tamaño del TLB

d[ ] 100 ns e[ ] Depende del algoritmo de

e[ ] 122 ns Envejecimiento

11. Peor Ajuste genera más Fragmentación 12. Uno de los objetivos de las memorias

Interna debido a que: caché consiste en:

a[ ] Los bloques son de tamaño a[ ] Mejorar el tiempo de acceso al TLB

variable b[ Reducir el tiempo de transferencia

b[ ] Los bloques son de tamaño fijo X] entre dos componentes

c[ ] Favorece a los procesos pequeños c[ ] Aumentar la cantidad de procesos

d[ ] Los bloques nunca se dividen en la cola de listos

e[ Los bloques están ordenados del d[ ] Reducir el tiempo de ejecución del

X] más grande al más pequeño Cambio de Contexto

e[ ] Completar el Quantum

13. Un sistema operativo con páginas muy 14. Una arquitectura con dos TLB tiene la

grandes tiende a: siguiente ventaja

a[X Imitar la asignación de bloques de a[ ] Es más barata

] tamaño fijo b[ Gana tiempo en el cambio de

b[ ] Disminuir la fragmentación interna X ] contexto

c[ ] Que la Razón de Acierto sea muy c[ ] Evita la sobre paginación

baja d[ ] Mejora el rendimiento del Quantum

d[ ] Tener más fallos de página e[ ] Genera poca Fragmentación

e[ ] Usar más el procesador

15. En el TLB se almacenan: 16. El mapeo de direcciones lógicas a físicas

a[ ] Registros realizado mediante la MMU:

b[ ] Páginas completas de los procesos a[ ] Aligera el cambio de contexto

c[ ] Información del contexto b[ ] Siempre más complicado

d[ c[ ] Disminuye los bloqueos

Direcciones de páginas

X] d[

Es más rápido que por software

e[ ] Variables muy usadas X]

recientemente e[ ] Es más barato que por software

17. Con el algoritmo de envejecimiento, si 18. El TLB se usa en una arquitectura para:

los bits de referencia de una página fueron a[ ] Disminuir la cantidad de páginas en

1,0,0,1,1,1 en los últimos 6 ciclos del reloj, memoria principal

el contador se verá así: b[ ] Facilitar el cambio de contexto

a[ ] 10000000, 01000000, 01100000, c[ ] Que no se produzcan fallos de

10011000, 11001100, 011001101 página

b[ 10000000, 01000000, 00100000, d[ Aligerar el tiempo de acceso a la

X] 10010000, 11001000, 11100100

X] memoria principal

c[ ] 00000000, 01000000, 00100000, e[ ] Aumentar la Razón de Acierto

10010000, 11001000, 01100100

d[ ] 10000000, 01000000, 00100000,

10011000, 11001000, 01100100

e[ ] 10000000, 01000000, 00100000,

00010000, 00001000, 00000100

19. Un proceso que requiere 577K de RAM 20. Con 16 GB en RAM divididos en

en un SO con páginas de 4K, se le asignan: páginas de 8K se tienen la siguiente

a[ ] 37 páginas y no tiene cantidad de páginas

fragmentación interna a[ ] 1,048,576

b[ ] 36 y no tiene fragmentación interna b[ ] 524,288

c[ ] 73 páginas y tiene 7K de c[ ] 262,144

fragmentación interna d[ ] 4,194,304

d[ 37 páginas y tiene 15 K de e[

X] fragmentación interna 2,097,152

X]

e[ ] 30.0625 y no tiene fragmentación

interna

21. La Fragmentación Interna se da 22. El problema de los filósofos cenando es

cuando: un problema clásico de:

a[ ] Las páginas son de tamaño variable a[ ] Inanición

b[ ] Las páginas son muy pequeñas b[ ] Acceso a la memoria compartida

c[ ] Quedan páginas sin asignar c[ ] Programación secuencial

d[ Queda memoria sin utilizar dentro d[ ] Programación con hilos

X] de una página

e[ ] Los procesos se quedan sin e[

Sincronización

memoria X]

23. El contenido del TLB cambia 24. Las direcciones de un proceso nunca

completamente cuando: varían durante el ciclo de vida cuando el

a[ ] El paginador regresa con las mapeo de direcciones lógicas a físicas se

páginas del disco duro hace:

b[ ] El proceso regresa a la cola de a[ ] En tiempo de ejecución

listos b[ ] En tiempo de carga

c[ ] Hay fallos de páginas c[

En tiempo de compilación

d[ X]

Se efectúa el cambio de contexto

X] d[ ] En tiempo de diseño

e[ ] El proceso está bloqueado e[ ] Depende del tamaño del TLB

25. La Memoria Virtual se implementa 26. Uno de los objetivos de las memorias

mediante: caché consiste en:

a[ ] Un TLB grande a[ ] Aumentar la cantidad de procesos

b[ ] Bloques de tamaño variable en la cola de listos

c[ ] Páginas pequeñas b[ ] Reducir el tiempo de ejecución del

Cambio de Contexto

d[

La paginación por demanda c[ ] Reducir el tiempo de CPU

X]

e[ ] Bloques de tamaño fijo d[ Reducir el tiempo de transferencia

X] entre dos componentes

e[ ] Mejorar el tiempo de acceso al TLB

27. Una desventaja de la asignación de 28. Un posible bloqueo mutuo se puede

memoria con bloques de tamaño variable: solucionar mediante:

a[ ] Es un proceso lento a[ ] El uso de varios hilos

b[ ] Los procesos grandes no se pueden b[ ] El uso de un vector de semáforos

ejecutar c[ ] La inanición

c[ ] Es muy dependiente del código d[ El uso de mutex en la sección

generado por el compilador X] crítica

d[ ] El sistema se degrada e[ ] La exclusión de recursos

e[ El SO debe reorganizar la memoria compartidos

X] cada cierto tiempo

29. El algoritmo para asignación de 30. Cuando dos o más procesos esperan la

bloques (de tamaño variable) que ocurrencia de un evento indefinidamente:

determina más rápido si un proceso no se a[

puede atender porque es demasiado grande X ] Hay un bloqueo

es: b[ ] Hay sobre paginación

a[ ] Primer ajuste c[ ] Hay un fallo de página

b[ ] Bloques de tamaño fijo d[ ] Ocurre un problema con un hilo

c[ ] Envejecimiento e[ ] Ocurre un error de sincronización

d[

Peor ajuste

X]

e[ ] Mejor ajuste

31. La Anomalía de Belady está 32. En el problema de los filósofos cenando:

relacionado con el siguiente algoritmo de a[ ] Con semáforos no se puede resolver

reemplazo: b[ ] Los hilos son la única solución

a[ ] Envejecimiento c[ ] La solución depende la cantidad de

b[ Primera en entrar, primera en salir filósofos

X] (FIFO) d[ Los tenedores son las variables

c[ ] No usada recientemente X] mutex

d[ ] Menos usada recientemente e[ ] La inanición no es posible

e[ ] Segunda oportunidad

33. Dada una cantidad variable de 34. Intel afirma que sus procesadores con un

procesos, utilizando paginación ¿Cuál SO TLB de 32 direcciones tiene una Razón de

genera más fragmentación interna?: Acierto de:

a[ ] Con páginas de 16K a[ ] 2%

b[ b[

Con páginas de 64K 98%

X] X]

c[ ] Con páginas de 8K c[ ] 100%

d[ ] Con páginas de 4K d[ ] 80%

e[ ] Con páginas de 32K e[ ] 95%

35. El tamaño de las páginas en la Memoria 36. Una desventaja de la espera activa es

Secundaria: que:

a[ Es igual que en la memoria a[ ] Produce fragmentación

X] principal b[ ] Afecta la sincronización

b[ ] Depende del tamaño de la memoria c[ ] Hay más bloqueos

c[ ] Es de 8 K d[ Hace un uso ineficiente del

d[ ] Es variable X] procesador

e[ ] Es de 4 GB e[ ] Aumentan los fallos de página

37. Una desventaja del Mejor Ajuste es: 38. Los SO usan páginas de tamaños

a[ ] Genera mucha Fragmentación pequeños para:

b[ ] Pierde mucho tiempo en los a[ ] Aumentar la localidad de referencia

cambios de contexto b[

Disminuir la fragmentación interna

c[ ] Los bloques no se agrupan X]

d[ ] Es difícil de implementar c[ ] Favorecer el cambio de contexto

e[ Es posible recorrer todos los d[ ] Disminuir la sobre paginación

X] bloques sin éxito e[ ] Disminuir los fallos de páginas

39. El TEA podría mejorar notablemente 40. El mapeo de direcciones de lógicas a

si: físicas en tiempo de ejecución se debe a que:

a[ ] Si los sectores en el disco fueran a[ ] El tamaño de las páginas es

más grandes pequeño

b[ ] Si el paginador siempre fuera b[ X ] Cambian de ubicación durante la

inteligente ejecución

c[ ] Si las páginas fueran más c[ ] El compilador genera un código

grandes optimizado

d[ ] El TLB se implementa en una d[ ] Se usa memoria con bloques de

memoria caché tamaño fijo

e[ X] Si el TLB pudiera guardar las e[ ] La memoria se fragmenta

páginas completas

41. El Tiempo para resolver un Fallo de 42. Los Algoritmos de Reemplazo deben ser

Página toma: eficientes para que:

a[ ] Depende del tiempo de acceso a[

Los fallos de página sean mínimos

del TLB X]

b[ ] Depende del tiempo asignado al b[ ] Mejore la localidad de referencia

Quantum c[ ] Mejore el tiempo de lectura

c[ ] 122 ns d[ ] Evitar la sobre paginación

d[ X] Varios milisegundos e[ ] La Razón de Acierto sea la misma

e[ ] 100 ns

43. Una ventaja de la paginación es: 44. Una desventaja de la administración de

a[ la memoria con paginación es:

No ocupa compactación

X] a[ ] No existe la fragmentación

b[ ] El acceso a la memoria es muy b[ ] El grado de multiprogramación es

rápido ilimitado

c[ ] Los procesos tienen todos sus c[ ] Los procesos se ejecutan con una

páginas en RAM parte del código

d[ ] No existe la fragmentación d[

Existen fallos de página

e[ ] Los tamaños pueden ser variables X]

e[ ] Favorece a los procesos que

demandan mucha CPU

45. Un buen algoritmo de reemplazo: 46. Una TLB con capacidad para 8 páginas

a[ X] Cambia las páginas menos numeradas de 0 a 7, con los bits en cero. Las

referenciadas páginas se referencian en el siguiente orden:

b[ ] Mejora el cambio de contexto C, A, E, B, D, A, C, A, E, B, G, C, D, H, F.

Ahora se referencia K, ¿cuál sale?:

c[ ] Produce menos fragmentación

a[ ] C

d[ ] Necesita un grupo de 8 bits

b[ X ] A

e[ ] Mejora la localidad de referencia

c[ ] G

d[ ] H

e[ ] D

47. Un paginador perezoso: 48. En un Sistema Operativo con páginas de

a[ ] Aumenta la razón de acierto 4K la fragmentación interna nunca será

b[ X] Incrementa la cantidad de fallos mayor que

de página a[

4K

c[ ] Aumenta el cambio de contexto X]

b[ ] 8K

d[ ] Favorece el tiempo de ejecución

de los procesos c[ ] 2K

e[ ] Disminuye el tiempo de lectura d[ ] 16K

en el disco e[ ] 0K

49. La administración de la memoria RAM 50. Una ventaja de la administración de la

con bloques de tamaño variable: memoria con paginación es que:

a[ ] Favorece a los procesos grandes a[ ] No hay fallos de página

b[ ] Tiene Fragmentación Externa en b[ ] No hay fragmentación interna

los bloques grandes c[ ] Los procesos se ejecutan siempre en

c[ RAM

No produce Fragmentación Interna

X] d[ Se disminuye considerablemente la

d[ ] Favorece a los procesos que X] fragmentación interna

demandan mucha CPU e[ ] Disminuyen los fallos de página

e[ ] Es el esquema más utilizado en los

SO actuales

Buena suerte :-)

También podría gustarte

- Linux en AzureDocumento487 páginasLinux en AzurePedro FuenzalidaAún no hay calificaciones

- Ejercicio Memoria ResueltosDocumento4 páginasEjercicio Memoria ResueltosmayyyAún no hay calificaciones

- 2020 Scrum Guide Spanish EuropeanDocumento17 páginas2020 Scrum Guide Spanish EuropeanjeaustinAún no hay calificaciones

- Soluciones Tema 2Documento3 páginasSoluciones Tema 2Sergio Muñoz100% (1)

- Ejercicios Realizados Sobre DockerDocumento38 páginasEjercicios Realizados Sobre Dockercarolina BonillaAún no hay calificaciones

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDe EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaAún no hay calificaciones

- Solución Tarea 9Documento2 páginasSolución Tarea 9jesusgomAún no hay calificaciones

- Ejercicios Resueltos Tema 5Documento16 páginasEjercicios Resueltos Tema 5Leandro López100% (1)

- Ejercicios Resueltos Tema 7Documento8 páginasEjercicios Resueltos Tema 7Jami MillerAún no hay calificaciones

- Examen Final SI643 - 2020-1Documento10 páginasExamen Final SI643 - 2020-1Dyland Steven Saldaña Del RosarioAún no hay calificaciones

- Guía Práctica de Informática para DocentesDocumento43 páginasGuía Práctica de Informática para DocentesEmpresarios por la Educación100% (8)

- Circuito Secuencial (LL) y Memoria SemiconductorDocumento6 páginasCircuito Secuencial (LL) y Memoria SemiconductorCHRISTOPHER ROBIN JOSE OBREGON PATIÑOAún no hay calificaciones

- TestDocumento27 páginasTestAngel Luis Tovar PazAún no hay calificaciones

- Examen Final-Febrero-2021-G2Documento4 páginasExamen Final-Febrero-2021-G2Brayan BarruetaAún no hay calificaciones

- Taller Sos 2.0Documento8 páginasTaller Sos 2.0Liana MarcelaAún no hay calificaciones

- Examen Final Si643 2020 2Documento6 páginasExamen Final Si643 2020 2Rosmel Gomez BenancioAún no hay calificaciones

- HCD EspolDocumento4 páginasHCD EspolAnonymous 7rbDr3bIAún no hay calificaciones

- EXAMEN Final SISTEMAS OPERATIVOSDocumento4 páginasEXAMEN Final SISTEMAS OPERATIVOSJuan Carlos MoraAún no hay calificaciones

- Resumen Del Material Proporcionado.Documento6 páginasResumen Del Material Proporcionado.GorbytAún no hay calificaciones

- Trabajo Practico de Test 4 Taller de HardwareDocumento2 páginasTrabajo Practico de Test 4 Taller de HardwareAlberto ArruaAún no hay calificaciones

- 1 11 EjerdelucamemoriaDocumento8 páginas1 11 EjerdelucamemoriaEveling CastroAún no hay calificaciones

- Examen 21-22Documento7 páginasExamen 21-22Sergio Trillo RodríguezAún no hay calificaciones

- Temaa IV - Parte 4Documento20 páginasTemaa IV - Parte 4Daniel MartinezAún no hay calificaciones

- Trabajo Del Capitulo 7 SISTEMAS OPERATIVOSDocumento10 páginasTrabajo Del Capitulo 7 SISTEMAS OPERATIVOSBrayan Murphy Crespo EspinozaAún no hay calificaciones

- Examen 18-19Documento7 páginasExamen 18-19EDUARDO GONZÁLEZ GUTIÉRREZAún no hay calificaciones

- Clase 11 - MultiprogramaciónDocumento62 páginasClase 11 - MultiprogramaciónVALENTINA SALAZARAún no hay calificaciones

- Practica Nro 1Documento8 páginasPractica Nro 1Sergio LeandroAún no hay calificaciones

- Test Bloque II Tema 1, 2 y 3Documento18 páginasTest Bloque II Tema 1, 2 y 3tueresAún no hay calificaciones

- Control 3 (2020)Documento4 páginasControl 3 (2020)Jhon TiznadoAún no hay calificaciones

- Examen ArqDocumento6 páginasExamen ArqDavid CedilloAún no hay calificaciones

- Test AlumnoDocumento3 páginasTest AlumnoFranciscoJoséLedesmaMolinaAún no hay calificaciones

- Computer Science Paper 1 HL SpanishDocumento9 páginasComputer Science Paper 1 HL Spanishdonn dadaAún no hay calificaciones

- Ejercicios Tema 5-12-13Documento5 páginasEjercicios Tema 5-12-13Zarate BismkAún no hay calificaciones

- Cuestionarios Sor 01Documento4 páginasCuestionarios Sor 01JCDIAún no hay calificaciones

- 1-4 Cuestionario Tipos de Sistemas OperativosDocumento2 páginas1-4 Cuestionario Tipos de Sistemas OperativosGuido Roberto GutiérrezAún no hay calificaciones

- Presentacion Rendimiento OpenEdge RDBMS PDF PDFDocumento26 páginasPresentacion Rendimiento OpenEdge RDBMS PDF PDFLucho Montero100% (1)

- 2do Parcial PDFDocumento36 páginas2do Parcial PDFlolaAún no hay calificaciones

- SistOper zOSDocumento76 páginasSistOper zOSMichael Arroyo HerediaAún no hay calificaciones

- Test AlumnoDocumento3 páginasTest AlumnoFranciscoJoséLedesmaMolinaAún no hay calificaciones

- Ejercicios Tema6Documento4 páginasEjercicios Tema6Xavier DaviasAún no hay calificaciones

- Ejercicios Pro Tema MEMORIA NO RESUELTOSDocumento3 páginasEjercicios Pro Tema MEMORIA NO RESUELTOSErickAún no hay calificaciones

- ASD - Arquitectura de Sistemas Distribuidos PDFDocumento322 páginasASD - Arquitectura de Sistemas Distribuidos PDFpaquito923Aún no hay calificaciones

- Practica Nro 1Documento7 páginasPractica Nro 1Richar Calizaya Carvajal100% (1)

- 2do PracticoDocumento3 páginas2do Practicocarlos huaytaAún no hay calificaciones

- Preguntas de ComputaciónDocumento15 páginasPreguntas de ComputaciónLuis GmmAún no hay calificaciones

- TP 6-2020Documento5 páginasTP 6-2020juan godoyAún no hay calificaciones

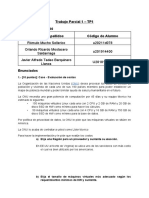

- Trabajo Parcial 1 - TP1 Número de Grupo: 10 Nombres y Apellidos Código de AlumnoDocumento13 páginasTrabajo Parcial 1 - TP1 Número de Grupo: 10 Nombres y Apellidos Código de AlumnoRicardo MostaceroAún no hay calificaciones

- Formacion Bim An NologoDocumento137 páginasFormacion Bim An NologoCarlos BenavidesAún no hay calificaciones

- Auxiliar Adm Canarias Sept2006 Libre-Bl2Documento2 páginasAuxiliar Adm Canarias Sept2006 Libre-Bl2Paula RamosAún no hay calificaciones

- Tarea Gestión de Los Recursos PDFDocumento4 páginasTarea Gestión de Los Recursos PDFEdgar UlloaAún no hay calificaciones

- Parcial de Operativos USBDocumento5 páginasParcial de Operativos USBJuan Carlos ViñaAún no hay calificaciones

- Preguntas Gestion de MemoriaDocumento4 páginasPreguntas Gestion de MemoriaSandro Javier Garavito GuerraAún no hay calificaciones

- Preguntas Cliente ServidorDocumento24 páginasPreguntas Cliente ServidorRaul Villafuerte Mejia100% (1)

- Memoria CachéDocumento30 páginasMemoria CachéLuis Eduardo MoralesAún no hay calificaciones

- Trabajo de Redes de Computadoras TanenbaumDocumento4 páginasTrabajo de Redes de Computadoras Tanenbaumsoyhernan1986Aún no hay calificaciones

- Practica 1Documento7 páginasPractica 1Brayan TerrazasAún no hay calificaciones

- TP1 - Sistemas de Numeración y Unidades de Información 2017Documento6 páginasTP1 - Sistemas de Numeración y Unidades de Información 2017jornada660Aún no hay calificaciones

- Ejercicios Tema 5 MVDocumento3 páginasEjercicios Tema 5 MVSebastian BasantesAún no hay calificaciones

- Examen 19-20 Turno TardeDocumento5 páginasExamen 19-20 Turno TardeEDUARDO GONZÁLEZ GUTIÉRREZAún no hay calificaciones

- Trabajo Del Capitulo 7Documento13 páginasTrabajo Del Capitulo 7John CRAún no hay calificaciones

- Practico 4 2021Documento8 páginasPractico 4 2021Matias BeneitezAún no hay calificaciones

- FSO 20190520 Ordinaria p2 Test SolucionesDocumento4 páginasFSO 20190520 Ordinaria p2 Test SolucionesHector BazarteAún no hay calificaciones

- Generación de malla: Avances y aplicaciones en la generación de mallas de visión por computadoraDe EverandGeneración de malla: Avances y aplicaciones en la generación de mallas de visión por computadoraAún no hay calificaciones

- Carta Redes 6 3 2022 SentDocumento9 páginasCarta Redes 6 3 2022 SentjeaustinAún no hay calificaciones

- 02 P3 Tema02Documento50 páginas02 P3 Tema02jeaustinAún no hay calificaciones

- Proyecto 2 EIF209 2022-1Documento3 páginasProyecto 2 EIF209 2022-1jeaustinAún no hay calificaciones

- Progra-1 Proyec-No1 - IIC - 2022Documento4 páginasProgra-1 Proyec-No1 - IIC - 2022jeaustinAún no hay calificaciones

- EIF-207 Estructuras de Datos 2022-02Documento10 páginasEIF-207 Estructuras de Datos 2022-02jeaustinAún no hay calificaciones

- Noche en VelaDocumento10 páginasNoche en VelajeaustinAún no hay calificaciones

- Manual Control WinDocumento47 páginasManual Control WinElioSolarAún no hay calificaciones

- Practica de Carrera 2Documento20 páginasPractica de Carrera 2Rosa Isabel Sanchez CastilloAún no hay calificaciones

- 445 - Acta de Entrega Recepción Da-025!26!8455-Gadmur-2014Documento8 páginas445 - Acta de Entrega Recepción Da-025!26!8455-Gadmur-2014Carlos GimenezAún no hay calificaciones

- 033 - Instalación JUPITER + Capacidad de ImpresiónDocumento12 páginas033 - Instalación JUPITER + Capacidad de Impresiónmlrivero671239Aún no hay calificaciones

- Acceso RemotoDocumento4 páginasAcceso RemotoDanielaVelascoAún no hay calificaciones

- Manual WinsammDocumento0 páginasManual WinsammEduardo RockoAún no hay calificaciones

- Instalación Accys Time en SQL ClienteDocumento9 páginasInstalación Accys Time en SQL ClienteTecate VeinticuatroAún no hay calificaciones

- 6.1.4.7 Packet Tracer - Configure Firewall SettingsDocumento3 páginas6.1.4.7 Packet Tracer - Configure Firewall SettingsCuervo CuervoAún no hay calificaciones

- Encriptacion Del GrubDocumento6 páginasEncriptacion Del GrubAngel OrtAún no hay calificaciones

- Act Individual Paso4 CristhianFdoGutierrezAcostaDocumento8 páginasAct Individual Paso4 CristhianFdoGutierrezAcostaCristhianGutierrezAún no hay calificaciones

- Configurar El Servidor Radius en Windows Server para Autenticar Usuarios de VPN Cisco - The SolvingDocumento21 páginasConfigurar El Servidor Radius en Windows Server para Autenticar Usuarios de VPN Cisco - The SolvingEdwin MarquezAún no hay calificaciones

- Instalación Windows Server 2008, Servidor DHCP y WINSDocumento16 páginasInstalación Windows Server 2008, Servidor DHCP y WINSXema LopezAún no hay calificaciones

- AFT-Manual PATRONEO KEY 2013 PDFDocumento230 páginasAFT-Manual PATRONEO KEY 2013 PDFhaleboop elpiAún no hay calificaciones

- Qué Es El Sistema de ArchivosDocumento22 páginasQué Es El Sistema de ArchivosAlfredoAlonsoAlcocerBalamAún no hay calificaciones

- Wifiway 2Documento4 páginasWifiway 2Patricio_Mansi_1721Aún no hay calificaciones

- Actividad 2 Unidad 2: Máximo Martínez Pérez 1ºdam A 1Documento7 páginasActividad 2 Unidad 2: Máximo Martínez Pérez 1ºdam A 1Maximo MartinezAún no hay calificaciones

- Plan de Clases de Windows 2006Documento28 páginasPlan de Clases de Windows 2006Genry Sánchez DucongerAún no hay calificaciones

- Actividad No. 4: Introducción A Kali LinuxDocumento7 páginasActividad No. 4: Introducción A Kali LinuxSebastian ReyesAún no hay calificaciones

- Sistemas Operativos - Taller 2-2Documento9 páginasSistemas Operativos - Taller 2-2Catalina TellezAún no hay calificaciones

- Configuracion Basica GNS3Documento9 páginasConfiguracion Basica GNS3acidburdAún no hay calificaciones

- Casos de Uso (Casos)Documento30 páginasCasos de Uso (Casos)joeshegoAún no hay calificaciones

- Instalacion Del FTDIDocumento16 páginasInstalacion Del FTDIElisa VegaAún no hay calificaciones

- Practica de Windows 2 PDFDocumento9 páginasPractica de Windows 2 PDFgisellaAún no hay calificaciones

- Temas #02 - Material de Computacion IDocumento31 páginasTemas #02 - Material de Computacion ILisvia InchausteguiAún no hay calificaciones

- Instalación y Configuración Servidor ProFTPdDocumento3 páginasInstalación y Configuración Servidor ProFTPdCuenta FalsaAún no hay calificaciones

- Tema Muestra OkDocumento12 páginasTema Muestra OkCurso Web HemeroscopeaAún no hay calificaciones