Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Practica 1 - Decodificador BCD A 7 Segmentos PDF

Practica 1 - Decodificador BCD A 7 Segmentos PDF

Cargado por

Reene CondoriTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Practica 1 - Decodificador BCD A 7 Segmentos PDF

Practica 1 - Decodificador BCD A 7 Segmentos PDF

Cargado por

Reene CondoriCopyright:

Formatos disponibles

UNIPAZ Fecha:

INSTITUTO UNIVERSITARIO DE LA PAZ (Decreto Ordenanzal 0331 ……………….

de 1987)

ESCUELA DE INGENIERIA DE PRODUCCIÓN PROGRAMA TECNOLOGÍA Versión 1

ELECTROMECÁNICA PROGRAMA CURRICULAR CIRCUITOS ELECTRICOS Pág. 1 de 4

SEMESTRE I AÑO 2015

PRÁCTICA #1.

DECODIFICADOR BCD A 7 SEGMENTOS

OBJETIVOS

1. Evaluar e interpretar características fundamentales del decodificador.

2. Analizar el display de siete segmentos, respecto de la medición de sus

terminales.

3. Verificar en la mediciòn los dos tipos de display de siete segmentos anodo-

comùn y catodo-comùn.

PROCEDIMIENTO

La función básica de un decodificador es detectar la presencia de una determinada

combinación de bits (código) en sus entradas y señalar la presencia de este código

mediante un cierto nivel de salida.

Un ejemplo de aplicación es el decodificador BCD a 7 segmentos. Este tipo de

decodificador acepta código BCD en sus entradas y proporciona salidas capaces de

excitar un display de 7 segmentos para indicar un dígito decimal.

En la figura se muestra un display común formado por siete elementos o segmentos.

Excitando determinadas combinaciones de estos segmentos se pueden obtener cada uno

de los diez dígitos decimales.

Para generar un 1 se excitan los segmentos b y c como se muestra en la figura.

UNIPAZ Fecha:

INSTITUTO UNIVERSITARIO DE LA PAZ (Decreto Ordenanzal 0331 ……………….

de 1987)

ESCUELA DE INGENIERIA DE PRODUCCIÓN PROGRAMA TECNOLOGÍA Versión 1

ELECTROMECÁNICA PROGRAMA CURRICULAR CIRCUITOS ELECTRICOS Pág. 2 de 4

SEMESTRE I AÑO 2015

Cada segmento se utiliza para varios dígitos decimales, pero ninguno de ellos se emplea

para representar los diez dígitos, por lo tanto cada segmento tiene que activarse mediante

su propio circuito de decodificación, que detecta la aparición de cualquier número en el

que haya que usar ese segmento.

Los segmentos que se deben activar para cada uno de los dígitos se muestran en la tabla.

Dígito Segmentos activados

0 a, b, c, d, e, f

1 b, c

2 a, b, d, e, g

3 a, b, c, d, g

4 b, c, f, g

5 a, c, d, f, g

6 a, c, d, e, f, g

7 a, b, c

8 a, b, c, d, e, f, g

9 a, b, c, d, f, g

La lógica de decodificación de segmentos requiere cuatro entradas en código decimal

binario (BCD) y siete salidas, una para cada segmento del display, como se indica en el

diagrama de bloques de la figura.

UNIPAZ Fecha:

INSTITUTO UNIVERSITARIO DE LA PAZ (Decreto Ordenanzal 0331 ……………….

de 1987)

ESCUELA DE INGENIERIA DE PRODUCCIÓN PROGRAMA TECNOLOGÍA Versión 1

ELECTROMECÁNICA PROGRAMA CURRICULAR CIRCUITOS ELECTRICOS Pág. 3 de 4

SEMESTRE I AÑO 2015

La tabla de verdad de salida múltiple es:

Dígito Entradas Salidas de segmentos

Decimal D C B A a b c d e f g

0 0 0 0 0 1 1 1 1 1 1 0

1 0 0 0 1 0 1 1 0 0 0 0

2 0 0 1 0 1 1 0 1 1 0 1

3 0 0 1 1 1 1 1 1 0 0 1

4 0 1 0 0 0 1 1 0 0 1 1

5 0 1 0 1 1 0 1 1 0 1 1

6 0 1 1 0 1 0 1 1 1 1 1

7 0 1 1 1 1 1 1 0 0 0 0

8 1 0 0 0 1 1 1 1 1 1 1

9 1 0 0 1 1 1 1 1 0 1 1

10 1 0 1 0 X X X X X X X

11 1 0 1 1 X X X X X X X

12 1 1 0 0 X X X X X X X

13 1 1 0 1 X X X X X X X

14 1 1 1 0 X X X X X X X

15 1 1 1 1 X X X X X X X

Como el código BCD no incluye los valores binarios 1010, 1011, 1100, 1101, 1110 y 1111,

estas combinaciones no van nunca a aparecer en las entradas y pueden, por lo tanto,

tratarse como condiciones indiferentes (X), como se indica en la tabla de verdad.

A partir de la tabla de verdad se puede escribir para cada segmento una expresión suma

de productos. Por ejemplo la suma de productos estándar para el segmento a es:

a DC B A DC B A DC BA DC B A DCB A DCBA DC B A DC B A

La implementación de la suma de productos estándar de la lógica del segmento a

requiere un circuito AND-OR formado por 8 compuertas AND de 4 entradas y 1 compuerta

OR de 8 entradas. Puede obtenerse mediante el diagrama de Karnaugh una expresión

suma de productos mínima para el segmento a.

Los pasos a seguir son:

1) Los 1s de la tabla se pasan directamente al mapa de Karnaugh.

2) Se introducen en el mapa todas las condiciones indiferentes (X).

3) Se agrupan los 1s y las condiciones indiferentes para conseguir los grupos más

grandes posibles.

UNIPAZ Fecha:

INSTITUTO UNIVERSITARIO DE LA PAZ (Decreto Ordenanzal 0331 ……………….

de 1987)

ESCUELA DE INGENIERIA DE PRODUCCIÓN PROGRAMA TECNOLOGÍA Versión 1

ELECTROMECÁNICA PROGRAMA CURRICULAR CIRCUITOS ELECTRICOS Pág. 4 de 4

SEMESTRE I AÑO 2015

El diagrama de Karnaugh para el segmento a es:

La expresión mínima a partir del diagrama de Karnaugh para la lógica del segmento a es:

a1 D B CA C A

ENTREGABLES

a) Determinar la lógica mínima para los segmentos b, c, d, e, f y g. (HOJA DE EXAMEN).

b) Dibujar Y Simular en proteus el diagrama lógico para el decodificador de 7

segmentos, combinando todos los circuitos lógicos de los segmentos individuales y

eliminando las puertas y los inversores duplicados.

c) Implementar el montaje usando compuertas lógicas.

También podría gustarte

- UNI2Documento35 páginasUNI2BL LauraAún no hay calificaciones

- Enunciados de Los Problemas (Impresion)Documento27 páginasEnunciados de Los Problemas (Impresion)marcosAún no hay calificaciones

- La SanturronaDocumento3 páginasLa SanturronamarcosAún no hay calificaciones

- La SanturronaDocumento3 páginasLa SanturronamarcosAún no hay calificaciones

- Introductorio 17Documento62 páginasIntroductorio 17marcosAún no hay calificaciones

- Biologia 1Documento264 páginasBiologia 1marcosAún no hay calificaciones

- Ficha Técnica Zebra Zt230Documento3 páginasFicha Técnica Zebra Zt230Chumy BlancoAún no hay calificaciones

- LAB9 ENSAMBLAJE v2Documento8 páginasLAB9 ENSAMBLAJE v2Alex VilcapomaAún no hay calificaciones

- Desarrollo Virtual Controles ActivexDocumento281 páginasDesarrollo Virtual Controles ActivexraculmanAún no hay calificaciones

- Documentación de Microsoft Defender para Punto de ConexiónDocumento3694 páginasDocumentación de Microsoft Defender para Punto de ConexiónOsekdj SlpAún no hay calificaciones

- Informe Tecnico de Taller Computadoras ColegioDocumento5 páginasInforme Tecnico de Taller Computadoras ColegioTimoteo Machaca CalcinaAún no hay calificaciones

- Laboratorio 6-Joel FuertesDocumento4 páginasLaboratorio 6-Joel FuertesJoel Edgar Fuertes MelendezAún no hay calificaciones

- Control de Los PuertosDocumento4 páginasControl de Los PuertosDaniel Reyes CastañedaAún no hay calificaciones

- Trabajo Práctico N°16 - Técnicas DigitalesDocumento16 páginasTrabajo Práctico N°16 - Técnicas DigitalesValentin GaleoteAún no hay calificaciones

- Capa de AplicacionDocumento27 páginasCapa de AplicacionGatito MonsterAún no hay calificaciones

- Qué Es SAPDocumento1 páginaQué Es SAPfrobledogAún no hay calificaciones

- Uf1868 - Operación y Supervisión de Los Equipos y ServiciosDocumento31 páginasUf1868 - Operación y Supervisión de Los Equipos y ServiciosAriadna SantanaAún no hay calificaciones

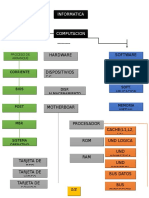

- Esquema ComputacionalDocumento2 páginasEsquema ComputacionalAlexis Ferrera FelizAún no hay calificaciones

- Grafcet Como Método Gráfico para La Resolución de Procesos SecuencialesDocumento5 páginasGrafcet Como Método Gráfico para La Resolución de Procesos Secuencialesalvaroazael.lealAún no hay calificaciones

- ProfibusDocumento9 páginasProfibusfanny regulesAún no hay calificaciones

- CZ-V21A DatasheetDocumento3 páginasCZ-V21A DatasheetJuan Carlos TierrablancaAún no hay calificaciones

- Resumen de Las Familias LogicasDocumento18 páginasResumen de Las Familias LogicasjoelAún no hay calificaciones

- Linux Essentials - Capítulo 3Documento7 páginasLinux Essentials - Capítulo 3Nicole Alejandra Pérez Tapia100% (1)

- Autoevaluacion de InformaticaDocumento2 páginasAutoevaluacion de InformaticaCarlos EscobarAún no hay calificaciones

- Electroneumática-1Documento60 páginasElectroneumática-1germanAún no hay calificaciones

- Informe 05 Configuración de SwitchDocumento11 páginasInforme 05 Configuración de SwitchAlex ZuritaAún no hay calificaciones

- Tarea Tipos de PeriféricosDocumento14 páginasTarea Tipos de PeriféricosSilviaGEBAún no hay calificaciones

- Capítulo 5 - Mantenimiento Del Redo LogDocumento38 páginasCapítulo 5 - Mantenimiento Del Redo LogFrancisco GuiñazúAún no hay calificaciones

- Vectores y MatricesDocumento35 páginasVectores y MatriceshdhdjdAún no hay calificaciones

- Instalacion Scada Wincc w10 - Rev1Documento4 páginasInstalacion Scada Wincc w10 - Rev1Denny JimenezAún no hay calificaciones

- Introduccion A Los Permisos de Archivos y Tipos de ArchivosDocumento39 páginasIntroduccion A Los Permisos de Archivos y Tipos de ArchivosKariina RománAún no hay calificaciones

- 26.1.7 Lab - Snort and Firewall RulesDocumento9 páginas26.1.7 Lab - Snort and Firewall RulesjuanAún no hay calificaciones

- Ficha y Cables USB Por DentroDocumento3 páginasFicha y Cables USB Por DentroEdgar PimentelAún no hay calificaciones

- TRabajo TIA2 TemporizadoresDocumento10 páginasTRabajo TIA2 Temporizadoresdavid munozAún no hay calificaciones