Documentos de Académico

Documentos de Profesional

Documentos de Cultura

G6 L2 2019 03

G6 L2 2019 03

Cargado por

david alejandro muñoz0 calificaciones0% encontró este documento útil (0 votos)

8 vistas2 páginasIMPLEMENTACION DE UNA ALU

Título original

G6-L2-2019-03

Derechos de autor

© © All Rights Reserved

Formatos disponibles

DOC, PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoIMPLEMENTACION DE UNA ALU

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

8 vistas2 páginasG6 L2 2019 03

G6 L2 2019 03

Cargado por

david alejandro muñozIMPLEMENTACION DE UNA ALU

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como DOC, PDF, TXT o lea en línea desde Scribd

Está en la página 1de 2

1

David Alejandro Muñoz, Harold Murillo Pérez, Ever Harold López, Nicolas García

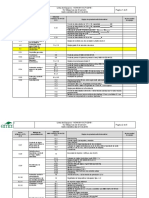

Laboratorio 2: Implementación De Unidad

Lógica Aritmética

Mostrar resultado hexadecimal

Resumen—En este proyecto lo que se trata es de hacer una

unidad aritmeticológica de 8 bits, es decir lo que solemos conocer

con el nombre de `ALU', y la implementaremos a partir del I. DISEÑO

lenguaje VHDL, es decir diseñaremos un algoritmo que

implemente una ALU. En el algoritmo se ha hecho de forma que

Lo que se va a realizar a continuación es la descripción

todo se tiene que hacer a través de compuertas lógicas es decir un

lenguaje puramente sintetizable ya que sólo utilizaremos comportamental algorítmica del circuito de la figura anterior,

compuertas. después se realizará la transferencia entre registros, que sigue

siendo comportamental, y por último se verá la descripción

Abstract-- In this project, what is about is to make an 8-bit estructural mostrando así las diferencia. La sintaxis del VHDL

arithmetic unit, that is, what we usually know with the name of no es sensible a mayúsculas o minúsculas, por lo que se puede

`ALU ', and we will implement it from the VHDL language, that escribir como se prefiera. A lo largo de las explicaciones se

is, we will design an algorithm that implements an ALU. In the pondrán siempre las palabras clave del lenguaje en

algorithm it has been done in a way that everything must be done mayúsculas para distinguirlas de las variables y otros

through logic gates, that is, a purely synthesizable language since elementos. Esto no significa que durante la descripción de

we will only use gates. diseños se tenga que hacer así.

Introduction

E El significado de las siglas VHDL es VHSIC(Very High

Speed Integrated Circuit) Hardware Description

Language, es decir, lenguaje de descripción hardware de

circuitos integrados de muy alta velocidad. VHDL es un

lenguaje de descripción y modelado diseñado para describir,

en una forma en que los humanos y las máquinas puedan leer

y entender la funcionalidad y la organización de sistemas

hardware digitales, placas de circuitos y componentes.

El VHDL va a ser interesante puesto que va a permitir los dos

tipos de descripciones:

Estructura: VHDL puede ser usado como un lenguaje de Fig. 1. sumador restador.

Netlist normal y corriente donde se especifican por un lado los

componentes del sistema y por otro sus interconexiones.

Comportamiento: VHDL también se puede utilizar para la

descripción comportamental o funcional de un circuito. Esto

es lo que lo distingue de un lenguaje de Netlist. Sin necesidad

de conocer la estructura interna de un circuito es posible

describirlo explicando su funcionalidad. Esto es especialmente

útil en simulación, ya que permite simular un sistema sin

conocer su estructura interna. Así, este tipo de descripción se

está volviendo cada día más importante porque las actuales

herramientas de síntesis permiten la creación automática de

circuitos a partir de una descripción de su funcionamiento.

El propósito de este proyecto era diseñar e implementar una

ALU, o unidad de lógica aritmética, utilizando el lenguaje de Fig. 2. Compuerta AND/OR.

descripción de hardware Verilog y la placa Terasic DE10 Lite.

Esta ALU tiene que hacer las siguientes operaciones o

funciones:

Inversión

Suma

Resta

Compuerta AND y OR

2

Fig. 3. Multiplexor.

Al unir todos estos bloques de diseño se podrá crear una

ALU tal y como se verá a continuación:

Diagrama de bloques

Fig. 4. ALU.

REFERENCIAS

Diagrama de flujo [1] http://deeea.urv.cat/public/PROPOSTES/pub/pdf/170pub.pdf

[2] Lenguaje para la síntesis y modelado de circuitos VHDL. Autores:

Fernando Pardo y José A. Boluda. Editorial RA-MA.

También podría gustarte

- Informe Corto Vacio CargaDocumento6 páginasInforme Corto Vacio Cargadavid alejandro muñozAún no hay calificaciones

- Laboratorio 2: Implementación de Unidad Lógica AritméticaDocumento2 páginasLaboratorio 2: Implementación de Unidad Lógica Aritméticadavid alejandro muñozAún no hay calificaciones

- Modulos Secuenciales, Cronometro AutomaticoDocumento2 páginasModulos Secuenciales, Cronometro Automaticodavid alejandro muñozAún no hay calificaciones

- Informe Corto-Vacio-CargaDocumento6 páginasInforme Corto-Vacio-Cargadavid alejandro muñozAún no hay calificaciones

- SuperconductoresDocumento14 páginasSuperconductoresdavid alejandro muñozAún no hay calificaciones

- Linx 8920Documento2 páginasLinx 8920Luis Angel RomeroAún no hay calificaciones

- FGPR - 520 - 06 - Reporte de Performance Del Proyecto - SimplificadoDocumento2 páginasFGPR - 520 - 06 - Reporte de Performance Del Proyecto - SimplificadoMARCO ANTONIO PEÑA PLATAAún no hay calificaciones

- I Could Never - Penelope WardDocumento203 páginasI Could Never - Penelope Wardjulie amblaAún no hay calificaciones

- Ejercicios BalanceDocumento12 páginasEjercicios BalanceAle FigAún no hay calificaciones

- 2.9.1 Packet Tracer - Basic Switch and End Device ConfigurationDocumento6 páginas2.9.1 Packet Tracer - Basic Switch and End Device ConfigurationGersonBravoAún no hay calificaciones

- Procedimiento CremallerasDocumento5 páginasProcedimiento CremallerasSeguridad y Salud en el trabajoAún no hay calificaciones

- Guia de Resolucion de Problemas Sobre BujiasDocumento1 páginaGuia de Resolucion de Problemas Sobre BujiasjorhaiisAún no hay calificaciones

- Marketing OnlineDocumento14 páginasMarketing OnlineAlejandra VcAún no hay calificaciones

- Asignacion de Ejer. Mec. de Fluidos.. Leuris Diaz 2017-2600 PDFDocumento29 páginasAsignacion de Ejer. Mec. de Fluidos.. Leuris Diaz 2017-2600 PDFleuris diaz100% (1)

- Manual Instalación Centos 7 Con ParticionesDocumento38 páginasManual Instalación Centos 7 Con Particionesponce777Aún no hay calificaciones

- Actividad Online de Clasificación de TriángulosDocumento6 páginasActividad Online de Clasificación de TriángulosNancy EmtAún no hay calificaciones

- TRANSPORTEDocumento3 páginasTRANSPORTEEsc SamAún no hay calificaciones

- MICROCONTROLADORESDocumento5 páginasMICROCONTROLADORESCristhian LucasAún no hay calificaciones

- SENSORESDocumento6 páginasSENSORESEalrAún no hay calificaciones

- Manual de Uso Portal Del Empleado SoftlandDocumento23 páginasManual de Uso Portal Del Empleado SoftlandCarolina ParedesAún no hay calificaciones

- NOM-001-SCFI Seccion 5.2 Maq DiversionDocumento4 páginasNOM-001-SCFI Seccion 5.2 Maq DiversionAriel Amaro BeatrizAún no hay calificaciones

- Serv Veri Desc Sol ExitDocumento11 páginasServ Veri Desc Sol ExitbernhartAún no hay calificaciones

- Ingeteam Fusion EsDocumento2 páginasIngeteam Fusion EsSophia M.Aún no hay calificaciones

- Mis Amigas Las VocalesDocumento9 páginasMis Amigas Las VocalesCesar SamillanAún no hay calificaciones

- Trabajo Colaborativo Probabilidad Entrega FinalDocumento6 páginasTrabajo Colaborativo Probabilidad Entrega FinalZul M LiAún no hay calificaciones

- Lista de Chequeo de Manejo Y Almacenamiento de Materiales ChecklistDocumento5 páginasLista de Chequeo de Manejo Y Almacenamiento de Materiales ChecklistAlfredo Valdelamar ReynaAún no hay calificaciones

- Di Piero, E. y Miño Chiappino, J. - 2020 - REVISTA-54-dossier-Piero - Pp.42a58Documento17 páginasDi Piero, E. y Miño Chiappino, J. - 2020 - REVISTA-54-dossier-Piero - Pp.42a58Manuel DupuyAún no hay calificaciones

- Evaluación Modulo I Organización Del SG-SST - Revisión Del Intento 1Documento12 páginasEvaluación Modulo I Organización Del SG-SST - Revisión Del Intento 1Daniel GarcíaAún no hay calificaciones

- ILUMINACIÓNDocumento2 páginasILUMINACIÓNMANTENIMIENTO CAFEZAM SASAún no hay calificaciones

- Flete CampanillaDocumento3 páginasFlete CampanillaLEYDY ISABEL MEZA AMBICHOAún no hay calificaciones

- E-Book E-Commerce 4.0 - Snappy CommerceDocumento34 páginasE-Book E-Commerce 4.0 - Snappy Commercemarceloperera84Aún no hay calificaciones

- Tubo Sap PVCDocumento1 páginaTubo Sap PVCJOSE LUIS HUALLPATINCOAún no hay calificaciones

- PETS-ANT-MI-10 Conexión de LaboresDocumento2 páginasPETS-ANT-MI-10 Conexión de LaboresJersonAún no hay calificaciones

- Codigo p2020 Hyundai Acennt 2001Documento2 páginasCodigo p2020 Hyundai Acennt 2001Jorge Bacuilima MoraAún no hay calificaciones

- Foro 1Documento7 páginasForo 1Priscilla Ríos NovoaAún no hay calificaciones