Documentos de Académico

Documentos de Profesional

Documentos de Cultura

UNIVALLE

Cargado por

JESSICA ESCOBAR ORTIZ0 calificaciones0% encontró este documento útil (0 votos)

35 vistas1 páginaEste documento presenta un taller de Arquitectura de Computadores II que consiste en 12 puntos prácticos para ser resueltos en grupo utilizando comandos de depuración. Los puntos incluyen usar comandos como REGISTER, R, DUMP y SEARCH para visualizar y modificar registros, segmentos de memoria, la pila y buscar valores en memoria. El objetivo es familiarizarse con las herramientas de depuración y la arquitectura interna de la CPU.

Descripción original:

TALLER

Derechos de autor

© © All Rights Reserved

Formatos disponibles

PDF, TXT o lea en línea desde Scribd

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoEste documento presenta un taller de Arquitectura de Computadores II que consiste en 12 puntos prácticos para ser resueltos en grupo utilizando comandos de depuración. Los puntos incluyen usar comandos como REGISTER, R, DUMP y SEARCH para visualizar y modificar registros, segmentos de memoria, la pila y buscar valores en memoria. El objetivo es familiarizarse con las herramientas de depuración y la arquitectura interna de la CPU.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

0 calificaciones0% encontró este documento útil (0 votos)

35 vistas1 páginaUNIVALLE

Cargado por

JESSICA ESCOBAR ORTIZEste documento presenta un taller de Arquitectura de Computadores II que consiste en 12 puntos prácticos para ser resueltos en grupo utilizando comandos de depuración. Los puntos incluyen usar comandos como REGISTER, R, DUMP y SEARCH para visualizar y modificar registros, segmentos de memoria, la pila y buscar valores en memoria. El objetivo es familiarizarse con las herramientas de depuración y la arquitectura interna de la CPU.

Copyright:

© All Rights Reserved

Formatos disponibles

Descargue como PDF, TXT o lea en línea desde Scribd

Está en la página 1de 1

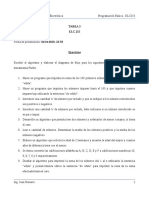

FACULTAD DE INGENIERÍAS

ESCUELA DE INGENIERÍA ELÉCTRICA Y ELECTRÓNICA

PROGRAMA ACADÉMICO DE TECNOLOGÍA EN SISTEMAS

ARQUITECTURA DE COMPUTADORES II

(Prof. Julián A. Giraldo)

TALLER #1

El taller debe ser resuelto en grupos de máximo tres (3) personas. Desarrolle cada

punto en el DEBUG e imprima los resultados obtenidos en el informe.

1. Use el comando REGISTER para desplegar los contenidos actuales de los

registros internos del CPU. Liste los valores CS, DS, SS y ES. ¿Qué significado

tienen estos valores iniciales?

2. Revise el estado del par de registros CS:IP y calcule la dirección física de la

siguiente instrucción a ser ejecutada

3. Use el comando R para primero desplegar el contenido de CX y después

cambie su valor a 1010H

4. Despliegue el contenido actual del registro de banderas y después cambie el

estado de la bandera de paridad para representar paridad PAR.

5. Despliegue el contenido de los registros internos y compárelos con los

contenidos que se obtuvieron inicialmente en el punto 1

6. Use el comando DUMP para desplegar los primeros 256 bytes del segmento

de datos en curso

7. Despliegue los siguientes 128 bytes del segmento de código

8. Use el comando DUMP para mostrar la 6 últimas palabras cargadas en la pila

9. Edite los primeros 16 bytes del segmento de datos en curso con el valor FFH.

Verifique que los contenidos hayan cambiado

10. -Use el comando FILL para cargar las 32 localidades de memoria a partir

de DS:10 con el valor 55H y las 32 localidades a partir de DS:40H con 00H.

11. Con el comando MOVE, copie el contenido de las 16 localidades a partir de

DS:00 a las 16 localidades a partir de DS:20H

12. Ejecute el comando SEARCH para determinar que localidades entre DS:00

y DS:FFH contienen el valor FFH

También podría gustarte

- Prácticas de redes de datos e industrialesDe EverandPrácticas de redes de datos e industrialesCalificación: 4 de 5 estrellas4/5 (5)

- Administración de redes LAN. Ejercicios prácticos con GNS3De EverandAdministración de redes LAN. Ejercicios prácticos con GNS3Aún no hay calificaciones

- Laboratorio 2 Arquitectura Del ComputadorDocumento2 páginasLaboratorio 2 Arquitectura Del ComputadorYamir Kamell PajaroAún no hay calificaciones

- Programa No. 3 Introduccion A La Programacion Con EnsambladorDocumento10 páginasPrograma No. 3 Introduccion A La Programacion Con EnsambladorjcastanedaAún no hay calificaciones

- FINAL Practico 2Documento2 páginasFINAL Practico 2Hugo Armando RestrepoAún no hay calificaciones

- SF - AC Preguntas 1er Parcial - 32Documento13 páginasSF - AC Preguntas 1er Parcial - 32lzAún no hay calificaciones

- Diseño Del Conjunto de Instrucciones: Universidad Nacional de IngenieriaDocumento5 páginasDiseño Del Conjunto de Instrucciones: Universidad Nacional de IngenieriaAli SayedAún no hay calificaciones

- Cac Practica 1Documento5 páginasCac Practica 1willherondale2Aún no hay calificaciones

- Proyecto Codigo FinalDocumento12 páginasProyecto Codigo FinalÁngel Eduardo Godinez ManriqueAún no hay calificaciones

- Lab3 - OAC (DEBUG) 1Documento6 páginasLab3 - OAC (DEBUG) 1Samuel VillamilAún no hay calificaciones

- PRACTICA 1 Resuelta MicroprocesadoresDocumento26 páginasPRACTICA 1 Resuelta MicroprocesadoresAleXander DiiazAún no hay calificaciones

- Guia1Micro PDFDocumento7 páginasGuia1Micro PDFПривет ДругAún no hay calificaciones

- Practica 1 - MicroproDocumento10 páginasPractica 1 - MicroprorodrigoAún no hay calificaciones

- Cac P1Documento5 páginasCac P1Appetite DestructionAún no hay calificaciones

- Practica 1 - MicroproDocumento14 páginasPractica 1 - MicroproCrisAún no hay calificaciones

- Práctica 6 IMPARESDocumento3 páginasPráctica 6 IMPARESjorge quintero galindoAún no hay calificaciones

- Deber # 2 V2Documento4 páginasDeber # 2 V2Aquiles Caigo ParadoAún no hay calificaciones

- Ar QPR Act Res NuevaDocumento6 páginasAr QPR Act Res NuevauabrahaamAún no hay calificaciones

- 1ER PARCIAL 29-6-19 MDocumento3 páginas1ER PARCIAL 29-6-19 MMelani ArgüelloAún no hay calificaciones

- EdC Conv3 Dic20 v2Documento3 páginasEdC Conv3 Dic20 v2Ashley ConejoAún no hay calificaciones

- 1er Parcial 7-10-17Documento4 páginas1er Parcial 7-10-17Milagro SalinasAún no hay calificaciones

- Laboratorio#3 OACDocumento12 páginasLaboratorio#3 OACFermin OsorioAún no hay calificaciones

- Practica 2 FundamentosDocumento4 páginasPractica 2 FundamentosajgilbAún no hay calificaciones

- 2do Examen - Microcontroladores - A - Enero - Junio - 2021Documento2 páginas2do Examen - Microcontroladores - A - Enero - Junio - 2021DAVID OBRAYANT ALVARADO MART?NEZAún no hay calificaciones

- Digitales Ejercicios de MSS y ASMDocumento4 páginasDigitales Ejercicios de MSS y ASMRonny BritoAún no hay calificaciones

- PracticaDocumento11 páginasPracticaskrix 89Aún no hay calificaciones

- Guía de Ejercicios EDII 2019Documento16 páginasGuía de Ejercicios EDII 2019SergioTolayZbAún no hay calificaciones

- Solucionario Examen ParcialDocumento7 páginasSolucionario Examen ParcialAlexander Mcsorley MansillaAún no hay calificaciones

- Deber # 4 V2Documento4 páginasDeber # 4 V2smith muñozAún no hay calificaciones

- Práctica 4. Programación en Shell. Introducción A Awk.Documento9 páginasPráctica 4. Programación en Shell. Introducción A Awk.juankaten100% (1)

- Practica 4manejo de Tablas y Retardos.17301 PDFDocumento10 páginasPractica 4manejo de Tablas y Retardos.17301 PDFErickCruzAún no hay calificaciones

- Trabajo de Laboratorio 3 - 2022 - 1Documento3 páginasTrabajo de Laboratorio 3 - 2022 - 1raimarAún no hay calificaciones

- Unidad 1 Ordenar 3 Numeros de Menor A MayorDocumento8 páginasUnidad 1 Ordenar 3 Numeros de Menor A Mayorjuan david martinez parraAún no hay calificaciones

- 05-c Desde AsmDocumento10 páginas05-c Desde AsmEvelyn Medrano KariAún no hay calificaciones

- Lab3 Ee604 - Fiee UniDocumento1 páginaLab3 Ee604 - Fiee UniDavidAún no hay calificaciones

- Sol Parcial 2021Documento5 páginasSol Parcial 2021Facundo LeiteAún no hay calificaciones

- 0 E05 BD 01Documento3 páginas0 E05 BD 01Javier_Stefan_5933Aún no hay calificaciones

- Practica 10 Taller 2022Documento2 páginasPractica 10 Taller 2022LucianoLoyolaAún no hay calificaciones

- Ejercicios Tema4Documento7 páginasEjercicios Tema4Lucía Mora OrtizAún no hay calificaciones

- TrabPrac2 ACs 2016-IDocumento1 páginaTrabPrac2 ACs 2016-IKimballAún no hay calificaciones

- Practica3 VFDocumento6 páginasPractica3 VFCarlos Charly XPAún no hay calificaciones

- Taller # 2 OAC SRDocumento8 páginasTaller # 2 OAC SRDelvis Joel CruzAún no hay calificaciones

- Taller PiuveytkDocumento6 páginasTaller Piuveytkdavid estebanAún no hay calificaciones

- Informe 2 ComputadoresDocumento9 páginasInforme 2 Computadorespathy cocreAún no hay calificaciones

- Practica Codigos de Linea Utilizando MatlabDocumento8 páginasPractica Codigos de Linea Utilizando MatlabTezoquitl PantliAún no hay calificaciones

- Enunciado Laboratorio N°1 - MT325 - 2020-1Documento1 páginaEnunciado Laboratorio N°1 - MT325 - 2020-1trueAún no hay calificaciones

- Ensamblador UVMDocumento59 páginasEnsamblador UVMAbel Diaz OlivaresAún no hay calificaciones

- Pequeño Manual de Programacion HP PDFDocumento18 páginasPequeño Manual de Programacion HP PDFCristopher LlanosAún no hay calificaciones

- 1.documento Final PDFDocumento10 páginas1.documento Final PDFAlexander ChaoAún no hay calificaciones

- Practica No. 3 Ciclos-1Documento6 páginasPractica No. 3 Ciclos-1Rogelio Zamarripa TreviñoAún no hay calificaciones

- Guia de Practica 03 (DESARROLLO)Documento5 páginasGuia de Practica 03 (DESARROLLO)Paulo César Arzapalo RoqueAún no hay calificaciones

- Tarea 3 PDFDocumento2 páginasTarea 3 PDFEnriqueMaturanoAyarachiAún no hay calificaciones

- Grupo 46 Glorizgomez3Documento19 páginasGrupo 46 Glorizgomez3xavierforeroAún no hay calificaciones

- Lenguaje Ensamblador - Actividad 2Documento3 páginasLenguaje Ensamblador - Actividad 2edgar jafet murillo silvaAún no hay calificaciones

- Tarea 6Documento3 páginasTarea 6Shot PointAún no hay calificaciones

- 01 2018-2 LB2 Inf239Documento1 página01 2018-2 LB2 Inf239Luis Hernán Mesajil LópezAún no hay calificaciones

- C# en VisualDocumento52 páginasC# en VisualYazmin MoralesAún no hay calificaciones

- TP #6 - 2015Documento9 páginasTP #6 - 2015Agustin OsatinskyAún no hay calificaciones

- Problemas AVRDocumento5 páginasProblemas AVRReyner LozaAún no hay calificaciones

- Organizacion de ComputadorasDocumento5 páginasOrganizacion de ComputadorasJIMMY FRANCISCO GUIDOS SANCHEZAún no hay calificaciones

- Trabajo Seguro en Alturas PDFDocumento211 páginasTrabajo Seguro en Alturas PDFJESSICA ESCOBAR ORTIZAún no hay calificaciones

- DIAPOSITIVASDocumento14 páginasDIAPOSITIVASJESSICA ESCOBAR ORTIZ100% (1)

- Consideraciones Basicas Parte 1Documento6 páginasConsideraciones Basicas Parte 1JESSICA ESCOBAR ORTIZAún no hay calificaciones

- Actividad 2 Residuos Solidos GTC 24Documento2 páginasActividad 2 Residuos Solidos GTC 24JESSICA ESCOBAR ORTIZAún no hay calificaciones