Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Sistema de Interconexion Interna

Cargado por

José Yelko Rojas LópezDescripción original:

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Sistema de Interconexion Interna

Cargado por

José Yelko Rojas LópezCopyright:

Formatos disponibles

SISTEMAS DE

INTERCONEXION

INTERNA

INTEGRANTES:

CHUNA VALENCIA CRISTHIAN PAUL

DELGADO CHAVEZ CHRISTIAN KEVIN

JHONATHAN

GIL TESEN EDERSON JAIRO

QUIROZ CARRILLO KATHERYN MILAGROS

Pgina | 1

INDICE

DEDICATORIA.................................................................................................. 2

1.

INTRODUCCION:....................................................................................... 3

2.

MARCO TEORICO...................................................................................... 5

3.

2.1.

HISTORIA DE LOS BUSES....................................................................5

2.2.

DEFINICION DE BUS:...........................................................................6

2.3.

FUNCIONAMIENTO DE UN BUS:...........................................................6

ESTRUCTURA DE UN BUS:........................................................................9

3.1.

4.

LINEAS DE DATOS:.............................................................................. 9

3.1.1.

LINEAS DE DIRECCION:................................................................9

3.1.2.

LINEAS DE CONTROL:..................................................................9

3.2.

LINEAS DE BUS:.................................................................................. 9

3.3.

VENTAJAS Y DESVENTAJAS DE LOS BUSES:.....................................10

JERARQUIA DE BUSES:...........................................................................12

4.1.

BUS DEL SISTEMA:........................................................................... 12

4.2.

BUS LOCAL:...................................................................................... 12

4.3.

BUS DE EXPANSION O DE E/S:..........................................................13

Estndares USB.......................................................................................... 18

Tipos de conectores...................................................................................... 19

4.4.

5.

VENTAJAS DE LAS JERARQUIAS DE BUSES:......................................20

ARBITRAJE DE BUSES:............................................................................22

5.1.

METODOS DE ARBITRAJES:..............................................................22

5.1.1.

ARBITRAJE CENTRALIZADO:.......................................................22

5.1.2.

ARBITRAJE DISTRIBUIDO:...........................................................22

5.1.3.

PROTOCOLO DE ENCADENAMIENTO (DAISY CHAINING) DE DOS

SEALES:............................................................................................... 24

5.1.4.

PROTOCOLO DE ENCADENAMIENTO (DAISY CHAINING) DE TRES

SEALES:............................................................................................... 24

5.1.5.

PROTOCOLO DE ENCADENAMIENTO (DAISY CHAINING) DE

CUATRO SEALES:................................................................................. 25

5.1.6.

PROTOCOLO CON CONCESIN POR ENCUESTA (POLLING):.......26

5.1.7.

PROTOCOLO CON SEALES INDEPENDIENTES:.........................27

5.1.8.

PROTOCOLO DISTRIBUIDO:........................................................27

ANEXO.......................................................................................................... 30

LINKOGRAFA................................................................................................ 31

Pgina | 2

DEDICATORIA

A Dios

Por iluminarme durante este trabajo y por

permitirme finalizarlo con xito

A la Profesor: ING. Cesar Arellano Salazar

Por el apoyo que nos brinda da a da.

A nuestros Padres:

Por su apoyo incondicional que me brindan y

por estar siempre conmigo. A todas aquellas

personas con sed de conocimiento y deseos

de superacin, que leen hoy stas pginas y

premian el esfuerzo de este trabajo.

TODOS

Pgina | 3

1. INTRODUCCION:

En este presente trabajo realizaremos un estudio sobre el sistema de

interconexin interna de los buses para ello como primer punto

trataremos acerca de la definicin de los buses tambin hablaremos del

funcionamiento y estructura de estos. As como

unos conceptos

bsicos para conocer la jerarqua y arbitraje de los buses.

Dentro de la Arquitectura de Computadoras uno de los temas de mayor

importancia es el conocer el funcionamiento del procesador y dentro de

este se encuentra los buses. El bus representa bsicamente una serie

de cables mediante los cuales pueden cargarse datos en la memoria y

desde all transportarse a la CPU. Por as decirlo es la autopista de los

datos dentro de la PC ya que comunica todos los componentes del

ordenador con el microprocesador.

Pgina | 4

CAPITULO I:

MARCO TERICO

Pgina | 5

2. MARCO TEORICO

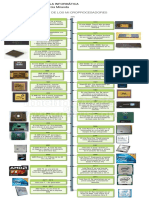

2.1.

HISTORIA DE LOS BUSES

El objetivo de conectar una tarjeta a un bus de expansin es que

sta funcione como si estuviera directamente conectada

al procesador. Con el fin de hacer factible estas caractersticas el

bus de expansin XT presentaba el mismo ancho de bus (8 bits) y

operaba a la misma velocidad de reloj (4.77 MHz) que el propio

procesador 8088.

Con

la evolucin de

los procesadores tambin

hubo

una revolucin en los buses que se haban quedado obsoletos. As

cuando en 1984 IBM presenta el PC AT (con el procesador Intel

80286) se rompi la aparentemente inquebrantable relacin entre

bus y microprocesador. Aunque en la prctica el reloj del procesador

de un AT funciona a la misma velocidad que su reloj de bus, IBM

haba abierto la puerta a la posibilidad de que este ltimo fuese ms

rpido que el reloj del bus. As pues el bus que incorpor el AT fue

de un ancho de banda de 16 bits funcionando a 8.33 Mhz. Este

enfoque de diseo no oficial se denomin oficialmente ISA (Industry

Standard Arquitecture) en 1988.

Puesto que el bus ISA ofreca algunas limitaciones En IBM se

desarroll otro tipo de bus que funcionaba a 10 Mhz y que soportaba

un ancho de banda de 32 bits. Este bus se mont en la gama PS/2.

El gran problema de este bus es que no era compatible con los

anteriores y necesitaba de tarjetas de expansin especialmente

diseadas para su estructura.

Como el mercado necesitaba un bus compatible ISA que fuese ms

rpido, la mayora de fabricantes establecieron las especificaciones

del bus EISA (Extended ISA) que ensanchaba la ruta de datos hasta

32 bits, sin embargo la necesidad de compatibilidad con ISA hizo

que este nuevo bus tuviese que cargar con la velocidad bsica de

transferencia de ISA (8.33 Mhz).

Pero la gran revolucin estaba por llegar. Por un lado los

procesadores Intel 80486 y por otro la invasin en el mercado de los

sistemas grficos como Windows hicieron necesario la aparicin de

un nuevo tipo de bus que estuviese a la altura de estos hitos. Al

manejarse grficos en color se producan grandes cuellos de botella

al pasar del procesador al bus ISA (el 80486 funcionaba a 33 Mhz y

el bus ISA a 8.33 Mhz). La solucin era enlazar el adaptador grfico

y otros perifricos seleccionados directamente al microprocesador.

Es aqu donde surgen los buses locales. Fue VESA (un organismo

de estandarizacin de dispositivos de vdeo) quin present el

primer tipo de bus local. Se le llamo VESA LOCAL BUS (VLB). Este

tipo de bus revolucion el mercado ya que permita una velocidad de

Pgina | 6

33 Mhz pudindose alcanzar una mxima de 50 Mhz y su ancho de

banda era de 32 bits (aunque en su especificacin 2.0 se alcanzan

los 64 bits).

En el ao 1992 Intel present un nuevo bus local llamado PCI, que

aunque no mejor el rendimiento del VLB, super las carencias que

presentaba este bus que estaba orientado al diseo de los

procesadores 80486. As pues el PCI se desarroll como un bus de

futuro. La velocidad de este bus era inicialmente de 20 Mhz y

funcionaba a 32 bits, aunque en la actualidad su velocidad de

transferencia alcanza los 33 Mhz y su ancho de banda llega hasta

los 64 bits. Otra caracterstica de este tipo de bus es la posibilidad

de que se le conecten tarjetas que funcionen a distintos voltajes.

2.2.

DEFINICION DE BUS:

EI bus representa bsicamente una serie de cables mediante los

cuales pueden cargarse datos en la memoria y desde all

transportarse a la CPU. Por as decirlo es la autopista de los datos

dentro de la PC ya que comunica todos los componentes del

ordenador con el microprocesador. El bus se controla y maneja

desde la CPU.

Un bus es en esencia una ruta compartida que conecta diferentes

partes del sistema como el procesador, la controladora de unidad

de disco, la memoria y los puertos de entrada, salida,

permitindoles transmitir informacin.

En arquitectura d computadores, el BUS es un sistema digital que

transfiere datos entre los componentes de un ordenador o entre

ordenadores.

2.3.

FUNCIONAMIENTO DE UN BUS:

En el bus se encuentran dos pistas separadas, el bus de datos y

el bus de direcciones. La CPU escribe la direccin de la posicin

deseada de la memoria en el bus de direcciones accediendo a la

memoria, teniendo cada una de las lneas carcter binario. Es

decir solo pueden representar 0 o 1 y de esta manera forman

conjuntamente el nmero de la posicin dentro de la memoria (es

decir: la direccin). Cuantas ms lneas haya disponibles, mayor

es la direccin mxima y mayor es la memoria a la cual puede

dirigirse de esta forma. En el bus de direcciones original haba ya

20 direcciones, ya que con 20 bits se puede dirigir a una memoria

de 1 MB y esto era exactamente lo que corresponda a la CPU.

Esto que en le teora parece tan fcil es bastante ms complicado

en la prctica, ya que aparte de los bus de datos y de direcciones

existen tambin casi dos docenas ms de lneas de seal en

la comunicacin entre la CPU y la memoria, a las cuales tambin

Pgina | 7

se acude. Todas las tarjetas del bus escuchan, y se tendr que

encontrar en primer lugar una tarjeta que mediante el envo de

una seal adecuada indique a la CPU que es responsable de la

direccin que se ha introducido. Las dems tarjetas se

despreocupan del resto de la comunicacin y quedan a la espera

del prximo ciclo de transporte de datos que quizs les incumba a

ellas.

PROCESADOR

8086

8088

80186

80188

80286

80386 SX

80386 DX

80486 DX

80486 SX

PENTIUM

PENTIUM PRO

PENTIUM II

PENTIUM III

PENTIUM IV

BUS DE DIRECCIONES

20

20

20

20

24

32

32

32

32

32

32

64

64

64

BUS DE DATOS

16

8

16

8

16

16

32

32

32

64

64

64

32

64

Este mismo concepto es tambin la razn por la cual al

utilizar

tarjetas

de

ampliacin

en

un

PC

surgen problemas una y otra vez, si hay dos tarjetas que

reclaman para ellas el mismo campo de direccin o campos

de direccin que se solapan entre ellos.

Los datos en si no se mandan al bus de direcciones sino al

bus de datos. El bus XT tena solo 8 bits con lo cual slo

poda transportar 1 byte a la vez. Si la CPU quera

depositar el contenido de un registro de 16 bits o

por valor de 16 bits, tena que desdoblarlos en dos bytes y

efectuar la transferencia de datos uno detrs de otro.

De todas maneras para los fabricantes de tarjetas de

ampliacin,

cuyos productos deben

atenderse

a

este protocolo, es de una importancia bsica la regulacin

del tiempo de las seales del bus, para poder trabajar de

forma inmejorable con el PC. Pero precisamente este

protocolo no ha sido nunca publicado por lBM con lo que se

obliga a los fabricantes a medir las seales con la ayuda de

tarjetas ya existentes e imitarlas.

Pgina | 8

CAPITULO II:

ESTRUCTURA

DE BUSES

3. ESTRUCTURA DE UN BUS:

Un bus es un conjunto de lneas independientes con una

funcin particular, usualmente, por entre 50 y 100 lneas. Se

pueden clasificar en tres grupo funcionales:

Pgina | 9

3.1.

LINEAS DE DATOS:

Proporciona un camino para trasmitir datos entre los mdulos

de sistema. El conjunto constituido por estas lneas se

denomina bus de datos; que generalmente consta de 8, 16, o

32 lneas distintas, cuyo nmero de lneas se conoce como

anchura del bus de datos.

3.1.1. LINEAS DE DIRECCION:

Seleccionan la fuente o el destino de la informacin que

hay sobre el bus de datos. La anchura del bus de

direcciones

determina

la

capacidad

de

direccionamiento de la unidad de memoria del sistema.

3.1.2. LINEAS DE CONTROL:

Se utilizan para controlar el acceso y el uso de las

lneas de datos y de direcciones.

Las seales de control trasmiten tanto ordenes como

informacin de temporizacin entre los mdulos del

sistema. Las seales de temporizacin indican la

validez de los datos y las direcciones.

3.2.

LINEAS DE BUS:

Las lneas del bus se agrupan en dos tipos genricas:

dedicadas y no dedicadas.

3.2.1. Una lnea de bus dedicada:

Se asigna de forma permanente a una funcin o a un

subconjunto de componentes del computador. Puede

ser funcional o fsica. La dedicacin fsica se refiere al

uso de mltiples buses, cada uno se conecta a un

subconjunto de mdulos. Tiene mayor rendimiento

debido a la menor contencin del bus, pero aumenta el

tamao y el coste.

3.2.2. En las lneas no dedicadas:

La informacin sobre la direccin y los datos se

transmite por el mismo conjunto de lneas utilizando una

lnea de direccin vlida. El mtodo de utilizar las

mismas lneas con objetivos diferentes se conoce como

multiplexacin en el tiempo. Aunque este sistema

P g i n a | 10

complica la circuitera y reduce el rendimiento del

computador.

3.3.

VENTAJAS Y DESVENTAJAS DE LOS BUSES:

3.3.1. VENTAJAS:

Flexibilidad del sistemas:

Facilidad

para

aadir

nuevos

componentes.

Mover perifricos entre ordenadores que

comparten el mismo bus.

Economa: las mismas conexiones compartidas

por mltiples componentes.

Manejar la complejidad partiendo del diseo:

DIVIDE Y VENCERS.

3.3.2. DESVENTAJAS:

Crea un cuello de botella:

Todo pasa a travs del bus.

El ancho de banda del bus limita la

velocidad en las transacciones entre los

componentes del sistema.

Velocidad mxima limitada:

Longitud del bus.

Nmero de dispositivos conectables.

Flexibilidad para soportar diferentes tipos

de dispositivos.

P g i n a | 11

CAPITULO III:

JERARQUIA

DE BUSES

4. JERARQUIA DE BUSES:

4.1.

BUS DEL SISTEMA:

Antiguamente los ordenadores solo utilizaban un bus nico para

conectar procesador, memoria y los mdulos de E/S.

P g i n a | 12

Sin embargo, cuando el nmero de dispositivos conectados a un

bus aumenta disminuye su rendimiento. Esto es debido a dos

motivos fundamentales:

Aumento del retardo de propagacin de las seales debido

al aumento de longitud de los conductores que dan soporte

al bus.

Incremento de demanda de acceso que se produce al

aumentar el nmero de dispositivos conectados.

Para evitar la cada de rendimiento, el sistema de buses se

jerarquiza, apareciendo dos buses ms: el bus local, y el bus de

E/S.

4.2.

BUS LOCAL:

Es de longitud pequea, de alta velocidad y adaptado a la

arquitectura particular del sistema para maximizar el ancho de

banda entre el procesador y la cach, por eso suele ser un bus

propietario. Este bus asla el trfico procesador-cach del resto de

transferencias del sistema.

P g i n a | 13

4.3.

BUS DE EXPANSION O DE E/S:

Bus ms largo y lento.

Reduce el trfico en el bus del sistema.

Standard, independiente del computador y accesible

por el usuario.

Ejemplos: ISA, PCI, USB, ATA, SCSI, VME

Para conectar los buses del sistema y de expansin se

requiere un Adaptador de Bus, dispositivo que permite

adaptar las distintas propiedades de ambos buses:

velocidad,

carcter

sncrono

o

asncrono,

multiplexacin, etc.

4.3.1. BUS ISA

Las siglas significan

INDUSTRY STANDARD

ARQUITECTURE. Apareci como un bus de 8 bits

con una velocidad de reloj de 4,77 MHz.

Hasta fines de la dcada de 1990, casi todos los

equipos contaban con el bus ISA, pero fue

progresivamente reemplazado por el bus PCI, que

ofreca un mejor rendimiento.

P g i n a | 14

4.3.2. BUS MCA

IBM

desarroll

en

1987

la

denominada

ARQUITECTURA DE BUS MICROCANAL (MCA).

Basada en ranuras de expansin 32 bits, introdujo

cambios de diseo y nuevos conceptos de gestin y

funcionamiento del bus.

El bus MCA es totalmente incompatible con los

dems y de uso exclusivo de IBM. Por ello, qued

prcticamente en desuso.

4.3.3. BUS EISA

Las siglas significan EXTENDED INDUSTRY

STANDARD ARQUITECTURE.

Diseada para competir con el bus exclusivo MCA.

Tiene caractersticas de la ISA en cuanto a su

compatibilidad y con capacidad de direccionamiento

de 32 bits.

4.3.4. BUS PCI

Las siglas significan PERIPHERICAL COMPONENT

INTERCONECT.

Interconexin a componentes perimetrales. Es de

caractersticas similares a VESA, pero se distingue

porque la conexin del bus con el microprocesador

se efecta por intermedio de un chip adicional que

simplifica y suprime las limitaciones de la conexin

directa.

4.3.5. BUS AGP

Las siglas AGP corresponden a Advanced Graphics

Port, o Puerto Avanzado de Grficos. Se trata de un

nuevo sistema para conectar perifricos en la placa

base del PC; es decir, es un nuevo bus por el que

van datosdirectamente del microprocesador al

perifrico.

Diseado exclusivamente para tratar con graficos,

AGP es un diseo de 32 bits, y trabaja a velocidades

de hasta 133MHz.

4.3.6. CONECTOR BUS LOCAL VESA(VLB)

En 1992, el bus local de VESA (VLB) fue

desarrollado por VESA (Asociacin para estndares

electrnicos y de video patrocinado por la compaa

NEC) para ofrecer un bus local dedicado a sistemas

P g i n a | 15

grficos. El VLB es un conector ISA de 16 bits con

un conector de 16 bits agregado

El bus VLB es un bus de 32 bits inicialmente

diseado para permitir un ancho de banda de 33

MHz (el ancho de banda del primer PC 486 en aquel

momento). Fue reemplazado rpidamente por el bus

PCI.

4.3.7. BUS PCI EXPRESS

Es un bus de interconexin que permite aadir

placas de expansin a un ordenador. El bus PCI

Express fue desarrollado en julio de 2002. A

diferencia del bus PCI, que se ejecuta en una

interfaz paralela, el bus PCI Express se ejecuta en

una interfaz en serie, lo que permite alcanzar un

ancho de banda mucho mayor que con el bus PCI.

Caractersticas del Bus PCI Express

El bus PCI Express se presenta en diversas

versiones (1X, 2X, 4X, 8X, 12X, 16X y 32X),

con rendimientos de entre 250 Mb/s y 8 Gb/s,

es decir, 4 veces el rendimiento mximo de

los puertos AGP 8X. Dado que el costo de

fabricacin es similar al del puerto AGP, es de

esperar que el bus PCI Express lo reemplace

en forma progresiva.

Una de las caractersticas ms interesantes

del bus PCI Express es que admite la

conexin en caliente, es decir, que puede

conectarse y desconectarse sin que sea

necesario apagar o reiniciar la mquina.

Funcionamiento

Con PCI

Express los

perifricos

son

enlazados en serie de dos en dos. Cada

enlace en serie trabaja a 250MB/s y a una

tensin de 0,8 V con una potencia dedicada

de 75W para todo el bus. Tambin requiere

menos cable. En este caso hablamos de

lnea PCI Express. Las pistas ocupan menos

espacio en las placas madres y los

conectores son ms pequeos. Los beneficios

son considerables, especialmente en los PC

porttiles y las placas madres de gama alta.

P g i n a | 16

El bus PCI Express puede ser construido

combinando mltiples lanes a fin de conseguir

un rendimiento ms elevado. Podemos

encontrar el bus PCI Express en varias

versiones; existen las versiones 1, 2, 4, 8, 12,

16 y 32 lanes. Por ejemplo, la tasa de

transferencia de un sistema PCI Express con

8 lanes (x8) es de 2 GB/s (250 x 8). El PCI

Express permite tasas de transferencia que

van de 250 Mb/s a 8 Gb/s en su versin 1.1.

Los diferentes bus PCI

PCI Express 1x ofrece una tasa de

transferencia de 250 Mb/s. Existen 1 o

dos de estos en todas las placas madre

actuales.

PCI Express 2x ofrece una tasa de

transferencia de 500 Mb/s. Este bus no

es tan comn y est reservado a los

servidores.

PCI Express 4x ofrece una tasa de

transferencia de 1000 Mb/s tambin

est reservado a los servidores.

PCI Express 16x ofrece una tasa de

transferencia de 4000 Mb/s es muy

utilizado, est presente en todas las

placas madre modernas, es el formato

estndar de las tarjetas grficas.

PCI Express 32x ofrece una tasa de

transferencia de 8000 Mb/s posee el

mismo formato que el PCI Express 16x,

a menudo es utilizado en las placas

madre de gama alta para alimentar el

bus SLI o Crossfire. Las referencias de

estas placas madre por lo general

poseen la mencin 32. Esto permite

tener dos puertos PCIexpress con

formato16 y cableados en 16 lanes, al

contrario de los SLI clsicos, cableados

en 2 x 8 lanes o Crossfire bsicos,

cableados en 1x16 + 1x4 lanes. Estas

placas madre se caracterizan tambin

por la presencia de un southbridge

P g i n a | 17

adicional, nicamente dedicado a este

bus 32x.

4.3.8. BUS PC-XT:

La IBM PC-XT original fue construida con base en el

microprocesador Intel 8088, el cual es un circuito

que trabaja con un bus interno de datos de 16 bits,

aunque su bus externo es de 8 bits. Fue as como

qued definida en 8 bits la longitud del byte y de los

primeros buses de expansin.

El slot ISA-8 es un conector con doble hilera de 31

contactos metlicos, espaciados entre s a una

distancia de 0.1 pulgadas (alrededor de 2.5 mm).

4.3.9. BUS AT:

Cuando se fabric la primera computadora AT

dotada con el procesador 80286 de Intel dado que

este circuito fue capaz de manejar palabras de 16

bits en su bus externo, duplicando potencialmente la

cantidad de informacin que poda ser transferida

entre el CPU y sus perifricos, fue necesario adaptar

la ranura de expansin para adecuarla a las nuevas

prestaciones. Sin embargo, para mantener la

compatibilidad con las tarjetas ya existentes, se

respet la forma y caractersticas del bus ISA-8, pero

se le aadi una extensin dedicada al manejo de

las seales correspondientes a los 8 bits adicionales.

Por otra parte, a las tarjetas se les aadi una hilera

adicional de terminales metlicas (36 en total, 18 por

cada lado), dando un total de 98 puntos de conexin.

Como las primeras computadoras AT utilizaban un

procesador de 6 MHz, la velocidad de intercambio

subi hasta esa frecuencia; posteriormente, cuando

surgi un CPU capaz de alcanzar los 8 MHz, IBM

declar que la velocidad estndar de operacin del

bus ISA-16 sera de esa frecuencia, puesto que no

se prevea un aumento significativo en la velocidad

de los procesadores. Esto limit la velocidad de

operacin de las tarjetas controladoras, defecto que

persiste ahora, cuando se utilizan procesadores de

200 MHz. En la actualidad, a pesar de su limitacin

P g i n a | 18

en velocidad, las tarjetas ISA-16 son las ms

empleadas a nivel mundial.

4.3.10.

Universal serial bus (USB)

El USB (Bus de serie universal), como su nombre lo

sugiere, se basa en una arquitectura de tipo serial.

Sin embargo, es una interfaz de entrada/salida

mucho ms rpida que los puertos seriales estndar.

La arquitectura serial se utiliz para este tipo de

puerto por dos razones principales:

La arquitectura serial le brinda al usuario una

velocidad de reloj mucho ms alta que la

interfaz paralela debido a que este tipo de

interfaz no admite frecuencias demasiado

altas (en la arquitectura de alta velocidad, los

bits que circulan por cada hilo llegan con

retraso y esto produce errores);

Los cables seriales resultan mucho ms

econmicos que los cables paralelos.

Estndares USB

A partir de 1995, el estndar USB se ha desarrollado

para la conexin de una amplia gama de

dispositivos.

El estndar

comunicacin:

USB1.0 ofrece

dos

12 Mb/s en modo de alta velocidad,

1,5 Mb/s de baja velocidad.

modos

de

El estndar USB 1.1 brinda varias aclaraciones para

los fabricantes de dispositivos USB, pero no cambia

los rasgos de velocidad. Los dispositivos certificados

por el estndar USB 1.1 llevan el siguiente logotipo:

P g i n a | 19

El estndar USB 2.0 permite alcanzar velocidades

de hasta 480 Mbit/s. Los dispositivos certificados por

el estndar USB 2.0 llevan el siguiente logotipo:

Si no lleva ningn logotipo, la mejor manera de

determinar si un dispositivo es de USB de alta o baja

velocidad es consultar la documentacin del

producto, siempre y cuando los conectores sean los

mismos.

La compatibilidad entre USB 1.0, 1.1 y 2.0 est

garantizada. Sin embargo, el uso de un dispositivo

USB 2.0 en un puerto USB de baja velocidad (es

decir 1.0 1.1) limitar la velocidad a un mximo de

12 Mbit/s. Adems, es probable que el sistema

operativo muestre un mensaje que indique que la

velocidad ser restringida.

Tipos de conectores

Existen dos tipos de conectores USB:

Los conectores conocidos como tipo A, cuya

forma es rectangular y se utilizan, generalmente,

para dispositivos que no requieren demasiado

ancho de banda (como el teclado, el ratn, las

cmaras Web, etc.);

Los conectores conocidos como tipo B poseen

una forma cuadrada y se utilizan principalmente

para dispositivos de alta velocidad (discos duros

externos, etc.).

Fuente de alimentacin de +5 V (VBUS) mximo 100

mA

P g i n a | 20

4.3.11.

Interfaz con el bus de expansin

Adapta las velocidades de ambos buses.

Acta como buffer de almacenamiento intermedio para

evitar la prdida de datos.

Se comunica de forma sncrona con el bus del sistema y de

forma asncrona con el bus de expansin.

4.3.12.

-

4.4.

Buses para dispositivos de distinta velocidad

Aumentan el rendimiento del sistema.

Bus alta velocidad Conexin de dispositivos de E/S

de alta velocidad.

Bus de expansin Conexin de dispositivos de E/S

lentos.

Bus de E/S externo Interconexin de discos externos

y otros dispositivos.

VENTAJAS DE LAS JERARQUIAS DE BUSES:

El bus local entre el procesador y la cach asla el trfico de E/S

del procesador.

Se puede transferir informacin entre la memoria y la E/S sin

interrumpir la actividad del procesador.

El bus de expansin reduce el trfico en el bus del sistema.

La transferencia entre cach y memoria principal se pueden

realizar de forma ms eficiente.

Se pueden realizar una transferencia de memoria cach a

memoria principal al mismo tiempo que el interfaz recibe datos

desde un dispositivo de E/S.

El procesador + cach o el coprocesador tienen la misma

prioridad en el acceso al bus que todos los dispositivos

conectados al bus de expansin de forma conjunta.

Se elimina el problema de la incompatibilidad.

Mejora el rendimiento del computador.

P g i n a | 21

CAPITULO IV:

ARBITRAJE

BUSES

DE

P g i n a | 22

5. ARBITRAJE DE BUSES:

5.1.

METODOS DE ARBITRAJES:

5.1.1. ARBITRAJE CENTRALIZADO:

En este esquema un nico dispositivo de hardware es

responsable de asignar tiempos en el bus. Como

caracterstica principal podemos decir que existe Un nico

dispositivo asigna tiempos de bus denominado controlador del

bus, dicho controlador puede estar separado o en el mismo

procesador. En una forma ms simple de verlo, se puede decir

que un rbitro centralizado selecciona uno de entre los

dispositivos que han solicitado el bus y le notifica que ahora es

el maestro del bus. Ahora bien lo interesante es explicar que

significa ser el maestro del bus, y se puede explicar con el

siguiente ejemplo:

Un maestro que desea usar el bus activa la seal

comn de peticin de bus si observa que el bus no est

ocupado.

El rbitro activa la seal de bus ocupado.

El rbitro concede el bus al maestro 1.

Si este no lo necesita se la pasa al siguiente, y as

sucesivamente hasta que llega al que solicit el Bus.

Al terminarse se desactiva esta seal de peticin de

bus, lo que hace que el rbitro desactive la seal de

concesin y la de bus ocupado.

Quizs entonces la ventaja ms significativa de este mtodo

es que hay prcticamente una sencillez implcita, ya que

P g i n a | 23

pueden aadirse tantos maestros como se quieran a la serie

de peticiones al bus. Por el contrario, la propagacin de la

seal entre los dispositivos que intentan acceder al bus es

lenta, lo que a su vez implica que la prioridad es fija, y si un

maestro falla aquellos que estn en menor prioridad (en

espera de uso del bus) se vern afectados y no tendrn

acceso al bus.

5.1.2. ARBITRAJE DISTRIBUIDO:

En este tipo de arbitraje no existe un controlador central, lo

que implica que cada mdulo contiene una determinada lgica

para controlar el acceso a los mdulos que interactan

conjuntamente para compartir el bus. Entonces podemos

encontrar dos formas de arbitrar el bus:

5.1.2.1. Arbitraje distribuido por autoseleccin:

Se emplean mltiples lneas de peticin de bus, pero

ahora cada dispositivo determina de forma independiente

si l es el solicitante de mayor prioridad sin necesidad de

un rbitro. Cada lnea de identificacin tiene asignada una

prioridad, de manera que si varios masters activan sus

lneas simultneamente, gana el de mayor prioridad. Un

mster que quiera tomar el control del bus deber activar

su lnea y comprobar el estado de las dems. La

desventaja reside en que el nmero de masters, que

pueden alojarse por lnea de arbitrajes existentes es

limitado.

5.1.2.2. Arbitraje distribuido por deteccin de colisin:

Cada dispositivo solicita de forma independiente el bus. En

caso de mltiples peticiones simultneas de bus se

produce una colisin. Una vez detectada la colisin se

aplica un esquema que determine el dispositivo que ser

maestro de bus entre las partes en colisin.

Dado que se puede dar el caso de que ms de un mdulo

desee el control del bus se requieren mtodos de arbitraje,

estos pueden ser centralizados o distribuidos.

En un esquema centralizado el controlador del bus o

rbitro es el responsable de asignar el tiempo de

utilizacin del bus.

En un esquema distribuido cada mdulo contiene la

lgica de control para acceder al bus, actuando de

forma cooperativa para compartir el recurso.

P g i n a | 24

El objetivo de ambos mtodos de arbitraje es designar un

dispositivo (UCP o mdulo de E/S) como maestro y otro

acta como esclavo.

La temporizacin contempla como se coordinan los sucesos

sobre el bus. Si es sncrona los sucesos sobre el bus estn

determinados sobre un reloj. El bus incluye una lnea de

reloj sobre la que se transmite una secuencia regular.

La temporizacin asncrona es ms simple de realizar y

verificar pero es menos flexible, y el sistema no se beneficia

de los avances que se producen en el rendimiento de sus

dispositivos. Con la temporizacin asncrona pueden

compartir el bus una mezcla de dispositivos lentos y

rpidos.

Ancho de banda (B): Mxima velocidad de transferencia en

bits/seg.

Fraccin de ancho de banda: cuantifica el grado de ocupacin de

la velocidad de transferencia de la memoria cuando se realizan

operaciones de E/S con un perifrico. Su valor est entre 0 y 1. B

perifrico / B memoria.

5.1.3. PROTOCOLO DE ENCADENAMIENTO (DAISY

CHAINING) DE DOS SEALES:

Es el protocolo centralizado ms sencillo ya que utiliza slo

dos seales encadenadas, una de peticin del bus y otra

de concesin. El master que quiere acceder al bus activa la

seal de peticin (out) y los dems masters la propagan

hasta el rbitro. El rbitro activa la seal de concesin que

es propagada por los masters que no solicitaron el acceso

al bus. El master que recibe la seal de concesin y tiene

una peticin pendiente toma el control del bus. Si un master

recibe una seal de peticin mientras est accediendo al

bus, bloquea su propagacin al rbitro hasta que finalice la

utilizacin del bus. La prioridad viene determinada por la

proximidad al rbitro.

P g i n a | 25

5.1.4. PROTOCOLO DE ENCADENAMIENTO (DAISY

CHAINING) DE TRES SEALES:

Utiliza una lnea ms que el protocolo anterior, la lnea de

ocupacin. Adems, la lnea de peticin no es encadenada

sino compartida por todos los masters a travs de una

entrada al rbitro con capacidad de O-cableada. Cuando un

master toma el control del bus activa la lnea de ocupacin.

El rbitro slo activa la lnea de concesin cuando recibe

una peticin y la lnea de ocupacin est desactivada.

Como en el caso anterior, si un master recibe la concesin

y no ha solicitado el bus, transmite la seal al siguiente

master. Un master toma el control del bus si tiene una

peticin local pendiente, la lnea de ocupacin est

desactivada y recibe el flanco de subida de la seal de

concesin.

5.1.5. PROTOCOLO DE ENCADENAMIENTO (DAISY CHAINING)

DE CUATRO SEALES:

Este protocolo permite simultanear el uso del bus por un

master con el proceso de arbitraje para la seleccin del master

siguiente. De esta forma, cuando el primer master abandona

el bus, no se pierde tiempo en el arbitraje para el siguiente

P g i n a | 26

porque ya se ha hecho, pasando directamente el master

seleccionado a realizar su transaccin, al tiempo que se

realiza la seleccin del siguiente master. Para ello se aade

una cuarta lnea al esquema anterior, la lnea de

reconocimiento.

La lnea de reconocimiento la activa un master que solicit el

bus (activ peticin) y recibi la concesin pero la lnea de

ocupacin estaba activa (bus ocupado). Cuando el rbitro

recibe la activacin de reconocimiento inhibe su actuacin, es

decir, deja de atender la seal de peticin y generar la de

concesin. El master queda en espera para ocupar el bus tan

pronto lo abandone su actual usuario, que lo har

desactivando la seal de ocupacin. Cuando esto ocurre, el

master ocupa el bus y desactiva la seal de reconocimiento,

con lo que el rbitro recupera su actuacin, procediendo a un

nuevo arbitraje entre los master solicitantes, simultneamente

con la operacin de transaccin en el bus. En la siguiente

figura hemos representado el dilogo de seales

correspondiente a una ocupacin del bus por el master M1,

seguido por el arbitraje a favor de M2 mientras M1 realiza su

transaccin, y terminando con la ocupacin del bus por M2

cuando M1 finaliza:

P g i n a | 27

5.1.6. PROTOCOLO CON CONCESIN POR ENCUESTA

(POLLING):

Este protocolo sustituye la lnea encadenada de concesin

del bus por un conjunto de lneas que permiten acceder de

forma selectiva a la direccin asignada cada master sobre

estas lneas.

5.1.7. PROTOCOLO CON SEALES INDEPENDIENTES:

Tambin denominado en estrella, utiliza una lnea de

concesin especfica para cada lnea de peticin

independiente. Esta alternativa tienen la ventaja que el

rbitro puede aplicar distintos algoritmos de decisin en

caso de peticiones simultaneas (FIFO, prioridad fija,

prioridad variable).

Adems, los retardos de propagacin de las seales son

pequeos en comparacin con las anteriores alternativas.

Tiene la desventaja del nmero elevado de lneas de

arbitraje (una por posible master). El nmero de master

queda limitado al nmero de lneas existentes.

P g i n a | 28

5.1.8. PROTOCOLO DISTRIBUIDO:

En estos protocolos la responsabilidad del arbitraje no

reside en una unidad independiente sino que se distribuye

por los diferentes masters conectados al bus.

Arbitro-i concede el bus al master Mi activando Gi si:

Mi ha activado su lnea de peticin de bus Ri,

La lnea de ocupacin est desactivada.

La lnea de entrada de prioridad Pi-1 est activada

Si el master Mi no ha activado su lnea de peticin de bus

Ri, el Arbitro-i activa la lnea de salida de prioridad Pi.

P g i n a | 29

CONCLUSIONES:

Los buses funcionan de acuerdo al dispositivo que lo solicite, ya que

existe una jerarqua de buses, para optimizar el funcionamiento de los

dispositivos del computador.

Una estructura de interconexin es un sistema digital que transfiere

datos entre los componentes de una computadora o entre

computadoras, muy parecido a una red de autopistas.

Como todo componente de un sistema digital es necesario que los

buses cuenten con un control, el cual enva rdenes que especifican las

operaciones a realizar.

La mayora de los buses estn basados en conductores metlicos por

los cuales se trasmiten seales elctricas que son enviadas y recibidas

con la ayuda de dispositivos que poseen una interfaz del bus dado y se

encargan de manejar las seales y entregarlas como datos tiles

P g i n a | 30

ANEXO

BUS AGP

BUS PCI

BUS USB

BUS PCI

EXPRESS

P g i n a | 31

BUS EISA

BUS MCA

LINKOGRAFA

http://www.fdi.ucm.es/profesor/jjruz/WEB2/Temas/EC10.pdf

http://html.rincondelvago.com/buses-de-sistema.html

http://www.fiwiki.org/images/0/01/AC_Transparencias_Buses.pdf

http://www.fdi.ucm.es/profesor/mendias/512/docs/tema7.pdf

http://ispctes.blogspot.pe/2012/07/metodos-de-arbitraje-en-un-bus.html

http://www.ecured.cu/index.php/Buses_de_expansi%C3%B3n

También podría gustarte

- Fundamentos de Redes InformáticasDe EverandFundamentos de Redes InformáticasCalificación: 4.5 de 5 estrellas4.5/5 (9)

- Fundamentos de Redes Informáticas - 2ª EdiciónDe EverandFundamentos de Redes Informáticas - 2ª EdiciónCalificación: 3 de 5 estrellas3/5 (2)

- Prácticas de redes de datos e industrialesDe EverandPrácticas de redes de datos e industrialesCalificación: 4 de 5 estrellas4/5 (5)

- Historia y Evolucion de Los Buses (Tarea)Documento9 páginasHistoria y Evolucion de Los Buses (Tarea)Yazmine Trasviña Arce50% (2)

- 01 La Motherboard y Los BusesDocumento1 página01 La Motherboard y Los BusesNicte Von GodEvilAún no hay calificaciones

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDe EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeAún no hay calificaciones

- Linea de Tiempo de La Historia de Los MicropocesadoresDocumento1 páginaLinea de Tiempo de La Historia de Los MicropocesadoresDiego Miranda67% (6)

- Código BCD, GREY, ASCIIDocumento8 páginasCódigo BCD, GREY, ASCIIhola2Aún no hay calificaciones

- Programación Básica de PLC y HMI InduniDocumento62 páginasProgramación Básica de PLC y HMI InduniEnrique Potrero100% (2)

- Unidad II Comunicacion Interna en La ComputadoraDocumento16 páginasUnidad II Comunicacion Interna en La ComputadoraYuri AnayaAún no hay calificaciones

- CASILISTODocumento40 páginasCASILISTOSthephanie CabreraAún no hay calificaciones

- Estructuras de Interconexión de Un Sistema ComputacionalDocumento29 páginasEstructuras de Interconexión de Un Sistema ComputacionalyarlensonAún no hay calificaciones

- Teoria de Buses de DatosDocumento14 páginasTeoria de Buses de DatosJesus BarriosAún no hay calificaciones

- Informe de Interconexion Interna - BusesDocumento38 páginasInforme de Interconexion Interna - BusesTatianaFloresAún no hay calificaciones

- Actividad 2 Bus de ExpansiónDocumento8 páginasActividad 2 Bus de ExpansiónAndres Cruz AlvarezAún no hay calificaciones

- Arkitectura de CompiDocumento52 páginasArkitectura de CompiJavier ReyesAún no hay calificaciones

- Qué Es Un Bus InformáticoDocumento18 páginasQué Es Un Bus InformáticoAbel GordjuaAún no hay calificaciones

- OoooooooooooooooDocumento5 páginasOoooooooooooooooapi-239410825Aún no hay calificaciones

- Sistema de Interconexión Interna - BusesDocumento31 páginasSistema de Interconexión Interna - BusesJoel SanzAún no hay calificaciones

- Buses StandardDocumento16 páginasBuses StandardCaryaxo RamaAún no hay calificaciones

- Buses de ExpansionDocumento6 páginasBuses de ExpansionKelmer Ashley Comas CardonaAún no hay calificaciones

- Clasificacion BusesDocumento6 páginasClasificacion BusesCésarAlexisTiradoRuizAún no hay calificaciones

- Sistemas Digitales 10Documento8 páginasSistemas Digitales 10Nicolás MendezAún no hay calificaciones

- TIPOS DE BUSES (Tarea Fundamento de ProgramaconDocumento8 páginasTIPOS DE BUSES (Tarea Fundamento de Programaconrichard navarreteAún no hay calificaciones

- Proyecto Parte 1 (Memorias y Perifericos)Documento7 páginasProyecto Parte 1 (Memorias y Perifericos)Maria C MoralesAún no hay calificaciones

- BusesDocumento18 páginasBusesAnabelJulianaVarhenVilelaAún no hay calificaciones

- Grupo #5 INFORME (Exposición) COMPONENTES DE HARDWAREDocumento18 páginasGrupo #5 INFORME (Exposición) COMPONENTES DE HARDWARELeonel Puerto OliveraAún no hay calificaciones

- Datos Buses y BiosDocumento8 páginasDatos Buses y BiosJoaquinE.VeronAún no hay calificaciones

- RedesDocumento6 páginasRedesFreireAún no hay calificaciones

- Como Se Comunican Los Perifericos Con La Pc.Documento10 páginasComo Se Comunican Los Perifericos Con La Pc.Caminante de Sueños100% (1)

- BUS - EcuRedDocumento12 páginasBUS - EcuReddirección de tecnologíaAún no hay calificaciones

- 6 Buses y Ranuras de ExpansiónDocumento12 páginas6 Buses y Ranuras de ExpansiónPabloAgustínPerramon0% (1)

- Tipos de Buses Por Su Clase 2Documento5 páginasTipos de Buses Por Su Clase 2api-239306233Aún no hay calificaciones

- Concepto y Funcion de BusesDocumento9 páginasConcepto y Funcion de BusesPedro Eduardo Cortez MayorgaAún no hay calificaciones

- Presentacion BusesDocumento12 páginasPresentacion BusesRodolfo Rodrii'iBlees ZolanskiìAún no hay calificaciones

- Capítulo N°3Documento2 páginasCapítulo N°3Juan Francisco Herrera y MorejonAún no hay calificaciones

- Buses de ExpansionDocumento20 páginasBuses de ExpansionChristian Acero100% (1)

- BusDocumento14 páginasBusElias RiosAún no hay calificaciones

- Arquitectura de Computadoras U2Documento15 páginasArquitectura de Computadoras U2Luis Fernando Muñoz NievesAún no hay calificaciones

- Bus PCIDocumento8 páginasBus PCIAndrés Esteban Julio ValdelamarAún no hay calificaciones

- EjemploDocumento4 páginasEjemploKevin AlbertAún no hay calificaciones

- Bus de DatosDocumento18 páginasBus de Datosxavier lopezAún no hay calificaciones

- Definición de Ranura de Expansión ISADocumento11 páginasDefinición de Ranura de Expansión ISAgabriel seelveAún no hay calificaciones

- Comunicación Interna de La ComputadoraDocumento80 páginasComunicación Interna de La ComputadorarafaelmezagAún no hay calificaciones

- Bus (Informática)Documento3 páginasBus (Informática)senorwebAún no hay calificaciones

- Exposicion BusesDocumento21 páginasExposicion BusesFranco Morales la TorreAún no hay calificaciones

- Comunicación Interna de La Computadora Unidad IIDocumento65 páginasComunicación Interna de La Computadora Unidad IIrafaelmezagAún no hay calificaciones

- BUSESDocumento8 páginasBUSESLizbeth TitoAún no hay calificaciones

- El BusDocumento8 páginasEl BusLeandro PerezAún no hay calificaciones

- Conexiones de Discos Duros IDE y Discos FlexiblesDocumento3 páginasConexiones de Discos Duros IDE y Discos Flexibleslusi danielAún no hay calificaciones

- BusesDocumento10 páginasBusesDIEGO TAPIAAún no hay calificaciones

- Bus (Informática) : ContenidoDocumento24 páginasBus (Informática) : Contenidohector blancoAún no hay calificaciones

- Sistemas de Buses de Un Computador (2021)Documento10 páginasSistemas de Buses de Un Computador (2021)Rosa Elena TanahuviaAún no hay calificaciones

- Trabajo Bus PCIDocumento15 páginasTrabajo Bus PCIRicardo Diazgranados BossioAún no hay calificaciones

- Bus de DatosDocumento8 páginasBus de DatosSatel Lo NuestroAún no hay calificaciones

- PerraDocumento12 páginasPerraelpollo91Aún no hay calificaciones

- BusDocumento9 páginasBusSergio HLAún no hay calificaciones

- Bus WariDocumento11 páginasBus WariNIK ANTONI AGUILAR SANCHEZAún no hay calificaciones

- Microcontrolador 8088Documento5 páginasMicrocontrolador 8088Calcinado ArtAún no hay calificaciones

- 3 Resumen BusesDocumento4 páginas3 Resumen BusesHinara Sánchez (Hinarish)Aún no hay calificaciones

- Bus (Informática)Documento5 páginasBus (Informática)Viktor M HernandezAún no hay calificaciones

- BusesDocumento14 páginasBusesljfjAún no hay calificaciones

- Buses 2Documento97 páginasBuses 2Oleg German YasikovAún no hay calificaciones

- Actividad 4Documento5 páginasActividad 4josue oliver caballero naviaAún no hay calificaciones

- 2 3 Manual Outlook Web ContactosDocumento12 páginas2 3 Manual Outlook Web ContactosINMAAún no hay calificaciones

- Copia de MAPA DE REGISTROS ATMEGA328PDocumento52 páginasCopia de MAPA DE REGISTROS ATMEGA328Pluis quiñonezAún no hay calificaciones

- Lenguajes de InterfazDocumento9 páginasLenguajes de InterfazLuis RamirezAún no hay calificaciones

- Seguridad en InternetDocumento64 páginasSeguridad en InternetRoberto ValenteAún no hay calificaciones

- Caracterización de Procesos de Caso de EstudioDocumento5 páginasCaracterización de Procesos de Caso de EstudioJuan Pablo Mora GomezAún no hay calificaciones

- Instituto Tecnológico de Nuevo LeónDocumento1 páginaInstituto Tecnológico de Nuevo LeónLaura Patricia Barbosa ReyesAún no hay calificaciones

- Resumen - Comunicación en Entornos DigitalesDocumento5 páginasResumen - Comunicación en Entornos DigitalesNelson Raúl Escriba MartinezAún no hay calificaciones

- Servicios1 xj4r2Documento30 páginasServicios1 xj4r2Amado MacosayAún no hay calificaciones

- ALTERADocumento3 páginasALTERADominic SantiagoAún no hay calificaciones

- Manual Mrtienda 5.x PDFDocumento136 páginasManual Mrtienda 5.x PDFOmar RodriguezAún no hay calificaciones

- Crear Informes SencillosDocumento14 páginasCrear Informes SencillosMilton Paul Lopez RamosAún no hay calificaciones

- Sistema Completo de Supervision de Carga para Grúas I3000Documento2 páginasSistema Completo de Supervision de Carga para Grúas I3000mapsingenieriaAún no hay calificaciones

- Comandos Alcom VozDocumento2 páginasComandos Alcom VozJavier Santibáñez0% (1)

- IT Data Consulting - 2017Documento42 páginasIT Data Consulting - 2017orbital23Aún no hay calificaciones

- Determinar El Tipo de Data Center Que Se Va A CrearDocumento1 páginaDeterminar El Tipo de Data Center Que Se Va A CrearRonald PaxtorAún no hay calificaciones

- Sodexo Club - Registro Desde WebDocumento5 páginasSodexo Club - Registro Desde WebSharon Leslie de la Cruz0% (1)

- Análisis Sintáctico DescendenteDocumento7 páginasAnálisis Sintáctico DescendenteMiguel Enrique Junior Zavaleta RojasAún no hay calificaciones

- Guia Padres de Familia - Matriculas 2022 - Ratificaciones v2.0Documento9 páginasGuia Padres de Familia - Matriculas 2022 - Ratificaciones v2.0Julio Cesar Otoya PeraltaAún no hay calificaciones

- Manual SigaDocumento112 páginasManual SigaAlejandra ParraAún no hay calificaciones

- Estudio de Caso 5 Seguridad y WSSRADocumento3 páginasEstudio de Caso 5 Seguridad y WSSRADaniel MartínezAún no hay calificaciones

- Ejercicios Capitulo 25Documento5 páginasEjercicios Capitulo 25leo50% (4)

- TELMEXDocumento15 páginasTELMEXFanny HernándezAún no hay calificaciones

- Angel Redondo JoseLuis FOL01 TareaDocumento13 páginasAngel Redondo JoseLuis FOL01 Tareatrianapumpum100% (1)

- Actividad Eje 2 Ingenieria Del Software IIDocumento20 páginasActividad Eje 2 Ingenieria Del Software IIHUGO ALBERTO ARDILA MOLINAAún no hay calificaciones

- Mapa en Una App InventorDocumento5 páginasMapa en Una App InventorLuis SánchezAún no hay calificaciones

- Soluciones Open Source para SeguridadDocumento14 páginasSoluciones Open Source para SeguridadedgarAún no hay calificaciones