Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Informe 4 Sin Terminar de Diseño Digital

Cargado por

Oscar GaloDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Informe 4 Sin Terminar de Diseño Digital

Cargado por

Oscar GaloCopyright:

Formatos disponibles

.

Leccin #4: Compuertas lgicas NAND y NOR.

scar Ariel Galo Soto

e-mail: galo.8493@gmail.com

Integrante 2 (Arial, 11 Pts, centrado)

e-mail: integrante2@institucin (quitar hipervnculo)

Integrante 3 (Arial, 11 Pts, centrado)

Compuerta lgica NO-OR (NOR).

RESUMEN: En el presente informe se describen

Una compuerta lgica NOR se puede implementar con

la concatenacin de una compuerta OR con una

compuerta NOT. En esta compuerta, la salida ser uno

solo si todas las entradas son cero.

las compuertas NAND y NOR, conocidas como

compuertas universales. A partir de distintos

experimentos se desea conocer la funcin lgica que

cumple cada compuerta en distintos circuitos y la

utilidad que presenta su utilizacin frente a otros tipos

de compuertas.

PALABRAS CLAVE: Compuerta lgica NO-Y

(NAND), compuerta lgica NO-O (NOR), mapas de

Karnaugh.

4 MATERIALES Y EQUIPO

1.

2.

3.

1 INTRODUCCIN

5 PROCEDIMIENTO (Jamil)

A partir de la implementacin de compuertas lgicas

universales se pueden obtener distintas funciones

lgicas equivalentes para circuitos que utilizan otro tipo

de elementos, lo que las hace muy cmodas por su

utilizacin y disponibilidad en el mercado. Mediante

estas compuertas tambin se pueden definir nuevas

funciones lgicas que pueden aplicarse a distintas

situaciones de ingeniera.

5.1 Implementacin de la compuerta Y

1.

2.

2.

3.

Se conecto una de las dos entradas de la

compuerta Y como se muestra en la figura

E1.1.

Se cambio la posicin de los conmutadores A y

B para obtener todas las combinaciones

posibles y se verifico la tabla de verdad de la

figura 1.1.

5.2 Expansin de la compuerta Y

2 OBJETIVOS

1.

Tablero

Tarjeta

Cables para conexin

3.

Conocer el comportamiento de las compuertas

lgicas NOR y NAND.

Verificar las operaciones bsicas definidas para

cada compuerta en base a las Leyes de

Morgan.

Demostrar la versatilidad de dichos elementos

al ser utilizados para obtener la misma funcin

lgica que otras compuertas.

4.

Se conecto la compuerta como muestra la

figura E1.2 y se completo la tabla de verdad

figura 1.2.

Se conectaron compuertas Y de dos entradas

para obtener una compuerta Y de 3 entradas.

Cuntas compuertas son necesarias? Se

examino la tabla de verdad en este caso en la

figura 1.3.

En la configuracin propuesta por nosotros solo

se necesitaron dos compuertas Y para formar

una compuerta Y de 3 entradas.

5.3 Verificacin de las leyes asociativas y

conmutativa

3 MARCO TEORICO

5.

Compuerta lgica NO-Y (NAND).

Una compuerta NAND (NO Y) de dos entradas, se

puede implementar con la concatenacin de una

compuerta AND o "Y" de dos entradas y una compuerta

NOT o "No" o inversora. En esta compuerta, la salida

solo ser "cero cuando todas las entradas sean uno.

6.

Mapas de Karnaugh.

Los Mapas de Karnaugh son una herramienta muy

utilizada para la simplificacin de circuitos lgicos.

Cuando se tiene una funcin lgica con su tabla de

verdad y se desea implementar esa funcin de la

manera ms econmica posible se utiliza este mtodo.

7.

Se conecto la compuerta Y como se muestra en

la figura E1.3; la lmpara indicadora I1 se

conecta para indicar F1= A(BC) y la lmpara I2

para F2= (AB)C.

Se variaron los estados de los conmutadores A,

B y C para obtener todas las combinaciones

posibles y examinamos la validez de la ley

asociativa: F1=F2. La indicacin de ambas

lmparas (I1 Y I2) debe ser idntica en cada

caso. Figura 1.4

Pruebe la validez de la ley conmutativa

cambiando entre si las conexiones. Cmo

har esto?

Esto se logra fcilmente

posiciones de las entradas.

cambiando

las

0

0

1

1

1

1

1

1

1

1

5.4 Entradas desconectadas

8.

Examine el comportamiento de la compuerta Y

cuando una de sus entradas est abierta

(desconectada) y cuando ambas estn

abiertas; Cmo interpreta esto el circuito

electrnico?

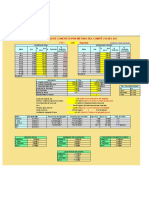

6 Tablas y graficas (Jamil las grficas)

1

1

0

0

0

0

1

1

1

1

A

0

0

0

0

1

1

1

1

1

1

0

0

1

1

0

0

1

1

Figura 1.2

B

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

C

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

1

F

0

0

0

0

0

0

0

1

Figura 1.3

Figura E1.1

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Figura 1.4

F1

0

0

0

0

0

0

0

1

F2

0

0

0

0

0

0

0

1

Figura E1.2

7 PROBLEMAS (Roberto)

1.

Exprese las siguientes afirmaciones en forma

de ecuaciones booleanas e indique cuales son

las variables booleanas.

a) Si hay suficiente calor y estamos

preparados para salir de vacaciones,

iremos a la costa

b) Si la pelcula es interesante y tengo tiempo

y dinero, ire al cine.

RESPUESTA

a) A*B = C

b) A*B*C = D

2. Repita para las siguientes afirmaciones:

Si Dany gusta de Laura y Laura gusta de Dany

y si sus padres no se oponen al enlace, habr

una boda.

RESPUESTA

A*B*C = D

3. Escriba la tabla de verdad de una compuerta Y

de 3 entradas; indique los niveles de tensin (L

y H) usando lgica positiva.

RESPUESTA

A

B

C

D

0

0

0

0

Figura E1.3

A

0

0

1

1

A

0

0

0

0

0

0

B

0

1

0

1

Figura 1.1

B

0

0

0

0

1

1

C

0

0

1

1

0

0

C

0

0

0

1

D

0

1

0

1

0

1

F

0

0

0

0

0

0

0

0

0

1

1

1

1

4.

0

1

0

1

0

0

1

1

0

0

0

0

0

1

0

1

0

0

1

1

1

Donde 1 representa un nivel alto de tensin (H)

Y 2 representa un nivel bajo de tensin (L)

Dibuje el diagrama lgico mostrando la

implementacin de las siguientes expresiones

booleanas usando compuertas Y.

F = AB(CA)

RESPUESTA

8.

5.

Implemente lo siguiente utilizando compuertas

Y.

D= (CB) (AB)

9.

Cuantas compuertas Y de 2 entradas son

necesarias para obtener una compuerta de 3

entradas? 4 entradas? n entradas?

RESPUESTA

Se necesitan 2 compuertas Y, para obtener una

de 3 entradas.

Se necesitan 3 compuertas Y, para obtener una

de 4 entradas.

Se necesitan n-1 compuertas Y, para obtener

una de n entradas.

Explique como demuestra la validez de la ley

conmutativa en el experimento, pargrafo 1.3c.

RESPUESTA

10. Qu conclusin puede extraerse de los

resultados del pargrafo 1.4?

Cuando una entrada se encuentra

desconectada la compuerta detecta una seal

de alto voltaje. Por lo tanto cuando las dos se

encuentran desconectadas la salida de la

compuerta AND estar en la posicin

6.

Una compuerta Y de dos entradas cuesta 2.5 $

y una de tres entradas cuesta 3$. Utilice el

mtodo ms barato para implementar la

siguiente ecuacin booleana.

F = ABCDE

8 ANALISIS DE RESULTADOS

Se puede observar que, debido a las diferentes

combinaciones que se pueden utilizar con las

compuertas NAND y NOR, se pueden formar nuevas

funciones lgicas capaces de facilitar algunos procesos

y construir circuitos con elementos familiares. El tiempo

de respuesta disminuy al tener circuitos ms grandes,

lo cual se debe a el tiempo de procesamiento de cada

compuerta extra.

9 CONCLUSIONES (Jamil)

10 REFERENCIAS

7.

Las variables booleanas A, B y C vistas en la

figura estn conectadas a las entradas de una

compuerta Y. Dibuje el estado de la salida en

funcin del tiempo

[1]

Morris, Mano, M. Diseo digital, 3era. ed. Pearson

Educacion, Mexico, 2003. pp 88-94.

[2]

Dr. Axel A. Barcelo A. Introduccion a la lgica

intencional,pp. 10-15, 2012. Disponible en:

http://www.filosoficas.unam.mx/1abarcelo/INTENSIONAL/2012/

260312.pdf

PROBLEMAS

1)

Dibuje el diagrama lgico usado para probar la

identidad en el prrafo 3.2e

2)

Explique, con la ayuda de un diagrama lgico,

como prob el teorema de De Morgan en el

prrafo 3.3e

Al realizar las conexiones y hacer

todas las

posibilidades de la tabla de verdad nos dimos cuenta

que las salidas son las masmas para ambos circuitos.

3)

a)

b)

c)

4)

Utilizando el Teorema De Morgan encuentre el

complemento de las siguientes funciones

booleanas:

(A+B)C

(A +BC) (B+C)+A

[A+(B+C)] (B+C)

También podría gustarte

- Analisis de Sistemas de Potencia - Unidad IDocumento48 páginasAnalisis de Sistemas de Potencia - Unidad IOscar GaloAún no hay calificaciones

- Examen Final 5SsDocumento2 páginasExamen Final 5SsOscar GaloAún no hay calificaciones

- Programacion 3cer Periodo 2013Documento8 páginasProgramacion 3cer Periodo 2013Oscar GaloAún no hay calificaciones

- Informe Roya Del CafeDocumento19 páginasInforme Roya Del CafeOscar GaloAún no hay calificaciones

- Evaluacion para Excel Basico de Infop OnlineDocumento2 páginasEvaluacion para Excel Basico de Infop OnlineOscar Galo0% (1)

- Ansipot Ejercicio Sistema Por UnidadDocumento4 páginasAnsipot Ejercicio Sistema Por UnidadOscar GaloAún no hay calificaciones

- Actividades Modulo 3 INFOP Mejora ContinuaDocumento1 páginaActividades Modulo 3 INFOP Mejora ContinuaOscar GaloAún no hay calificaciones

- Analisis MultivariableDocumento12 páginasAnalisis MultivariableOscar GaloAún no hay calificaciones

- Estandares en Sistemas de ControlDocumento35 páginasEstandares en Sistemas de ControlOscar GaloAún no hay calificaciones

- GenogramaDocumento14 páginasGenogramaOswaldo VázquezAún no hay calificaciones

- DISEÑO DE MEZCLA F'C 210Documento1 páginaDISEÑO DE MEZCLA F'C 210alexis chirre riveraAún no hay calificaciones

- Examen Parcial IIDocumento4 páginasExamen Parcial IIMiguel Llauce ChapoñanAún no hay calificaciones

- Teoría de TaludesDocumento40 páginasTeoría de TaludesCARLOS DANIEL VIELMAN CONTRERASAún no hay calificaciones

- Tarea Semana 4 EstadisticaDocumento12 páginasTarea Semana 4 EstadisticaCarolina Ceballos LeónAún no hay calificaciones

- Lógica ProposicionalDocumento6 páginasLógica ProposicionalSbsagamer09Aún no hay calificaciones

- Cartel de Competencias, Capacidades Y Desempeños Del MatemáticaDocumento4 páginasCartel de Competencias, Capacidades Y Desempeños Del MatemáticaJuanjo Mayo AtocAún no hay calificaciones

- 05.1 - Teorema de CastiglianoDocumento14 páginas05.1 - Teorema de CastiglianosantiagoAún no hay calificaciones

- Matematicas Act 3Documento7 páginasMatematicas Act 3AlbanycastrogAún no hay calificaciones

- Cyd en Concreto Armado Unidad 01 - Parte 04 - Diseño Por FlexiónDocumento33 páginasCyd en Concreto Armado Unidad 01 - Parte 04 - Diseño Por FlexiónRuben FloresAún no hay calificaciones

- Tarea 2 Control PredictivoDocumento10 páginasTarea 2 Control PredictivoYuber ZapataAún no hay calificaciones

- Resumen de AplicacionesDocumento247 páginasResumen de AplicacionesmarcoAún no hay calificaciones

- Acordes Aug y Dim PDFDocumento3 páginasAcordes Aug y Dim PDFCarolina HoyosAún no hay calificaciones

- Tarea I Cálculo VectorialDocumento7 páginasTarea I Cálculo VectorialStalyn EncarnacionAún no hay calificaciones

- ADocumento10 páginasA401 Rebeca Daniela Requena VillaseñorAún no hay calificaciones

- Teoria de Juegos Ejercicios Resueltos Final PDFDocumento28 páginasTeoria de Juegos Ejercicios Resueltos Final PDFEnrique Forner Diaz100% (1)

- Ficha de Lectura de InteresDocumento3 páginasFicha de Lectura de InteresgreysonUTPAún no hay calificaciones

- Colegio Politecnico Taller 1Documento14 páginasColegio Politecnico Taller 1Jorge Enrique Ordoñez GarciaAún no hay calificaciones

- Evaluación Matemática 4°, Unidad en Espiral 7Documento4 páginasEvaluación Matemática 4°, Unidad en Espiral 7Margareth FuentesAún no hay calificaciones

- Ejercicios VectoresDocumento2 páginasEjercicios VectoresGuillermo TellAún no hay calificaciones

- Quiz 1 Pensamiento de SistemasDocumento6 páginasQuiz 1 Pensamiento de SistemasdanielAún no hay calificaciones

- Leyes de NewtonDocumento10 páginasLeyes de NewtonDAYANNA MICHELLE MONRROY VICUÑAAún no hay calificaciones

- Vacacional - 1Documento4 páginasVacacional - 1Levi JonesAún no hay calificaciones

- Caso Práctico - PH para Media y ProporciónDocumento10 páginasCaso Práctico - PH para Media y ProporciónDALESKA BRIGHITE VILCAMANGO ACHAAún no hay calificaciones

- CALCULO INTEGRAL (Recuperado)Documento4 páginasCALCULO INTEGRAL (Recuperado)wilbert100% (1)

- Ejercicio 3Documento4 páginasEjercicio 3alexAún no hay calificaciones

- Tarea 6 Clasificacion de VigasDocumento11 páginasTarea 6 Clasificacion de VigasOmar Flores LeybaAún no hay calificaciones

- Adición y Sustracción de EnterosDocumento57 páginasAdición y Sustracción de EnterosClaudia Patricia Moreno CabreraAún no hay calificaciones

- Sesión Uve HeurísticaDocumento3 páginasSesión Uve HeurísticaReneé Severino Barzola GarcíaAún no hay calificaciones

- Guía Práctica 03 - Lógica Proposicional IDocumento22 páginasGuía Práctica 03 - Lógica Proposicional ICESAR HIPOLITO MANAYAY REYESAún no hay calificaciones