Documentos de Académico

Documentos de Profesional

Documentos de Cultura

ARG003

Cargado por

Miguel JaquetDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

ARG003

Cargado por

Miguel JaquetCopyright:

Formatos disponibles

Gracias !

Programacin Assembler de

PIC

Lnea Base

ARG003 - DVD

Aprendiendo PIC

Rango Medio

Aprendiendo PIC

Rango Medio

Clas

es

Inter

activ

TM

ARG003

es

Inter

activ

as

con

audi

o y

anim

i

Comenzando con

PIC

Rango Medio

A i t t S t d I t i

audi

o y

anim

acio

nes.

Ar qui t ec t ur a, Set de I nst r uc c i ones y

Pr ogr amac i n en Assembl er

Clases Interactivas con audio y

animaciones.

mc

Programa

electronics

mc

2005 Microchip Technology Incorporated. All Rights Reserved. Slide 1

mc

certificado por

Microchip

Technology Inc.

electronics

mc

Objetivos de la Clase j

Cuando usted finalice la clase Cuando usted finalice la clase

podr:

Entender lo bsico sobre la

arquitectura de un PIC16 arquitectura de un PIC16

Entender las instrucciones

Entender la organizacin de

Memoria Memoria

Entender como escribir programas

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 2

Entender como escribir programas

simples

Agenda g

G Arquitectura Bsica G Arquitectura Bsica

G Revisin del Set de Instrucciones

G Modos de direccionamiento y

organizacin de la Memoria organizacin de la Memoria

G Caractersticas Especiales G Caractersticas Especiales

G Metiendo las manos en

Ej i i Ejercicios

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 3

Arquitectura q

G El alto rendimiento de los microcontroladores

PIC

i t ll d t ib id l PIC

microcontroller puede ser atribuida a las

siguientes caractersticas de su arquitectura:

Arquitectura Harvard

Pipelining de Instrucciones

A hi d i t Archivos de registros

Instrucciones de un ciclo

Instrucciones de una palabra Instrucciones de una palabra

Longitud de la palabra de Instrucciones

Set de Instrucciones reducido Set de Instrucciones reducido

Set de Instrucciones ortogonal

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 4

Arquitectura Harvard q

G Arquitectura Von q

Newmann:

Busqueda de instrucciones

y datos desde una memoria y datos desde una memoria

simple

Ancho de Banda de

i Li it d operacin Limitado

G Arquitectura Harvard: G Arquitectura Harvard:

Usa dos memorias

separadas para Datos e

I t i Instrucciones

Ancho de Banda de

operacin mejorado

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 5

Permite diferentes anchos

de Bus

Pipelining de Instrucciones

G La bsqueda de instrucciones se superpone con la ejecucin de

p g

instrucciones previamente buscadas

Instruction Cycles

movlw 0x05 MAIN

f REG1

1

2

Example Program

Busca Ejecuta

T0 T1 T2 T3 T4 T5 T6 T7

Tiempo de ejecucin de una instruccin normal

call SUB1

addwf REG2

movwf REG1 2

3

4 Ejecuta

Busca Ejecuta

Busca Ejecuta

Busca Fetch

Tiempo para ejecutar

la instruccin call

incluye el nivelado del

pipeline (Flush)

movf PORTB,w SUB1 51 Busca Ejecuta ,

return

movf PORTC,w

t

SUB2

52

53

54

j

Busca Ejecuta

Busca Flush

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 6

return 54

Pipelining de Instrucciones

movlw 0x05 -

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca

T0

call SUB1

addwf REG2

movwf REG1 2

3

4

movf PORTB,w SUB1 51 ,

return

movf PORTC,w

t

SUB2

52

53

54

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 7

return 54

Pipelining de Instrucciones

movwf REG1 movlw 0x05

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1

call SUB1

addwf REG2

movwf REG1 2

3

4

Busca

movf PORTB,w SUB1 51 ,

return

movf PORTC,w

t

SUB2

52

53

54

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 8

return 54

Pipelining de Instrucciones

call SUB1 movwf REG1

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2

Tiempo de ejecucin normal de una instruccin

call SUB1

addwf REG2

movwf REG1 2

3

4

Busca Ejecuta

Busca

movf PORTB,w SUB1 51 ,

return

movf PORTC,w

t

SUB2

52

53

54

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 9

return 54

Pipelining de Instrucciones

addwf REG2 call SUB1

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2 T3

call SUB1

addwf REG2

movwf REG1 2

3

4

Busca Ejecuta

Busca Ejecuta

Busca

movf PORTB,w SUB1 51 ,

return

movf PORTC,w

t

SUB2

52

53

54

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 10

return 54

Pipelining de Instrucciones

movf PORTB,w call SUB1

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2 T3 T4

call SUB1

addwf REG2

movwf REG1 2

3

4 Nivela

Busca Ejecuta

Busca Ejecuta

Busca

Tiempo de ejecucin

del call includo el

flush del pipeline

movf PORTB,w SUB1 51 Fetch ,

return

movf PORTC,w

t

SUB2

52

53

54

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 11

return 54

Pipelining de Instrucciones

return movf PORTB,w

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2 T3 T4 T5

call SUB1

addwf REG2

movwf REG1 2

3

4 Flush

Busca Ejecuta

Busca Ejecuta

Busca

movf PORTB,w SUB1 51 Busca Ejecuta ,

return

movf PORTC,w

t

SUB2

52

53

54

j

Busca

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 12

return 54

Pipelining de Instrucciones

movf PORTC,w return

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2 T3 T4 T5 T6

call SUB1

addwf REG2

movwf REG1 2

3

4 Flush

Busca Ejecuta

Busca Ejecuta

Busca

movf PORTB,w SUB1 51 Busca Ejecuta ,

return

movf PORTC,w

t

SUB2

52

53

54

j

Busca Ejecuta

Busca

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 13

return 54

Pipelining de Instrucciones

addwf REG2 return

Bsca Instruccion

Ejecuta Instruccin

p g

Ciclos de Instruccin

movlw 0x05 MAIN

f REG1

1

2

Programa Ejemplo

Busca Ejecuta

T0 T1 T2 T3 T4 T5 T6 T7

call SUB1

addwf REG2

movwf REG1 2

3

4 Flush

Busca Ejecuta

Busca Ejecuta

Busca Busca

movf PORTB,w SUB1 51 Busca Ejecuta ,

return

movf PORTC,w

t

SUB2

52

53

54

j

Busca Ejecuta

Busca Flush

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 14

return 54

Longitud de la palabra de Instruccin

Memoria de Programa de 8 Bit

Instruccion de 8 bit sobre MCUde 8 Bits

Ejemplo: Freescale Cargar Acumulador A:

2 Localizaciones de Memoria 2 Localizaciones de Memoria

2 Ciclos de Instrucciones para Ejecutarse

G Limitado ancho

de banda

ldaa #k

1 0 0 0 0 1 1 0

k k k k k k k k

G Incrementa los

requerimientos

de Memoria

Memoria de Programa de 14 Bits

14-bitt de Instruccin sobre PIC16 MCU de 8 bits

Ej l M l Lit l l i t W Ejemplo: Mover un valor Literal al registro Wr

1 Localizacn en Memoria de Programa

1 Ciclo de instruccin para ejecutarse

mo l k

1 1 0 0 0 0 k k k k k k k k

G Buses separados Permiten diferentes

movlw k

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 15

G Buses separados Permiten diferentes

anchos

G 2k x 14 ies equivalente a 4k x 8

Concepto del Archivo de Registros

G Concepto de Archivo de

Registro: Todos los datos

de memoria son parte del

Data Memory

(Register File)

s

archivo de registro,

cualquier localizacin

puede ser operada

directamente

w f

ALU

07h

08h

09h

0Ah

D

a

t

a

B

u

d

directamente

G Todos los perifricos

estan mapeados como

una serie de regist

w f

0Ah

0Bh

0Ch

0Dh

G Set de instrucciones

Ortogonal: Todas las

instrucciones pueden

operar sobre cualquier W

0Eh

0Fh

10h

operar sobre cualquier

localizacin de memoria

de datos

G La longitud del formato

W

Opc ode d Addr ess

Decoded Instruction

from Program

Memory:

Arithmetic/Logic Address of Second

de la palabras de

instruccin permite un

direccionamiento directo

del archivo de registros

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 16

Function to be Performed

Result

Destination

Source Operand

g

Revisin del Set de

Instrucciones Instrucciones

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 17

Revisin del Set de

Instrucciones Instrucciones

0 6 7 9 13 10

File Register Address

Bit Position (0-7) Bit Position (0-7)

BSF 0x25, 3

Bit Position File Register Address

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 18

Revisin del Set de

Instrucciones Instrucciones

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 19

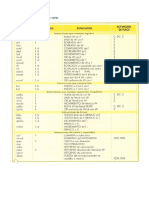

Set de Instrucciones PIC16

Operaciones Orientadas a Bits

bcf f,b Bit Clear f

Operaciones orientadas a Byte

addwf f,d Add W and f

bsf f,b

btfsc f,b

btfss f,b

Bit Set f

Bit Test f, Skip if Clear

Bit Test f, Skip if Set

andwf f,d

clrf f

clrw -

AND W with f

Clear f

Clear W

Operaciones de Control y Literales

addlw k

andlw k

Add literal and W

AND literal with W

comf f,d

decf f,d

decfsz f,d

Complement f

Decrement f

Decrement f, Skip if 0

call k

clrwdt -

goto k

Call subroutine

Clear Watchdog Timer

Go to address

incf f,d

incfsz f,d

iorwf f,d

Increment f

Increment f, Skip if 0

Inclusive OR W with f

iorlw k

movlw k

retfie -

Inclusive OR literal with W

Move literal to W

Return from interrupt

movf f,d

movwf f

nop -

Move f

Move W to f

No Operation

retlw k

return -

sleep -

Return with literal in W

Return from Subroutine

Go into standby mode

rlf f,d

rrf f,d

subwf f,d

Rotate Left f through Carry

Rotate Right f through Carry

Subtract W from f

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 20

sublw k

xorlw k

Subtract W from literal

Exclusive OR literal with W

swapf f,d

xorwf f,d

Swap nibbles in f

Exclusive OR W with f

Instrprete Visual PIC16 p

Register File Address

FF FF

Data

Bus

Literal Data from

Instruction Word

FF FF

FF FF FF FF

FF FF

00h

01h

02h

STATUS

0 1 2

FF FF

18 18 18 18

FF FF FF FF

FF FF

02h

03h

04h

w f

ALU

1111 00 0000

Z DC C

d

FF FF

05h

06h

07h

w f

ALU

FF FF

FF FF FF FF

FF FF FF FF

FF FF

08h

09h

0Ah

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 21

W Regi st er

FF FF

FF FF FF FF

0Ah

0Bh

ADDLW 0x 0A

Execute Reset

Hex

Dec

Bi n

, ,

Organizacin de la Memoria de Datos

PIC16F876/877 Mapa del Archivo de Registros

368 Bytes de Registros de Propsitos Generales

000h 080h 100h

110h

180h

190h

10Fh 18Fh

SFR SFR SFR SFR

01Fh

020h

09Fh

0A0h

110h 190h

128 Bytes

GPR

96 Bytes

GPR

80 Bytes

GPR

96 Bytes

GPR

96 Bytes

Accesses

70h 7Fh

Accesses

70h 7Fh

Accesses

70h 7Fh

0EFh 16Fh 1EFh

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 22

70h 7Fh 70h 7Fh 70h 7Fh

Bank 0 Bank 1 Bank 2 Bank 3

07Fh 0FFh 17Fh 1FFh

Organizacin de la Memoria

de Datos

INDF INDF INDF

Bank 1 Bank 2 Bank 3

080 100 180

de Datos

INDF

Bank 0

000

OPTION_REG

PCL

STATUS

TMR0

PCL

STATUS

OPTION_REG

PCL

STATUS

081

082

083

101

102

103

181

182

183

TMR0

PCL

STATUS

001

002

003

STATUS

FSR

TRISA

STATUS

FSR

STATUS

FSR

083

084

085

103

104

105

183

184

185

STATUS

FSR

PORTA

003

004

005

TRISB

TRISC

TRISD

PORTB TRISB

086

087

088

106

107

108

186

187

188

PORTB

PORTC

PORTD

006

007

008

TRISD

TRISE

PCLATH PCLATH PCLATH

088

089

08A

108

109

10A

188

189

18A

PORTD

PORTE

PCLATH

008

009

00A

INTCON INTCON INTCON

PIE1 EEDATA EECON1

PIE2 EEADR EECON2

08B

08C

08D

10B

10C

10D

18B

18C

18D

INTCON

PIR1

PIR2

00B

00C

00D

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 23

PIE2 EEADR EECON2

08D 10D 18D

Device Specific Registers

PIR2

00D

Registro de STATUS g

IRP RP1 RP0 TO PD Z DC C

bit 7 bit 0

IRP: Registro Selector de Bancos (usado para el Dir. Indirecto)

0 =Bank 0, 1 1 =Bank 2, 3

RP1:RP0: Bits Selectores de Bancos de Registros

00 =Bank 0, 01 =Bank 1, 10 =Bank 2, 11 =Bank 3

TO bit Ti t TO: bit Time-out

0 =ocurri un WDT time-out

PD: bit Power-down

0 j i d i t i SLEEP 0 =ejecucin de una instruccin SLEEP

Z: bit Cero

1 =El resultado de la operacin aritmtica es cero

DC: Digit carry / borrowbit DC: Digit carry / borrow bit

1 =Acarreo en el cuarto bit

C: Carry / borrow bit

1 =Acarreo en el Bit de Mayor Peso

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 24

1 =Acarreo en el Bit de Mayor Peso

PIC16 Modos de

Direccionamiento Direccionamiento

Accesos a Memoria de Datos G Accesos a Memoria de Datos:

Directo addwf <di r ecci n del dat o>, <d> Directo addwf <di r ecci n del dat o>, <d>

Indirecto addwf I NDF, <d>

Inmediato (Literal) movl w <const ant e>

G Accesos a Memoria de Programa:

Absoluto t <Di M > Absoluto got o <Di r . Mem. pr ogr ama>

Relativo addwf PCL, f

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 25

Direccionamiento Directo

7-bits Codificados en el OPCODE

9-bit de Direccin Efectiva 2-bits desde el

STATUS

0 0x183

f Operand

0 0 0 0 0 0

RP1

0 0

RP0

FF

FF

FF

FF

00h

01h

Bank 1 Bank 2 Bank 3 Bank 0

FF

FF

18

FF

FF

FF

1C

FF

01h

02h

03h

04h

FF FF 05h

7Ah FF FF FF FF

Bus de

di i

D

i

r

e

c

c

i

n

7Bh

7Ch

7Dh

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

disrecciones

del Archivo de

Registros

D

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 26

7Eh

7Fh

FF

FF

FF

FF

FF

FF

Direccionamiento Directo

FF FF

80h INDF

Bank 1

FF FF

Address Bank 0

INDF 00h

Address

Register File

Ejemplo: Inicializar bits 0~3 como

salida en el PORTB

FF FF

FF FF

FF FF

80h : INDF

81h : OPTION

82h : PCL

FF FF

FF FF

FF FF

INDF: 00h

TMR0: 01h

PCL : 02h

F0 F0

Registro W :

38 38

FF FF

FF FF

83h : STATUS

38 38

FF FF

FF FF

84h : FSR

85h TRISA

STATUS: 03h

FSR: 04h

PORTA 05h

00 11 00 00 00 00 00 00 00

9-Bit Direccin Efectiva:

7-bits desde la Instruccin RP0 RP1

FF FF

FF FF

FF FF

FF FF

FF FF

FF FF

85h : TRISA

86h : TRISB

87h : TRISC

PORTA: 05h

PORTB: 06h

PORTC: 07h

bsf STATUS,RP0

bts desde a st ucc 0

FF FF

FF FF

FF FF

FF FF

20h

21h

A0h

A1h

bsf STATUS,RP0

movlw b11110000

movwf TRISB

FF FF

FF FF

FF FF

FF FF

FF FF

FF FF

22h

21h

23h

A2h

A1h

A3h

bcf STATUS,RP0

clrf PORTB

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 27

Bin Dec Hex

Direccionamiento Indirecto

8-bits Desde el FSR

9-bit de Direccin

1-bit dede

STATUS

00

IRP

00 00 0x1FC 0x1FC

FSR

00 00 00 00 00 00

FF

FF

000h

001h

Bank 2,3 Bank 0,1

100h

101h

FF

1C

FF

002h

003h

004h

102h

103h

104h

FF FF

005h

0FAh

FF FF

Bus de

disrecciones

105h

1FAh

0FBh

0FCh

0FDh

FF

FF

FF

FF

FF

FF

disrecciones

del Archivo de

Registros

1FBh

1FCh

1FDh

1FEh

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 28

0FEh

0FFh

FF

FF

FF

FF

1FEh

1FFh

Direccionamiento Indirecto

00

FF

00h : INDF

Register File Address

01h : TMR0

W Register:

Example: Clear all RAM locations from 20h to 7Fh

FF

02h : PCL

03h : STATUS

FF

18

01h : TMR0

0 0 0 0 0 0 0 0 0

9-Bit Effective Address:

20

04h : FSR

20h

80

00

bcf STATUS IRP

0 0 0 0 0 0 0 0 0

FSR IRP

20h

21h

22h

movlw 0x20

movwf FSR

00

00

00

bcf STATUS,IRP

23h

7Dh

LOOP

movwf FSR

clrf INDF

incf FSR,f

00

00

80h

7Fh

7Eh

,

btfss FSR,7

goto LOOP

00

00

00

FF

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 29

80h

g

<next instruction>

FF

Organizacin de la Memoria de

Programa

G Memoria de Programa

Reset Vector 0000h

14-bits

Programa

G Memoria de Programa

se divide en cuatro

pginas de 2k14

Interrupt Vector

Pagina 0

PCH = 00h

0004h

2k

p g

G Requerido para

mantener palabras de

PCH = 00h

Pagina 1

PCH 08h

0800h

2k

mantener palabras de

instrucciones de

ejecucin en un ciclo

PCH = 08h

1000h

j

simple

G El paginado solo se

Pagina 2

PCH = 10h

2k

G El paginado solo se

toma en cuenta en los

CALL y GOTO fuera de

Pagina 3

PCH = 18h

1800h

2k

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 30

y

la pgina

PCH = 18h

1FFFh

Contador de Programa g

0 1 2 3 4 5 6 7 8 9 10 11 12

PCL PCH

P C t

0 0 0 0 0 0 0 0 0 0 0 0 0

Program Counter

G Con un PC de 13-bit de direcciona: 2

13

= 8192 words G Con un PC de 13 bit de direcciona: 2 8192 words

G Contiene la direccin de la siguiente Instruccin

Byte mas bajo accesible en mem de datos como PCL G Byte mas bajo accesible en mem. de datos como PCL

G Byate mas alto accesible via PCLATH

G Funciona libremente dentro de los lmites de la pgina

G Eventos que modifican la secuencia del PC:

Interrupciones

Instrucciones: CALL, GOTO, RETURN, RETLW, RETFIE

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 31

Cualquier instruccin que use al PC como un aperando

Direccionamiento Absoluto

0 1 2 3 4 5 6 7 8 9 10 11 12

Instrucciones CALL and GOTO :

13

Opcode 0 0 0 0 0 0 0 0 0 0 0

PC Direccionamiento Absol to (Program Memor ) G PC Direccionamiento Absoluto (Program Memory)

saltar a otra localizacin de memotia de programa fuera de

lasecuencia del PC lasecuencia del PC

Llamar a una Subrutina

G Usado por las instrucciones CALL y GOTO G Usado por las instrucciones CALL y GOTO

11-bits de los 13 bits requeridos estan codificados en la instruccin

2 bits adicionales son aportados por el registro PCLATH p p g

G Usado cuando se realiza un Salto computado

La direccin del salto es calculada por el programa

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 32

p p g

La direccin computada es escrita directamente dentro del PC

Direccionamiento Absoluto

Instruccin de 14-Bit CALL o GOTO en Memoria de Programa

0 1 2 3 4 5 6 7 8 9 10 11 12

Opcode 0 0 0 0 0

13

0 0 0 0 0 0

R i t PCLATH M i d D t

- - - 0 0 0 0 0

0 1 2 3 4 5 6 7

Registro PCLATH en Memoria de Datos

2 Bits desde el PCLATH

11-Bits desde la

I t i

0 0

11 12 0 1 2 3 4 5 6 7 8 9 10

0 0 0 0 0 0 0 0 0 0 0

2-Bits desde el PCLATH

Instruccin

Contador de Programa de 13-Bit

PCH PCH PCL PCL

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 33

Direccionamiento Absoluto

Example: Jumping to code located in a different program memory page.

0 1 2 3 4 5 6 7

Registro PCLATH Instruccin CALL en Memoria de Programa

- - - 0 0 0 0 0

0 1 2 3 4 5 6 7

0 1 2 3 4 5 6 7 8 9 10 11 12

Opcode 0 0 0 0 0

13

0 0 0 0 0 0

Registro W Contador de Programa - PCH:PCL

- 0 0

FF

Registro W Contador de Programa - PCH:PCL

0 0 0 0 0 0 0 0 0 0 0

0 0020

movlw HIGH MiSubrutina

movwf PCLATH

org 0x0020

call MiSubrotina

0 1250

MiSubrutina

org 0x1250

<aqu comienza la subrutina>

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 34

return

CALL / RETURN Stack

0020

13-bit Program Counter

movlw HIGH MySub1

movwf PCLATH 0021

0020

0020

movwf PCLATH

call MySub1

call MySub4

bsf PORTB 7 0024

0023

0022

0021

0

bsf PORTB,0

call MySub2

bsf PORTB,7

MySub1

1001

1000

0024

1

2

call MySub2

return

bsf PORTB,1

call MySub3

1002

1001

1004

1003 MySub2

3

4

call MySub3

return

bsf PORTB,2

return 1007

1006

1005

1004

MySub3

5

6

13-bit x 8-Level

Return Address Stack

return

bsf PORTB,3

call MySub2

return

1009

1008

1007

100A

MySub4

7

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 35

return 100A

Direccionamiento relativo

Para escribir al

FF FF

W Register

8-bit Data Bus

Para escribir al

PC:

E ibi b t lt

PCLATH

FF FF

Escribir byte alto en

el PCLATH

PCLATH

PCH PCL

FF FF FF FF

Escribir byte bajo en

el PCL

PCH PCL

el PCL

(PCH siempre debe ser

cargado con el PCLATH)

movlw HIGH 0x1250

movwf PCLATH

cargado con el PCLATH)

movlw LOW 0x1250

movwf PCL

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 36

Direccionamiento relativo: Tablas de

Lectura Lectura

Ejemplo: Uso de Tablas de

ORG 0x0020 ;Page 0

movlw HIGH SevenSegDecode

movwf PCLATH

j p

lectura para decodificacin

de BCD a 7-segmentos

para excitar un display a

movwf PCLATH

movlw .5

call SevenSegDecode

movwf PORTB

para excitar un display a

LED

movwf PORTB

ORG 0x1800 ;Page 3

SevenSegDecode: SevenSegDecode:

addwf PCL,f

retlw b00111111 ;0

retlw b00000110 ;1

P

I

C

M

retlw b 00000110 ;1

retlw b01011011 ;2

retlw b01001111 ;3

retlw b01100110 ;4

M

C

U

;

retlw b01101101 ;5

retlw b01111101 ;6

retlw b00000111 ;7

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 37

retlw b01111111 ;8

retlw b01101111 ;9

Gracias !

Programacin Assembler de

PIC

Lnea Base

ARG003 - DVD

Aprendiendo PIC

Rango Medio

Aprendiendo PIC

Rango Medio

Caractersticas

Especiales Revisin Especiales Revisin

mc

Programa

electronics

mc

2005 Microchip Technology Incorporated. All Rights Reserved. Slide 38

mc

certificado por

Microchip

Technology Inc.

electronics

mc

Palabra de configuracin g

CP - DEBUG WRT1 WRT0 CPD LVP BOREN - - PWRTEN WDTEN FOSC1 FOSC0

bit 0 bit 1

G Localizada en la memoria de Programa fuera del alcance del

Contador de Programa

bit 0 bit 1

G Usada para programar las caractersticas del dispositivo:

Code Protection

Oscillator Mode

Watchdog Timer

P U Ti Power Up Timer

Brown Out Reset

LowVoltage Programming Low Voltage Programming

Flash Program Memory Write

G Solo leible durante el proceso de grabacin en los PIC16

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 39

G Solo leible durante el proceso de grabacin en los PIC16

PIC16 Opciones del

Oscilador Oscilador

XT XT

HS HS

Standard frequency crystal oscillator Standard frequency crystal oscillator

High frequency crystal oscillator High frequency crystal oscillator

100kHz 100kHz -- 4MHz 4MHz

4MHz 4MHz 20MHz 20MHz HS HS

LP LP

RC RC

High frequency crystal oscillator High frequency crystal oscillator

Low frequency crystal oscillator Low frequency crystal oscillator

External RC oscillator External RC oscillator

4MHz 4MHz - - 20MHz 20MHz

5kHz 5kHz -- 200kHz 200kHz

DC DC -- 4MHz 4MHz

Un oscilador seleccionable ofrece mayores

INTRC INTRC Internal RC oscillator Internal RC oscillator 4 or 8 MHz 4 or 8 MHz 2% 2%

G Un oscilador seleccionable ofrece mayores

posibilidades al diseador:

LP Oscilador de baja frecuencia LP Oscilador de baja frecuencia

RC or INTRC provee una solucin de ultra bajo costo

XT optimizado para la mayoria de las frecuencias de oscilador p p y

comunmente usadas

HS optimizado para excitar cristales de alta frecuencia

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 40

G Son pautadas solo las gamas de velocidades

POR, OST, PWRT , ,

G POR: Power On Reset

C MCLR t d V Con MCLR conectado a V

DD

,

es generado un pulso de

Reset cuando es detectada la

subida de Vdd subida de Vdd

G PWRT: Power Up Timer

Maniene al dispositivo p

Reseteado por 72ms

(nominal) (despues del POR)

G OST: Oscillator Start-up G OST: Oscillator Start-up

Timer

Mantiene al dispositivo

R t d 1024 i l Resteado por 1024 ciclos

para permitir al cistral

estabilizar su frecuencia y

amplitud; no activo en modo

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 41

amplitud; no activo en modo

RC ; usado despues del POR

o al despertar del SLEEP

Modo Sleepp

G El procesador puede ser puesto en Modo Bajo

consumo por medio de la ejecucin de una co su o po ed o de a ejecuc de u a

instruccin SLEEP

El oscilador del sistema es detenido

El t d d l d t id (di tti ) El estado del procesador es mantenido (diseo esttico)

Watchdog timer continua funcionando, si esta habilitado

Minima corriente de mantenimiento (0.1 - 2.0A typical)

Eventos que despiertan al procesador del modo SLEEP

MCLR

WDT

Pulso sobre el MCLR (pulled low)

Watchdog Timer lleg a final de cuenta

( yp )

WDT

INT

TMR1

ADC

Watchdog Timer lleg a final de cuenta

INT sobre el pin de iterrupcin

Interrupcin del Timer 1 (or also TMR3 on PIC18)

Interrupcin por final de conversin del A/D

CMP

CCP

PORTB

Interrupcin por cambio de la salida del Comparador

Evento en la entrada de captura

Interrupcin por cambio en el PORTB

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 42

SSP

PSP

Interrupcin en el Synchronous Serial Port (I

2

C Mode) Start / Stop Bit detect

Lectura /Escritura en el PSP

Watchdog Timer g

G Ayuda a recuperarse del mal funcionamiento del software

U f i i il d RC b l hi G Usa par funcionar su propio oscilador RC sobre el chip

G WDT es borrado po la instruccin CLRWDT

G Habilitado el WDT no puede ser desactivarse por software G Habilitado el WDT no puede ser desactivarse por software

G el desborde del WDT resetea al dispositivo

G Perodo del time out esProgramable : 18ms to 3.0s typ

G Opera en modo SLEEP; sobre el time out, despierta la CPU

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 43

BOR Brown Out Reset

G Cuando se produce una variacin p

del voltaje, Resetea al dispositivo

G Previene operaciones errticas o

inesperadas

G Elimina la necesidad de un circuito

BOR externo

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 44

PBOR Programmable

Brown Out Reset Brown Out Reset

G Configuracin opcional (seteado en la g p (

programacin)

No puede ser habilitado/ deshabilitado por software p p

G Cuatro puntos seleccionables BV

DD

:

2 5V MinimumV

DD

for OTP PICmicro

MCUs 2.5V Minimum V

DD

for OTP PICmicro MCUs

2.7V

4.2V

4.5V

G Para otros thresholds usar un supervisor de G Para otros thresholds,usar un supervisor de

CPU externo (MCP1xx, MCP8xx/TCM8xx, or

TC12xx)

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 45

TC12xx)

(P)BOR Brown Out Reset

G Mantiene al PIC

MCU en reset hasta ~72ms despues que V

DD

subi por

encima delvalor de threshold

( )

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 46

PLVD Detector de Bajo

Voltaje Programable Voltaje Programable

G Es mejor que un

V

DD

LVDIN

LVDCON

brown out

G 16 puntos

LVDCON

G 16 puntos

seleccionables:

1 8V up to 4 5V 1.8V up to 4.5V

in 0.1 to 0.2V

steps

LVDIF

steps

External analog

input

G conectado al V

REF I t

LVDIN

V

REF

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 47

G conectado al V

REF Interno

Programacin Serie en

Circuito ICSP Circuito ICSP

G Solo requiere 2 pines para ser

d

Pin Pin

V

PP

Function Function

ProgrammingVoltage =13V

programado

G Conveniente para hacer programacin

en sistemas

V

PP

V

DD

V

SS

RB6

Programming Voltage 13V

Supply Voltage

Ground

Clock Input

Calibration Data

Serialization Data

G Suportado por MPLAB

PM3 & ICD2

RB7 Data I/O & Command Input

MCLR/V

PP

V

DD

V

DD

Application PCB

MCLR/V

PP

V

DD

ICSP Connector ICSP Connector

V

SS

RB6

RB7

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 48

To application circuit

Isolation

circuits

I/O Ports

G Alta capacidad de corriente

G Pueden excitar directamente un LED

G Directa manipulacin de bits

C d Pi d di i d G Cada Pin puede ser direccionado

independientemente por software

G Todo los pines tiene proteccin ESD

G Pin RA4 es open drain

G Todos los pines I/O por dufault son entradas(Alta impedancia) sobre el

arranque arranque

G Todos los pines estan multiplexados sobre entradas analogicas sobre el

arranque (de los dispositivos que las tengan)

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 49

Pin I/O Diagrama

Conceptual Conceptual

Bit 1 of TRISB

Register

1 = RB1 is input

PORTB

Bit 1

Latch

Write

Operation

movwf PORTB

p

0 = RB1 is output

RB1

Bit 1 of

D t B Data Bus

Read Read

Operation

movf PORTB,w

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 50

I/O Ports

G Bit n en TRISx controla la direccin

d l d t Bit l PORT del dato Bit n en el PORTx

G 1 = Entrada 0 = Salida

2006 Microchip Technology Incorporated. All Rights Reserved. 101 ASP Slide 51

G 1 = Entrada, 0 = Salida

Gracias !

Programacin Assembler de

PIC

Lnea Base

ARG003 - DVD

Aprendiendo PIC

Rango Medio

Aprendiendo PIC

Rango Medio

Gracias ! Gracias !

Thank You

Traducido por:

Andrs Ral Bruno Saravia

RTC Argentina

mc

Programa

electronics

mc

2005 Microchip Technology Incorporated. All Rights Reserved. Slide 52

mc

certificado por

Microchip

Technology Inc.

electronics

mc

También podría gustarte

- Primer Curso de Cracking de Ricardo Narvaja CompletoDocumento344 páginasPrimer Curso de Cracking de Ricardo Narvaja CompletoJorge Bellido Galea100% (1)

- Guía Cosimir PDFDocumento41 páginasGuía Cosimir PDFEli TorresAún no hay calificaciones

- Manual ProteusDocumento27 páginasManual ProteusMarcelo RojasAún no hay calificaciones

- Guía Jaba de Programación para Las CalculadorasDocumento30 páginasGuía Jaba de Programación para Las CalculadorasAnonymous lSEnEklZ7Aún no hay calificaciones

- Manual de Small BasicDocumento364 páginasManual de Small Basicjokinb100% (3)

- Repertorio PBASICDocumento4 páginasRepertorio PBASICCRISTIAN RAMON MARTINEZ AMADORAún no hay calificaciones

- Libreria Retardos en MPLABDocumento4 páginasLibreria Retardos en MPLABFabian GuarinAún no hay calificaciones

- PIC CompilerDocumento22 páginasPIC CompilerJhonatan MartínezAún no hay calificaciones

- Manual Básico GambasDocumento36 páginasManual Básico GambasCindy FigueroaAún no hay calificaciones

- Programación Estructura - OdtDocumento4 páginasProgramación Estructura - OdtJulio ManuelAún no hay calificaciones

- Ejercicio Auto - Bat Porceso Batch16Documento7 páginasEjercicio Auto - Bat Porceso Batch16Edgar Tuco VillalobosAún no hay calificaciones

- Control de Flujo C#Documento25 páginasControl de Flujo C#Bolivar Orbe RoblesAún no hay calificaciones

- PerlDocumento40 páginasPerlRicardo Palacio PeñaAún no hay calificaciones

- Robotica Reporte 1Documento18 páginasRobotica Reporte 1Ruben AvalosAún no hay calificaciones

- Curso PicDocumento54 páginasCurso Picance2Aún no hay calificaciones

- Entrenador para Micro Control Ad or Con PBPDocumento56 páginasEntrenador para Micro Control Ad or Con PBPbandusAún no hay calificaciones

- Informe de Practica2Documento13 páginasInforme de Practica2Bryan MdloAún no hay calificaciones

- Introduccion A Small BasicDocumento82 páginasIntroduccion A Small BasicSergio HdzAún no hay calificaciones

- Palabras ClaveDocumento15 páginasPalabras ClavealexisAún no hay calificaciones

- 00 Excel VBADocumento26 páginas00 Excel VBAJavier MallorquínAún no hay calificaciones

- Prog-121 PROGRMAMACIÓN IDocumento7 páginasProg-121 PROGRMAMACIÓN ISamy SosaAún no hay calificaciones

- Programacion MELFA IVDocumento25 páginasProgramacion MELFA IVJaime HdzAún no hay calificaciones

- 10 Bits en BCDDocumento6 páginas10 Bits en BCDJosé MiguelAún no hay calificaciones

- Programación 1º DAMDocumento47 páginasProgramación 1º DAMAndyAún no hay calificaciones

- Estructuras de Control en Transact SQLDocumento4 páginasEstructuras de Control en Transact SQLYuri Neil Farfán MaitaAún no hay calificaciones

- Instruciones Del Pic 16f84Documento7 páginasInstruciones Del Pic 16f84Antony Zamora VilcaAún no hay calificaciones

- Garmin Etrex Venture Manual SPDocumento0 páginasGarmin Etrex Venture Manual SPlindonlosadaAún no hay calificaciones

- Control de Lectura (U-2)Documento14 páginasControl de Lectura (U-2)Felipe Guerrero100% (1)

- TALLER 5 Usando Lenguaje MelfaBasicDocumento10 páginasTALLER 5 Usando Lenguaje MelfaBasicWilmer MeloAún no hay calificaciones

- Comandos Batch en WindowsDocumento97 páginasComandos Batch en WindowsantornioAún no hay calificaciones