Documentos de Académico

Documentos de Profesional

Documentos de Cultura

P1 Ac Isi355 20112

Cargado por

DEABELKINGTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

P1 Ac Isi355 20112

Cargado por

DEABELKINGCopyright:

Formatos disponibles

1

DepartamentodeIngenieradeSistemas

FacultaddeIngeniera

UniversidaddeAntioquia

ArquitecturadeComputadoresyLaboratorioISI355(20112)

PrcticaNo.1

Diseoeimplementacindeunaunidadaritmticolgica(ALU)

1. Objetivo

Aplicarelprocesodediseodesistemasdigitalescombinacionales.

Emplearherramientasdesoftwareparaeldiseoylasimulacindesistemasdigitales.

2. Descripcin

En esta prctica se disear y simular un modelo combinacional de una unidad

aritmticolgica (ALU), siguiendo un estilo de diseo jerrquico, partiendo de

componentesbsicosparaluegoimplementarotrosmscomplejos.

LaALUesunodeloscomponentesfundamentalesdeuncomputadoryaqueseencarga

derealizaroperacionesaritmticasylgicassobredatosdeentradaovaloresproducidos

durantelaejecucindelosprogramas.SusmbolosemuestraenlaFigura1.

Figura1.SmboloquerepresentaunaALU

ElsentidoylafuncionalidaddelassealesdelaALUdelaFigura1eselsiguiente:

a,b: Operandosdeentrada.

ALUoperation: Sealdecontrolqueordenalaoperacinarealizarsobrelosoperandos

deentrada.

Result: Resultadodelaoperacin.

2

Zero: Salidaqueseactiva(seponeen1)cuandoResultesigualacero.

Overflow: Salida que se activa (se pone en 1) cuando la operacin produce un

desbordamiento.

Como la arquitectura MIPS que vamos a estudiar en la segunda parte del curso tiene un

tamao de palabra de 32 bits, construiremos una ALU con operandos de este tamao.

Para lograr este propsito, debemos permitir que la ALU soporte las operaciones AND,

OR,NOR,suma,restayactivesiesmenorque(setonlessthan,SLT)

1

.

GraciasalaregularidaddelasoperacionesquerealizaunaALU,unaALUconoperandos

de 32 bits puede construirse conectando 32 ALUs de 1 bit. Por lo tanto, seguiremos un

estilo diseo estructural y jerrquico, partiendo de componentes simples para lograr

otros ms complejos, y as hacer manejable la complejidad del problema. El proceso de

diseodelaALUde32bitsempieza,entonces,poreldiseodeunaALUde1bit.

ALUde1bit

LasoperacioneslgicasANDyORarealizarporlaALUsonmuysimplesporquemapean

directamente a componentes de hardware bsicos. La unidad lgica de 1 bit para las

operacionesANDyORtienelaformadescritaenelFigura2.Elmultiplexorseencargade

dirigiralasalidaelresultadodelaoperacinelegidasobrelosoperandosdeentrada.

Figura2.Unidadlgicade1bitparalasoperacionesANDyOR

Paraimplementarlaoperacindesumarequerimosdedosentradasparalosoperandosy

una salida para el resultado, adems de una entrada y una salida extras que harn las

veces de acarreos de entrada y salida, respectivamente. El objetivo es construir un

sumadorcompletode1bit,comoelquesemuestraenlaFigura3.

Conociendoelcomportamientodelaoperacindesuma,podemosconstruirunatablade

verdad que relaciona las entradas y salidas del sumador completo de 1 bit, tal como se

muestra en la Tabla 1. A partir de esta tabla, y empleando los mapas de Karnaugh, es

posible obtener expresiones lgicas minimizadas para las dos salidas del sumador

completode1bit(CarryOutySum).

1

Laoperacinsetonlessthancomparalosoperandosdeentrada,produciendoun1enlasalidaResultcuandoa

seamenorqueb(a<b).Encualquierotrocaso,produceun0.

3

Figura3.Vistadealtoniveldelsumadorcompletode1bit

Combinando el sumador completo de 1 bit con los elementos mostrados en la Figura 1

para realizar las operaciones lgicas AND y OR, y expandiendo el multiplexor para dar

cuentadelastresoperacionesposibles,obtenemosunaALUde1bitquepuederealizar

las operaciones suma, AND y OR, tal como se muestra en la Figura 4. Ahora la entrada

Operation requiere de 2 bits, y su codificacin se hace explcita en la misma figura. Si el

diseador desea agregar ms operaciones a la ALU, debe expandir el multiplexor de

salidaysuslneasdeseleccin,ademsdeagregarloscomponentesdigitalesnecesarios

paraimplementarlasnuevasoperaciones.

Tabla1.Relacindeentradasysalidasparaelsumadorcompletode1bit

Figura4.ALUde1bitquerealizalasoperacionessuma,ANDyOR

4

La operacin de resta equivale a la de suma usando la versin negativa de uno de los

operandos. Esta es la manera como la operacin de resta se implementa mediante un

sumador.Porejemplo,paracalcularab,podramosemplearelsumadorcompletode1

bit haciendo la operacin a + (b). Los nmeros negativos se representan usando el

complementoados,elcualsecalculainvirtiendocadabitdelnmeroyluegosumndole

1.Porlotanto,esvlidoescribir:

ab=a+(b)=a+(b+1)

Para lograr que la ALU de 1 bit pueda restar, debemos tener la posibilidad de invertir la

entrada b y sumarle 1. Para invertir la entrada b podemos agregar una puerta NOT, y

usar un multiplexor para elegir entre el valor de b y su complemento, tal como se

muestra en la Figura 5, en donde la nueva seal Binvert es la seal de control de este

multiplexor. Para sumar el 1 que demanda el complemento a dos en caso de una

operacin de resta, podemos fijar un 1 en la entrada CarryIn, logrando el efecto

deseado.

Figura5.ALUde1bitquerealizalasoperacionessuma,resta,AND,OR

ParaimplementarlaoperacinNORpodemosreutilizarmuchodelhardwaredelaALUde

1bitdelaFigura5.RecordandoelteoremadeDeMorgan:

(a+b)=ab

Vemos que NOT (a OR b) equivale a (NOT a) AND (NOT b), y para calcular esto ltimo

disponemos de una puerta AND y del valor NOT b, de modo que slo requerimos del

complementodea.ParainvertirlaentradaapodemosagregarunapuertaNOT,yusarun

multiplexor para elegir entre el valor de a y su complemento, mediante la seal de

control Ainvert, tal como se muestra en la Figura 6. Por lo tanto, para realizar la

5

operacin NOT (a OR b) elegimos los valores a (haciendo Ainvert = 1) y b (haciendo

Binvert = 1), y tomamos como resultado aquel que produce la puerta AND. As

completamosunaALUde1bitquepuederealizarlasoperacionessuma,resta,AND,ORy

NOR,lacualseilustraenlaFigura6.

Figura6.ALUde1bitquerealizalasoperacionessuma,resta,AND,ORyNOR

ALUde32bits

LaALUde32bitssepuedeconstruirapartirdelencadenamientode32ALUsde1bit,tal

comoseilustraenlaFigura7,endondecadaALUde1bitaportaunbitalresultadode32

bits.ObservequeelacarreodesalidadelaALUquecalculaelbitmenossignificativodel

resultado(ALU0)sepropagaatravsdetodoelsumador.

AndebemoslograrquelaALUrealicelaoperacinsetonlessthan(SLT).Recordemos

queestaoperacinproduceun1cuandoa<b,y0enotrocaso.Porlotanto,enelcaso

deunaALUde32bits,laoperacinSLTajustatodoslosbitsdelresultadoa0,exceptoel

menossignificativo,elcualseajustadeacuerdoalresultadodelacomparacin.Paraque

laALUpuedarealizarlaoperacinSLT,esnecesarioexpandirelmultiplexordesalidade

laFigura6agregndoleunaentradaparaproducirelresultadodelaoperacinSLT.Esta

nueva entrada se denomina Less y se usa solamente en la operacin SLT, tal como se

puedeobservarenlaFigura8.

De la descripcin previa de la operacin SLT, la entrada Less de los 31 bits ms

significativosdelaALUdebeconectarsea0,yaqueestosbitssonsiemprecero.Parael

bitmenossignificativodelresultadodelaoperacinSLT,necesitamosquesea1sia<b.

Observe que si se sustrae b de a, y la diferencia es negativa, entonces a < b. De manera

que si se realiza la operacin a b, basta con analizar el bit de signo del resultado (1

significanegativo,0significapositivo)paraconocerelresultadodelaoperacinSLT.

6

Figura7.ALUde32bitsconstruidaapartirde32ALUsde1bit

Figura8.ALUde1bitquerealizalasoperacionessuma,resta,AND,ORyNORyconunaentrada

directaparalaoperacinSLT

Para conformar el resultado de la operacin SLT necesitamos tomar el bit de signo del

resultadodelaoperacinab,elcualcorrespondealasalidadelsumadorcompletode1

bitdelaALUquecalculaelbitmssignificativodelresultado.LaFigura9ilustraelnuevo

diseo de la ALU de 1 bit necesaria para calcular el bit ms significativo del resultado.

7

Aqu,lasalidadelsumadorcompletode1bitsellevaalasalidaSet,usadasolamentepor

la operacin SLT. Como se necesita una ALU especial para el bit ms significativo,

tambin se considera aqu la lgica necesaria para la deteccin de la condicin de

desbordamiento (bloque Overflow detection), que calcula la salida Overflow. El

desbordamiento ocurre cuando el resultado de una operacin no puede representarse

con el hardware disponible. Por ejemplo, cuando se suman dos nmeros de 32 bits el

resultadopuederequerirde33bitsparaserrepresentadocorrectamente.Laausenciade

este bit extra significa que cuando ocurre un desbordamiento, el bit de signo del

resultadoesrealmenteelbitmssignificativodelmismo.LalgicadelbloqueOverflow

detectionsepuedeimplementardemuydiversasmaneras.

Figura9.ALUde1bitquerealizalasoperacionessuma,resta,AND,ORyNOR,conunaentradayuna

salidadirectasparalaoperacinSLT

La ALU de 32 bits capaz de realizar tambin la operacin SLT se construye como se

muestraenlaFigura10.Los31bitsmenossignificativosseimplementanconlaALUde1

bitdelaFigura8,mientrasqueelbitmssignificativoseimplementaconlaALUde1bit

delaFigura9.

La salida Zero de la ALU de la Figura 1 es una salida de 1 bit que se activa cuando el

resultado es igual a cero. Tal como se muestra en la Figura 11, esta condicin se detecta

medianteelbloqueZerodetection,elcualseencargadeanalizarelresultadoproducido

porlaALUde32bits,paragenerarlasalidaZero.

Considerando la Figura 10, observe que cada vez que deseamos que la ALU realice la

operacin de resta es necesario ajustar la entrada Binvert a 1 y asegurarnos de que el

acarreo de entrada de la ALU que calcula el bit menos significativo del resultado sea

igualmente 1. Cuando la ALU realiza las dems operaciones, ambas lneas de control

deben ser 0. Por consiguiente, podemos simplificar el control de la ALU mediante la

combinacin de las seales CarryIn (de la ALU que calcula el bit menos significativo del

8

resultado)yBinvertenunasolalneadecontrolllamadaBnegate,queser1cuandola

ALUdebacalcularunaresta,y0cuandolaALUdebarealizarotraoperacin.Demanera

similar, podemos combinar la seal Ainverter, la seal Bnegate y la seal de 2 bits

Operation en sola una seal de control de 4 bits para la ALU, que le indica calcular las

operaciones suma, resta, AND, OR, NOR y SLT, con la codificacin que se muestra en la

Tabla2.EnlaFigura11seilustralaformadefinitivadelaALUde32bits.

Figura10.ALUde32bitsquerealizalasoperacionessuma,resta,AND,OR,NORySLT

Tabla2.ValoresdelaslneasdecontroldelaALUde32bits(Ainvert,BnegateyOperation(2))ysu

correspondientefuncin

Figura11.ALUde32bitsquerealizalasoperacionessuma,resta,AND,OR,NORySLT,consalidasZero

yOverflow

3. Procedimiento

Cadagrupodetrabajoseguirladescripcindelnumeralanteriorparaimplementaruna

ALU de 32 bits. El diseo se har siguiendo un estilo de diseo estructural en el que se

diseanbloquesbsicosqueluegosoninstanciadosparacrearotrosmscomplejosyde

mayornivelenlajerarquadediseo.

Para el diseo y simulacin de la ALU de 32 bits se debe emplear Logisim, una

herramientagrfica,decdigoabierto,paraeldiseoysimulacindecircuitosdigitales.

Parafamiliarizarseconsuusoserecomiendaseguireltutorialparaprincipiantesdelque

disponeyconocerlaestructuradelaguadeusuariopararecurriraellacadavezquesea

necesarioresolverunadudasobresuempleo.

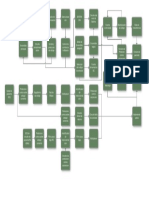

Laestructuraaniveldebloques(endiferentesnivelesdelajerarquadediseo)quedebe

tenerlaALUde32bitseslasiguiente:

ALU32bits(Figura1)

ALU1bit(Paralos31bitsmenossignificativos.VerFigura8)

ALU1bit(Paraelbitmssignificativo.VerFigura9)

10

Overflow detection (Bloque para detectar el desbordamiento en el bit ms

significativo.VerFigura9)

Zerodetection(BloqueparagenerarlasalidaZero.VerFigura11)

Sumadorcompletode1bit(BloqueparaimplementarlasALUsde1bit.VerFigura3)

Multiplexor4:1(ParaelegirelresultadodelaoperacindelasALUsde1bit)

Para el diseo del sumador completo de 1 bit se deben obtener las expresiones lgicas

minimizadasparasussalidasempleandomapasdeKarnaugh,partiendodeladescripcin

funcionalquesemuestraenlaTabla1.

LaimplementacindelosbloquesOverflowdetectionyZerodetectionsedeberealizar

mediantecompuertaslgicasbsicas,documentandoampliamentesudiseo.

LosdemselementosnecesariosparaimplementarlaALUde32bitsserntomadosdela

bibliotecadecomponentesdeLogisim.

LaALUde32bitstienequesersimuladaexhaustivamenteconlamismaherramientapara

verificarsucorrectofuncionamiento.Especialatencinsedebedaralaverificacindela

deteccincorrectadelascondicionesdedesbordamiento.

4. Informe

Cada equipo debe realizar un informe escrito que incluya una descripcin completa del

procesodediseodelaALUde32bits,losesquemticosdelosdiferentescomponentes

del diseo, una simulacin exhaustiva del mismo, y las observaciones y conclusiones del

trabajo.

5. Sustentacin

Cada equipo debe demostrar un dominio completo del desarrollo de la prctica. El

profesor plantear preguntas para evaluar los conocimientos adquiridos, cubriendo los

siguientesaspectos:

Diseojerrquicodecircuitoscombinacionales.

SimplificacindeexpresioneslgicasmediantemapasdeKarnaugh

Deteccindeldesbordamientoenoperacionesaritmticas.

ManejodelaherramientaLogisim.

11

6. Evaluacin

El informe escrito debe enviarse por correo electrnico al profesor

(farivera@udea.edu.co) antes de la fecha y hora por l designada. El proyecto Logisim

coneldiseodeALUsedebeenviarcomoadjuntoalinforme.Lasustentacinseharen

elhorarioestipuladoparalarealizacindelasprcticas.Elinformetieneunpesodel30%

enlacalificacindelaprctica.Lasustentacin,porsuparte,tieneunpesodel70%.

7. Materialdesoporte

LaherramientaLogisimsepuededescargaraqu:

http://ozark.hendrix.edu/~burch/logisim

También podría gustarte

- S3002302 PDFDocumento319 páginasS3002302 PDFDEABELKINGAún no hay calificaciones

- Ejemplos YaccDocumento9 páginasEjemplos YaccDEABELKINGAún no hay calificaciones

- Problemas de Diseño 2examenDocumento12 páginasProblemas de Diseño 2examenDEABELKINGAún no hay calificaciones

- RESUMEN Caps. 1 y 2 Metodología de La InvDocumento7 páginasRESUMEN Caps. 1 y 2 Metodología de La InvDEABELKINGAún no hay calificaciones

- Resumen Capitulo 6 CCNA2Documento8 páginasResumen Capitulo 6 CCNA2DEABELKINGAún no hay calificaciones

- Tutorial - Jailbreak Untethered de iOS 5.1Documento13 páginasTutorial - Jailbreak Untethered de iOS 5.1DEABELKINGAún no hay calificaciones

- Buffer OverflowDocumento23 páginasBuffer OverflowCynthiaEscobarAún no hay calificaciones

- Guía de Ejercicios para El Laboratorio Nº3Documento3 páginasGuía de Ejercicios para El Laboratorio Nº3DEABELKINGAún no hay calificaciones

- Resumen ExposicionDocumento10 páginasResumen ExposicionELAYMI NICOLE RUIZ SOTOAún no hay calificaciones

- Manual Windows 10Documento18 páginasManual Windows 10Fernando SalazarAún no hay calificaciones

- Virtual Box LuoQDocumento3 páginasVirtual Box LuoQFrancisco Lee ChenAún no hay calificaciones

- Entornos de La Adm de Sist Modalidad de Exámenes - Semana 2 - Revisión Del IntentoDocumento3 páginasEntornos de La Adm de Sist Modalidad de Exámenes - Semana 2 - Revisión Del IntentoSerch MartinezAún no hay calificaciones

- Metodologias Desarrollo SoftwareDocumento117 páginasMetodologias Desarrollo SoftwareLuis JosAún no hay calificaciones

- Guia 1 - CFCDocumento17 páginasGuia 1 - CFCOLMER CLAUDIO VILLENA LEONAún no hay calificaciones

- Política de Seguridad de Redes InalámbricasDocumento6 páginasPolítica de Seguridad de Redes InalámbricasReyna callesAún no hay calificaciones

- Macros VBA en Excel 2003 y 2007Documento87 páginasMacros VBA en Excel 2003 y 2007chamber100% (43)

- Diagrama DesfibriladorDocumento1 páginaDiagrama DesfibriladorEric Medina PortilloAún no hay calificaciones

- Ers Siscom BorradorDocumento16 páginasErs Siscom Borradorcesar mierAún no hay calificaciones

- Wuolah Free Apuntes SSDDDocumento47 páginasWuolah Free Apuntes SSDDDaniel MuñozAún no hay calificaciones

- Informe de Practica Pre ProfesionalesDocumento35 páginasInforme de Practica Pre ProfesionalesTania HUINCHO LOPEZAún no hay calificaciones

- TablaDocumento5 páginasTablaALVARO ZAún no hay calificaciones

- Manual de Errores de TabletsDocumento8 páginasManual de Errores de Tabletsmartin.mendoza.flores.1996Aún no hay calificaciones

- Tipo de GarantiaDocumento4 páginasTipo de GarantiaAlex Roy Huiza Flores100% (1)

- C5 5 - 4 PLC Control Continuo - PPTDocumento76 páginasC5 5 - 4 PLC Control Continuo - PPTDavid MontescoAún no hay calificaciones

- Examen MicroporcesadoresDocumento31 páginasExamen MicroporcesadoresGrizAún no hay calificaciones

- Laboratorio No3 - Circuitos DigitalesDocumento10 páginasLaboratorio No3 - Circuitos DigitalesFrank PerezAún no hay calificaciones

- DSS - Storage Training Material (Espanol)Documento60 páginasDSS - Storage Training Material (Espanol)JosePalacinAún no hay calificaciones

- Laboratorio 3 TransitorDocumento25 páginasLaboratorio 3 TransitorJoe QH100% (1)

- Programacion IIDocumento4 páginasProgramacion IIJuan Carlos ZeusAún no hay calificaciones

- Installation InstructionsDocumento13 páginasInstallation Instructionsvictor mezaAún no hay calificaciones

- Grupo #11 Cloud ComputingDocumento13 páginasGrupo #11 Cloud ComputingBrando P ChalloAún no hay calificaciones

- Manual Administrador Invesicres 63Documento215 páginasManual Administrador Invesicres 63Javier RamírezAún no hay calificaciones

- Informatica CobaemDocumento141 páginasInformatica Cobaemjagt9Aún no hay calificaciones

- Lista de Precios Al Público, Central PC Informática 22 Octubre 2011Documento4 páginasLista de Precios Al Público, Central PC Informática 22 Octubre 2011Ricardo J. LohseAún no hay calificaciones

- Cuadro Sinoptico Diseño SoftwareDocumento1 páginaCuadro Sinoptico Diseño SoftwareLeonel Alarcón Bravo50% (2)

- Revista Rockwell AutomationDocumento40 páginasRevista Rockwell Automationpepe grilloAún no hay calificaciones

- Git Cheatsheet - Charly CiminoDocumento1 páginaGit Cheatsheet - Charly CiminoIan TepperAún no hay calificaciones

- MP Programación Orientada A Objetos SCD-1020Documento20 páginasMP Programación Orientada A Objetos SCD-1020Mauricio López ReyesAún no hay calificaciones