Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Electonica PDF

Cargado por

Anthony GarciaTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Electonica PDF

Cargado por

Anthony GarciaCopyright:

Formatos disponibles

Contenido

1. JUSTIFICACIN ..................................................................................................................... 2

2. OBJETIVOS ............................................................................................................................. 2

2.1 Objetivo General ............................................................................................................ 2

2.2 Objetivos Especficos .................................................................................................. 2

3. FUNDAMENTO TERICO .................................................................................................... 2

3.1 Funcin lgica. lgebra de Boole ............................................................................. 2

3.2 Puertas lgicas .............................................................................................................. 3

3.3 Circuitos integrados digitales .................................................................................... 4

4. DISEO .................................................................................................................................... 5

4.1 Tabla de Verdad ............................................................................................................. 6

4.2 Simplificacin de Karnaugh ....................................................................................... 6

4.3 Funcin ............................................................................................................................ 6

4.4 Circuito Lgico............................................................................................................... 7

5. LISTADO DE MATERIALES ................................................................................................. 8

6. CONCLUSIONES .................................................................................................................... 8

7. BIBLIOGRAFA ....................................................................................................................... 9

2

1. JUSTIFICACIN

Los circuitos electrnicos digitales se basan en la transmisin y el procesamiento

de informacin, lo que hace necesario verificar que la informacin recibida es igual

a la emitida; no suelen producirse errores, por lo que cuando ocurren en la mayora

de los casos el error en la transmisin se produce en un nico bit.

El mtodo ms sencillo y eficaz de comprobacin de la transmisin de datos

consiste en aadir a la informacin transmitida un bit ms, con la misin de que el

nmero de 1 transmitidos en total sea par (paridad par), o impar (paridad impar).

2. OBJETIVOS

2.1 Objetivo General

Implementar un generador de paridad par e impar para detectar, y en algunos

casos corregir, errores en la transmisin.

2.2 Objetivos Especficos

Disear matemticamente el funcionamiento.

Elaborar el circuito digital utilizando multisim.

Implementar el circuito digital en el protoboard.

3. FUNDAMENTO TERICO

3.1 Funcin lgica. lgebra de Boole

El lgebra de Boole y los sistemas de numeracin binarios constituyen la base

matemtica para construir los sistemas digitales.

El lgebra de Boole es una estructura algebraica que relaciona las operaciones

lgicas O, Y, NO. A partir de estas operaciones lgicas sencillas, se pueden

obtener otras ms complejas que dan lugar a las funciones lgicas. Por otra

parte, hay que tener en cuenta que los valores que se trabajan en el lgebra de

Boole son de tipo binario.

Existen tres operaciones lgicas: suma, multiplicacin y complementacin o

inversin. Sus postulados son los siguientes:

3

Fig. 1 Propiedades del Algebra de Boole

3.2 Puertas lgicas

Compuerta. Es un bloque de circuitera que produce seales de salida lgica

(1 0) si se satisfacen las condiciones de las entradas lgicas. Los nombres,

circuitos digitales, circuitos de conmutacin, circuitos lgicos y compuertas son

usados a menudo pero s har referencia a los circuitos con compuertas.

1

Tabla de verdad. Es una representacin en forma tabular de todas las

combinaciones posibles de las variables de entrada.

Usos.- Cualquier informacin usada para calcular o controlar, puede ser

operada pasando seales binarias a travs de varias combinaciones de

circuitos lgicos con cada seal que representa una variable y transporta un bit

de informacin. Definimos como bit los 1 0 que puede tomar una variable

binaria.

Las ms importantes se muestran en la siguiente tabla:

1

http://www.aguilarmicros.mex.tl/imagesnew2/0/0/0/0/2/1/4/2/9/6/Comp_L.pdf

4

Fig. 2 Compuertas Lgicas

3.3 Circuitos integrados digitales

Los componente bsicos de los integrados son las puertas (Fig. 2), las cuales

se encuentran dentro de un chip o en circuitos digitales integrados con una

tecnologa de fabricacin que trataremos en el siguiente apartado: TTL y CMOS.

Cada chip o circuito integrado (Fig. 3) tiene una hoja de caractersticas que

facilita el fabricante.

Fig. 3 Chip de puertas

Lgicas

5

A su vez, cada tipo de puerta tiene su integrado del tipo 74xx, donde 74 (tecnologa

TTL) es la serie con las caractersticas ms importantes:

Tensin de alimentacin: 5 voltios.

Temperatura de trabajo: de 0 a 70 C.

Y xx es un nmero que nos indica de qu tipo de puerta se trata. As lo recoge la

siguiente tabla:

Fig. 4 Chips integrados y # de puertas segn el tipo de puerta lgica.

4. DISEO

Disear un generador de paridad par e impar A, B, C, D.

6

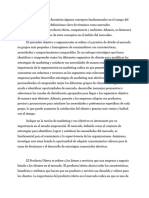

4.1 Tabla de Verdad

4.2 Simplificacin de Karnaugh

0

1

4 12

1

8

1

1 5

1

13 9

3

1

7 15

1

11

1

2 6

1

14 10

4.3 Funcin

) +

+) +

+) +(

)

(

+)(

) +(

)(

+)

(

)( ) +( )(

)

TABLA DE VERDAD

A B C D PAR IMPAR

0 0 0 0 0 1

0 0 0 1 1 0

0 0 1 0 1 0

0 0 1 1 0 1

0 1 0 0 1 0

0 1 0 1 0 1

0 1 1 0 0 1

0 1 1 1 1 0

1 0 0 0 1 0

1 0 0 1 0 1

1 0 1 0 0 1

1 0 1 1 1 0

1 1 0 0 0 1

1 1 0 1 1 0

1 1 1 0 1 0

1 1 1 1 0 1

7

4.4 Circuito Lgico

Fecha: 29-01-2014 UNIVERSIDAD

TECNOLGICA ISRAEL

Diseado por:

SALAS CHRISTIAN

Nombre del Proyecto:

CIRCUITO DIGITAL LGICO

PARA ABRIR LA PUERTA

DE UN DATA CENTER

Revisado por:

ING. JCOME

SIMBOLOGA

Fuente

Dip Switch

Resistencia

Tierra

8

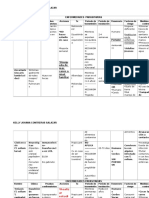

5. LISTADO DE MATERIALES

COSTOS DIRECTOS

CANTIDAD DESCRIPCIN PRECIO UNI TOTAL

1 Protoboard $ 11,00 $ 11,00

1 Compuerta 7486 $ 0,68 $ 0,68

4 Resistencia 1k $ 0,05 $ 0,20

2 Resistencia 4,7k $ 0,07 $ 0,14

1 Dip switch $ 0,70 $ 0,70

2 Led $ 0,15 $ 0,30

TOTAL $ 13,02

COSTOS INDIRECTOS

CANTIDAD DESCRIPCIN PRECIO UNI TOTAL

1 Varios $ 15,00 $ 15,00

TOTAL $ 15,00

COSTOS

DIRECTOS

COSTOS

INDIRECTOS

TOTAL

$ 13,02 $ 15,00 $ 28,02

6. CONCLUSIONES

6.1 Conclusiones

Se demostr que funcin cumplen con los generadores de paridad.

Se logr comprender el fundamento terico del generador de paridad y

la importancia de verificar que informacin se est recibiendo.

Logramos observar el el bit de paridad se utiliza para detectar posibles

errores en la transmisin del dato transmitido, mediante la comprobacin

de paridad.

9

7. BIBLIOGRAFA

(Boylestad, Introduccion a los Sistemas Digitales, 2004)

(http://recursostic.educacion.es/secundaria/edad/4esotecnologia/quincena5/4q2_c

ontenidos_4d.htm, s.f.)

(http://www.aguilarmicros.mex.tl/imagesnew2/0/0/0/0/2/1/4/2/9/6/Comp_L.pdf, s.f.)

http://educativa.catedu.es/44700165/aula/archivos/repositorio/4750/4923/html/9_d

etectoresgeneradores_de_paridad.html

También podría gustarte

- Evaluación de La Calidad de La TecnologíaDocumento16 páginasEvaluación de La Calidad de La TecnologíaMónica Marcela Cano LópezAún no hay calificaciones

- 04 La Observación - EntrevistaDocumento40 páginas04 La Observación - EntrevistaNora Loarte PoloAún no hay calificaciones

- Examen Unidad 3 MicroeconomiaDocumento7 páginasExamen Unidad 3 MicroeconomiawillingtonAún no hay calificaciones

- MARTIN ROSE - Working With DiscurseDocumento24 páginasMARTIN ROSE - Working With DiscurseHado NavarroAún no hay calificaciones

- Foro de Discusion Modulo 1Documento5 páginasForo de Discusion Modulo 1cm.acevedomAún no hay calificaciones

- Analisis de Trabajo SeguroDocumento6 páginasAnalisis de Trabajo SeguroyhytyrgfgfgAún no hay calificaciones

- Plan Maestro Ibagué 1Documento138 páginasPlan Maestro Ibagué 1Karolina GalindoAún no hay calificaciones

- RemediosDocumento31 páginasRemediosemmaAún no hay calificaciones

- GUIA - INDUCCION A LOS PROYECTOS DEL PnfaDocumento51 páginasGUIA - INDUCCION A LOS PROYECTOS DEL PnfaROSIBEL100% (1)

- Modelo Acta ConstitutivaDocumento9 páginasModelo Acta ConstitutivaBerenice BolañosAún no hay calificaciones

- Prueba Síntesis SemestralDocumento4 páginasPrueba Síntesis SemestralNoni05Aún no hay calificaciones

- 2do Parcial Epidemio - KELLY NOTASDocumento35 páginas2do Parcial Epidemio - KELLY NOTASBetzi HannlyAún no hay calificaciones

- Azul Rojo Verde y Amarillo Fotos Collage Moderno Empresa Reunión PresentaciónDocumento12 páginasAzul Rojo Verde y Amarillo Fotos Collage Moderno Empresa Reunión PresentaciónChantal Escalante BautistaAún no hay calificaciones

- Ejercicios IndependienteDocumento29 páginasEjercicios IndependienteRonny Chilon Troncos100% (1)

- Arquitectura de Computadores Promera EntregaDocumento5 páginasArquitectura de Computadores Promera EntregaJOSE SAMUEL VARGAS DAZAAún no hay calificaciones

- Esquema Figuras LiterariasDocumento9 páginasEsquema Figuras Literariasesmith81Aún no hay calificaciones

- Mandos MediosDocumento7 páginasMandos MediosGY HERNANDEZAún no hay calificaciones

- Proyecto Inversión Rodriguez Marquez Gomez WilliamsDocumento39 páginasProyecto Inversión Rodriguez Marquez Gomez WilliamsGeorgina GomezAún no hay calificaciones

- La EspiritualidadDocumento13 páginasLa EspiritualidadMateo BaquerizoAún no hay calificaciones

- Educacion SexualDocumento2 páginasEducacion SexualAngela CerquinAún no hay calificaciones

- Comentario de Texto Sobre CampanellaDocumento5 páginasComentario de Texto Sobre CampanellaMayra GallardoAún no hay calificaciones

- Propuesta de La Implementacion de Un Sistema de SySODocumento4 páginasPropuesta de La Implementacion de Un Sistema de SySOFabiolaButronAún no hay calificaciones

- Cotizacion Examenes Medicos Agosto AydapackDocumento4 páginasCotizacion Examenes Medicos Agosto AydapackRUBY HAún no hay calificaciones

- PLAN DE AULA Mod. 2.3Documento9 páginasPLAN DE AULA Mod. 2.3MARTHA AFRICA CABRERA ADAMEAún no hay calificaciones

- Tipos de ComprasDocumento8 páginasTipos de ComprasKatty ChilaAún no hay calificaciones

- Trabajo 01 - Comportamiento HumanoDocumento26 páginasTrabajo 01 - Comportamiento HumanojeanpierAún no hay calificaciones

- Sistematizacion 1111111111111111111111111 CompletoDocumento65 páginasSistematizacion 1111111111111111111111111 Completoanto130Aún no hay calificaciones

- CDU Abreviada 2016 PDFDocumento966 páginasCDU Abreviada 2016 PDFGabriela Salinas100% (1)

- Musculo CardiacoDocumento2 páginasMusculo CardiacoFrancesca PupoAún no hay calificaciones