Documentos de Académico

Documentos de Profesional

Documentos de Cultura

TecnologiaMOS 01

Cargado por

cojin1234Título original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

TecnologiaMOS 01

Cargado por

cojin1234Copyright:

Formatos disponibles

1

1

Tecnologa de Computadores

EL DISPOSITIVO MOS.

LOGICA INTEGRADA MOS (Parte 1)

2

Dispositivos MOSFET

(MOS :Metal-Oxido Semiconductor)

(FET: Field Effect Transistor)

Transistor de efecto de campo

2

3

Transistor de efecto de campo

Principio bsico de operacin:

Un campo elctrico externo controla el flujo de

corriente a travs de un canal de conduccin

establecido entre otros dos terminales.

Mecanismo de conduccin es atribuible a un

solo tipo de portador de carga (electrones o

huecos). (Conduccin unipolar)

Transistores Unipolares

5

Transistor de efecto de campo

MOSFET Metal Oxide Semiconductor Field

Effect Transistor

Enhanced Mode MOSFET Acumulacin

Modo de, enriquecimiento

Campo elctrico crea un canal de conduccin

Depletion Mode MOSFET Deplexion

Modo de agotamiento,

El canal de conduccin se fabrica con material semiconductor

3

6

Transistor de efecto de campo

Se utiliza mayormente en circuitos

integrados.

Puede emplearse tanto en circuitos

analgicos como digitales.

Mayor uso en circuitos digitales.

Un transistor MOSFET ocupa mucho menos

rea que un BJT.

Permite mayor cantidad de transistores en el mismo

espacio.

7

Transistor de efecto de campo

Atractivo:

Menos pasos en el proceso de fabricacin que

para sus contrapartes bipolares.

Es posible construir circuitos lgicos con

dispositivos MOSFET que no utilicen

resistencias.

Menor consumo de energa elctrica.

Menor disipacin de calor.

4

8

MOSFET

de Acumulacin o Enriquecimiento

(Enhanced)

9

Enhanced nMOS

Construccin tpica de un MOSFET de acumulacin

(Enhanced MOSFET)

p

n

+

n

+

p

n

+

n

+

p

n

+

n

+

sustrato

Fuente

(source)

Sumidero

(drain)

Compuerta

(gate)

SiO

2

Aluminio

Terminal

Sustrato

(body)

Canal

(Channel)

5

10

Elementos importantes

Desde el punto de vista del

componente electrnico

existen cuatro zonas o partes

del dispositivo:

Fuente (Source)

Compuerta (Gate)

Sumidero (Drain)

Canal (Channel)

11

Vista lateral

El terminal SS (Sustrato)

tiene el propsito de

aplicar un voltaje lo

suficientemente negativo

para evitar que la unin

pn entre en conduccin.

Normalmente se conecta

internamente al S

(Source).

p

n

+

n

+

Zona de

canal

inducido

Largo del

canal

L

S

G

SS

D

6

12

Largo del canal

El largo del canal es un parmetro

importante en la tecnologa de circuitos

integrados.

Mientras ms corto se pueda

fabricar, mayor es la densidad

de componentes.

Tecnologa de 0.5 micrones

significa que el largo de canal

es 0.5 um.

La capa de SiO

2

que forma la

compuerta es bien delgada, asegura que

el campo elctrico sea lo ms intenso

posible.

p

n

+

n

+

L

S

G

D

SS

Zona de

canal

inducido

Largo del

canal

SiO

2

13

NMOS y PMOS

p

n

+

n

+

S

G

D

B

n

p

+

p

+

S

G

D

B

canal n

canal p

Portadores de

carga son

electrones libres

Portadores de

carga son huecos

NMOS

PMOS

7

14

Induccin del canal

15

Substrato (Sustrate)

G

S D

Material tipo p

Induccin de canal en MOSFET

Sin voltaje aplicado en la compuerta (G).

n

+

n

+

Zonas de

agotamiento de

carga

8

16

Material tipo p

Induccin de canal en MOSFET

Efecto de aplicar un voltaje en la compuerta (G).

Substrato (Sustrate)

G

S D

V

GS

n

+

- - - - - - - - - - - - - -

n

+

Campo elctrico repele a los

huecos y atrae a los

electrones libres (minoras)

en el material p

Canal de conduccin

formado con los electrones

libres atrados

V

th

: voltaje de umbral potencial

mnimo necesario para que pueda

existir un canal de conduccin

17

Material tipo p

Induccin de canal en nMOSFET

Efecto de aumentar el voltaje en la compuerta (G).

Substrato (Sustrate)

G

S D

V

GS

n

+

n

+

Canal de conduccin se

hace ms profundo

9

18

Material tipo p

Aplicacin de un voltaje al D

Substrato (Sustrate)

G

S D

V

GS

n

+

n

+

D

V

DS

I

D

es proporcional a |V

GS

- V

th

| y a V

DS

Caso de V

DS

relativamente pequeo.

Canal de conduccin

permite paso de corriente

de electrones.

19

Corriente i

D

En trminos sencillos, para voltajes pequeos la

relacin entre v

DS

e i

D

sigue la Ley de Ohm.

v

GS

determina cul es el rea seccional del canal.

WD

L

r

r i v

D DS

=

=

L

Canal

W

D

10

20

i

D

para v

DS

pequeo

V

t

es el voltaje de

umbral

(threshold

voltage).

|v

GS

V

t

| es el

voltaje efectivo

que afecta al

canal.

i

D

v

DS

v

GS

Curva de v

GS

= V

t

21

Aplicacin de un voltaje entre D y S

Caso de V

DS

mayor

Material tipo p

Substrato (Sustrate)

G

S D

V

GS

D

V

DS

n

+

n

+

Canal de conduccin se

hace ms angosto

La profundidad del canal depende de la diferencia en

potencial entre v

DS

y v

GS

la cual es mayor cerca de S que

cerca de D.

11

22

Material tipo p

Aplicacin de un voltaje entre D y S

Substrato (Sustrate)

G

S D

V

GS

D

V

DS

Caso de V

DS

an mayor

n

+

n

+

Canal de conduccin se

hace bien angosto

La conductividad del canal ahora solo depende de la

cantidad de electrones inyectados al canal, no de v

DS

.

23

Saturacin del canal

Al cerrarse el canal la

corriente deja de depender

de la magnitud del voltaje

v

DS.

De ah es que viene el

trmino de que la

corriente i

D

se satura.

Este modo de operacin se

conoce como regin de

saturacin.

0011 0010 1010 1101 0001 0100 1011

3-mar -03

(c) 2003 Jorge A. Cruz Emeric

31

0011 0010 1010 1101 0001 0100 1011

Material tipo p

Aplicacin de un voltaje al D

Substrato (Sustrate)

G

S D

V

GS

D

V

DS

Caso de V

DS

an mayor

Caso de V

DS

an mayor

n

+

n

+

Canal de conduccin se

hace bien angosto

Canal de conduccin se

hace bien angosto

La conductividad del canal ahorasolo depende ahora de la

cantidad de electrones inyectados al canal, no de v

DS

.

La conductividad del canal ahorasolo depende ahora de la

cantidad de electrones inyectados al canal, no de v

DS

.

No debe confundirse esta

regin de saturacin en

MOS con la regin de

saturacin de los BJT.

12

24

Material tipo p

Acortamiento del canal

Substrato (Sustrate)

G

S D

V

GS

D

V

DS

Caso de V

DS

an mayor

n

+

n

+

Canal de conduccin

aparenta ser ms corto

Aceleracin de electrones por v

DS

ms alto hace que el

largo aparente del canal dependa de v

DS

.

25

Curvas caractersticas

de nMOS - Acumulacin

13

26

Curva caracterstica de entrada

nMOS Acumulacin

v

GS

i

D

V

t

| |

2

t GS D

V v K i =

No existe canal = NO puede

conducir

V

th

=V

t

= voltaje de

umbral (threshold)

Existe canal = puede

conducir

L

W

k K

n

'

5 . 0 =

k

n

=parametro de

transconductancia

Factor de Ganancia

(Amperios/Voltios

2

)

27

Curva caracterstica de salida

nMOS modo Acumulacin

Regin de saturacin

v

DS

i

D

v

GS

Regin

hmica o

lineal

Regin de corte

v

GS

= V

T

|v

DS

| = |v

GS

-V

T

|

|v

DS

|<| v

GS

-V

T

|

|v

DS

| > |v

GS

-V

T

|

14

28

Ecuacin de la corriente i

D

(

=

2

) (

2

DS

DS t GS D

v

v V v K i

Regin Lineal

| |

2

2

t GS D

V v

K

i =

Regin de saturacin

K ajusta las propiedades del dispositivo

(acta como factor de escala).

0011 0010 1010 1101 0001 0100 1011

3-mar-03

(c) 2003 Jorge A. Cruz Emeric

35

0011 0010 1010 1101 0001 0100 1011

v

DS

>v

GS

- V

T

Regin de saturacin

Curva caracterstica de salida

v

DS

i

D

v

GS

= V

T

v

GS

= V

T

v

GS

Regin de

triodo

v

DS

= v

GS

-V

T

v

DS

= v

GS

-V

T

) (

DS D

v f i =

29

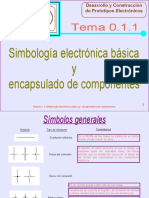

Smbolos esquemticos

Modo de Acumulacin NMOS

Modo de Acumulacin NMOS

cuando B se conecta

internamente a S.

G

D

S

B

D

S

G

D

S

B

Modo de Acumulacin PMOS

G

D

S

Modo de Acumulacin PMOS

cuando B se conecta

internamente a S.

G

D

S

G

G

D

S

15

48

Curvas pMOS

Acumulacin Deflexin

49

Curvas nMOS

16

50

Curvas pMOS

( Vt=-5v)

( Vt=-5v)

51

Para pMOS son las mismas curvas que nMOS

con los siguientes cambios:

V

GS

V

SG

(-V

GS

)

I

D

(D-->S) I

D

(S-->D)

V

DS

V

SD

(-V

SD

)

PMOS es el opuesto a NMOS (Voltajes y Corrientes)

Resumen Curvas caractersticas

17

54

T GS DS

T GS

V V V

V V

<

>

| |

2

2

0

T GS D

G

V V

K

I

I

=

=

0

0

=

=

D

G

I

I

T GS

V V s

(

=

=

2

) (

0

2

DS

DS T GS D

G

V

v V V K I

I

T GS DS

T GS

V V V

V V

>

>

Corte

Lineal

Saturacin

gin Re

Corrientes Voltajes

Modos de funcionamiento en el nMOS

55

T GS DS

T GS

V V V

V V

<

<

| |

2

2

0

T GS D

G

V V

K

I

I

=

=

0

0

=

=

D

G

I

I

T GS

V V >

(

=

=

2

) (

0

2

DS

DS T GS D

G

V

V V V K I

I

Corte

Lineal

Saturacin

gin Re

Corrientes Voltajes

Modos de funcionamiento en el pMOS

T GS DS

T GS

V V V

V V

>

<

18

56

D +

S -

V

DS

> 0 G +

V

GS

< V

T

I

D

=0

I

G

=0

D +

S -

V

DS

<V

GS

-V

T

G

I

D

I

G

=0

+

-

V

GS

> V

T

D +

S -

V

DS

>V

GS

-V

T

G

I

D

I

G

=0

+

-

V

GS

> V

T

Corte

Lineal Saturacin

| |

2

2

0

T GS D

G

V V

K

I

I

=

=

0

0

=

=

D

G

I

I

(

=

=

2

) (

0

2

DS

DS T GS D

G

V

v V V K I

I

Ejemplos Modos de funcionamiento en

el nMOS

57

Modelos Equivalentes

19

58

Comparacin de los circuitos de polarizacin

para trabajar en zona resistiva o en zona de fuente

de corriente con MOSFET de ambos tipos de canal

+

-

V

DS

I

D

+

-

V

GS

R

V

2

G

D

S

V

1

Canal N

+

-

V

DS

-I

D

+

-

V

GS

R

V

2

G

D

S

V

1

Canal P

Hay que invertir los sentidos reales de tensiones y

corrientes para operar en los mismas zonas de trabajo.

63

Ejemplo II

20

64

Especificaciones

Disee el circuito a la

izquierda para obtener

I

D

=0.4 mA

Las propiedades del

transistor son:

V

t

=1 V

K=0.8 mA/V

2

10V

R

El diseo en este caso

significa encontrar el valor

apropiado para R que

establezca el punto de

operacin especificado.

65

En qu regin est operando?

Dado que V

DS

> V

GS

- V

t

, este

transistor tiene que operar en la regin

de saturacin.

La ecuacin que describe su

comportamiento es:

10V

R

Observe que por la

manera en que ha sido

conectado V

DS

= V

GS

.

G

D

S

| |

2

2

T GS D

V V

K

I =

I

D

=0.4 mA

V

t

=1 V

K=0.8 mA/V

2

21

66

Anlisis

Por LVK

10V

R

G

D

S

I

D

R I V

D DS

+ = 10

La ecuacin del transistor

Como V

DS

= V

GS

, obtenemos:

| |

2

2

T GS D

V V

K

I =

| |

2

1 1 =

GS

V

I

D

=0.4 mA

V

t

=1 V

K=0.8 mA/V

2

67

Anlisis

10V

R

I

D

| |

2

1 1 =

GS

V

Buscando raz cuadrada a ambos lados queda

1 1 =

GS

V

Note que la segunda solucin no es viable.

Por qu lo sabe?

Para que el transistor pueda estar en conduccin hace falta

que V

GS

> V

t

Note que V

GS

= 0 no cumple con esto.

V V

GS

2 =

0 =

GS

V

V V

GS

2 =

22

68

Anlisis

10V

R

I

D

R V

DS

4 . 0 10 + =

La solucin es

R I V

D DS

+ = 10

Dato: I

D

= 0.4 mA

Retomando a:

V V

GS

2 =

K R 20 =

V

DS

=V

GS

= 2 V

69

Comentarios sobre ejemplo

Cuando resuelve por V

GS

o V

DS

,

Est resolviendo una ecuacin cuadrtica.

Produce dos posibles soluciones

Una de ellas es extraa.

La otra no es extraa pero no necesariamente es

correcta.

23

70

Comentarios sobre ejemplo

i

D

v

GS

V

t

I

D

V

GS1

V

GS2

| |

2

t GS D

V v K I =

Parbola

Transistor

Solucin #1

Solucin #2

71

Ejemplo III

24

72

Especificaciones

Obtenga el valor de R

S

para establecer V

D

= 4 V

Datos para el transistor

V

t

=2 V

K =1mA/V

2

5V

10 K 1 M

R

S

4V

Note que no se especifica regin

de operacin as que deber

determinarla.

73

Anlisis

Suponiendo que est en la regin de

saturacin

5V

10 K 1 M

R

S

Note que I

G

= 0 siempre as que:

| |

2

2

t GS D

V V

K

I =

5V

5V

El hecho que V

G

= 5 V no es sinnimo

que V

GS

tambin lo sea.

V

G V

GS

V V

G

5 =

25

74

Anlisis

5V

10 K 1 M

R

S

5V

5V

La resistencia de 1 M no tiene

impacto en la determinacin de V

GS

.

Al no haber i

G

, no existe cada de

voltaje a travs de ella.

V

G V

GS

75

Anlisis

5V

10 K 1 M

R

S

4V

Necesitamos una ecuacin adicional o

calcular I

D

de manera independiente.

Observe que

| |

2

2

t GS D

V V

K

I =

5V

I

D

mA

K

V

I

D

1 . 0

10

) 4 5 (

=

=

| |

2

2 5 . 0 1 . 0 =

GS

V mA

V

t

=2 V

K =1mA/V

2

V V

V V

GS

GS

663 . 1

447 . 2

=

=

V V

G

5 =

Al resolver queda

26

76

Anlisis

5V

100 K 1 M

R

S

4V

Note que la segunda solucin es menor que

V

t

por lo que no es compatible con el

problema fsico.

5V

I

D

V

t

=2 V

[k

n

] =1mA/V

2

V V

GS

447 . 2 =

Ahora calcule V

S

GS S

V V V + = 5

447 . 2 5 + =

S

V

V V

S

553 . 2 =

V V

V V

GS

GS

663 . 1

447 . 2

=

=

77

Anlisis

5V

10 K 1 M

R

S

4V

Coteje si esta solucin es compatible con

la regin de saturacin.

Para ello necesita determinar cunto es

V

DS

.

I

D

V V

GS

447 . 2 =

Lo cual est bien.

S D DS

V V V =

V V

S

553 . 2 =

V V

DS

447 . 1 553 . 2 4 = =

V

DS

>V

GS

V

t 2 447 . 2 447 . 1 >

27

78

Anlisis

5V

10 K 1 M

R

S

4V

Ahora puede calcular R

s

.

I

D

V V

GS

447 . 2 =

K

mA

V

R

S

5 . 25

1 . 0

553 . 2

= =

V V

S

553 . 2 =

D

S

S

S

S

I

V

I

V

R = =

79

Circuitos de polarizacin

28

80

Circuito de polarizacin

Las configuraciones utilizadas para

polarizar transistores bipolares sirven

tambin para MOSFET.

Su diseo es ms simple ya que I

G

= 0.

Sin embargo, debe velar por la relacin

entre V

DS

y V

GS

- V

t

81

Configuraciones discretas

Clsico

Dos fuentes

Retroalimentado

R

D

R

S

V

DD

R

1

R

2

R

D

R

S

V

DD

R

G

-V

SS

R

D

V

DD

R

G

29

82

Ejemplo circuito clsico

1 2

2

R R

R

V V

DD G

+

=

DS S D D DD

V R R I V + + = ) (

S D G GS

R I V V =

Por divisor de voltaje a la izquierda.

V

G

Por LVK a la derecha:

R

D

R

S

V

DD

R

1

R

2

Por LVK en circuito de la compuerta:

83

Circuito clsico modificado

Observe que:

0 =

G

V

DS S D D SS DD

V R R I V V + + = + ) (

SS D D GS

V R I V + =

Por LVK:

R

D

R

S

V

DD

R

G

-V

SS

Note que ninguna de

las ecuaciones incluye

a R

G

.

30

84

Circuito con retroalimentacin

Del circuito es evidente que:

DS GS

V V =

t GS DS

V V V >

DS D D DD

V R I V + =

Por LVK:

En este caso siempre se cumple que :

Al igual que el caso previo, ninguna de las

ecuaciones contiene a R

G

.

R

D

V

DD

R

G

85

Recta de Carga y Punto de Operacin

31

86

Punto de operacin

v

DS

(V) 5 10 15 20 25

2

4

6

8

10

i

D

(mA)

V

GS

=1.2V

V

GS

=1.4V

V

GS

=1.6V

V

GS

=1.8V

V

GS

=2.0V

Punto de

operacin

Lnea de carga:

I

D

=F(V

DS

)

V

DS

I

D

Suponiendo que

conoce V

GS

del

punto de operacin.

Vdd

R

92

Ejemplo pMOS

Determine el punto de trabajo de Q1 y Q2

K1=K2=0.2 mA/V

2

, Vth=-5 V

También podría gustarte

- Club Saber Electrónica Nro. 78. FuentesDocumento84 páginasClub Saber Electrónica Nro. 78. FuentesJose Emmanuel De La CruzAún no hay calificaciones

- Espejo de Corriente y Puente HDocumento10 páginasEspejo de Corriente y Puente Hfernanda.navasAún no hay calificaciones

- Practica 1 EspejoDocumento4 páginasPractica 1 Espejoyuvan ramosAún no hay calificaciones

- Preg Examen Radioaficionados Apendice C Materia Tecnica NOVICIODocumento48 páginasPreg Examen Radioaficionados Apendice C Materia Tecnica NOVICIOJuanAún no hay calificaciones

- UNIDAD 2 SCR UjtdiactriacDocumento120 páginasUNIDAD 2 SCR UjtdiactriacKevin AlcantarAún no hay calificaciones

- Manual Software Fluid SIMDocumento5 páginasManual Software Fluid SIMJoseCorreaAún no hay calificaciones

- Nueva Guia de Estudios para Exámen de RadioaficionadoDocumento40 páginasNueva Guia de Estudios para Exámen de RadioaficionadoFabián A. Juárez MartínezAún no hay calificaciones

- Reparador de Celulares y TabletsDocumento80 páginasReparador de Celulares y TabletsNaolsSloan0% (1)

- Cuestionario #4 Fundamento de ElectronicaDocumento7 páginasCuestionario #4 Fundamento de ElectronicaMarkrowAún no hay calificaciones

- Consulta JfetDocumento6 páginasConsulta JfetDiose PaolaAún no hay calificaciones

- Syllabus Electrónica de Potencia UDDocumento12 páginasSyllabus Electrónica de Potencia UDDavid Corredor RamirezAún no hay calificaciones

- Curso Microelectronica 1Documento15 páginasCurso Microelectronica 1yohan davila0% (1)

- Electronica AnalogicaDocumento31 páginasElectronica AnalogicaJonathan Lopez67% (3)

- Método de Ajuste y Reparación para Radios Con CI LA1828 Electrónica CompletaDocumento18 páginasMétodo de Ajuste y Reparación para Radios Con CI LA1828 Electrónica CompletaTrafu Lar100% (1)

- IEEE Carro Seguidor de Linea InformeDocumento4 páginasIEEE Carro Seguidor de Linea InformebyandresmayorgaAún no hay calificaciones

- Clasificacion de TransistoresDocumento2 páginasClasificacion de TransistoresMax Zarate100% (2)

- Aplicaciones Del Fet PDFDocumento7 páginasAplicaciones Del Fet PDFFlorin MitranAún no hay calificaciones

- Definicion de CONTACTORDocumento3 páginasDefinicion de CONTACTORZulma Neysa VasquezAún no hay calificaciones

- Laboratorio 1 El TransistorDocumento5 páginasLaboratorio 1 El TransistorANDRES VELEZAún no hay calificaciones

- Determinar IDSS VGSoffDocumento9 páginasDeterminar IDSS VGSoffMiguel VelizAún no hay calificaciones

- Técnicas de ReparaciónDocumento24 páginasTécnicas de ReparaciónElvisnosalgas regresayaAún no hay calificaciones

- Simbología Electrónica Básica y Encapsulado de ComponentesDocumento47 páginasSimbología Electrónica Básica y Encapsulado de ComponentesFRAILESAún no hay calificaciones

- Proyecto Final PDFDocumento19 páginasProyecto Final PDFHarold F. LaraAún no hay calificaciones

- Conversor Analogico Digital #149 PDFDocumento4 páginasConversor Analogico Digital #149 PDFdiegoAún no hay calificaciones

- 3 Circuito de Protección de Sobre y Bajo Voltaje para Motor de Inducción - Tutorial de Electrónica BásicaDocumento1 página3 Circuito de Protección de Sobre y Bajo Voltaje para Motor de Inducción - Tutorial de Electrónica BásicaJohnAún no hay calificaciones

- PDF Informe Puente H DDDocumento6 páginasPDF Informe Puente H DDESTEBAN MIGUEL ALVAREZ LUNAAún no hay calificaciones

- Lab - 14 Circuitos de Disparo DIAC-UJTDocumento8 páginasLab - 14 Circuitos de Disparo DIAC-UJTiChelsea0% (1)

- Lab 12 Transistor MOSFET PDFDocumento59 páginasLab 12 Transistor MOSFET PDFEnder Thiago Montoya MendozaAún no hay calificaciones

- Simulaciones Con Transistores BJT BC EC CCDocumento21 páginasSimulaciones Con Transistores BJT BC EC CCMadeline ReynosoAún no hay calificaciones

- Salidas de Mayor Potencia Con Arduino y Transistor BJTDocumento9 páginasSalidas de Mayor Potencia Con Arduino y Transistor BJTAlexis BohorquezAún no hay calificaciones