Documentos de Académico

Documentos de Profesional

Documentos de Cultura

5oejercicio DCSE2010-11

Cargado por

Jose MartinezTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

5oejercicio DCSE2010-11

Cargado por

Jose MartinezCopyright:

Formatos disponibles

DISEO DE CIRCUITOS Y

SISTEMAS ELECTRNICOS

Curso 2010/11 - Grupo 43

18 Enero 2011

5

ejercicio en clase (evaluacin continua)

PROBLEMA 1 [10 puntos]

Conteste a las siguientes preguntas de manera precisa y concisa:

(a) Para qu sirve el lenguaje VHDL?

VHDL (Very High Speed Integrated Circuit Hardware Description Language) es un lenguaje

estndar de descripcin hardware. Sus aplicaciones principales son: documentacin formal,

simulacin y sntesis.

(b) Cul es la definicin de una entidad y una arquitectura en VHDL? Describa el papel de cada una.

Una entidad es el bloque bsico de diseo que modela una parte de un circuito real. Su declaracin

describe la interfaz externa del circuito modelado, incluyendo el nombre del circuito, los nombres y

las caractersticas de sus entradas y salidas.

Una arquitectura especifica las operaciones internas y la organizacin del circuito. En VHDL se

pueden desarrollar mltiples arquitecturas para la misma entidad y luego elegir la ms apropiada en

distintos casos, en simulacin sntesis.

(c) Qu tcnicas se usan en VHDL para abordar diseos medianamente complejos? Cules son las

herramientas VHDL que soportan tales tcnicas?

Las dos tcnicas usadas en el curso para abordar diseos medianamente complejos se basan en la

descripcin estructural jerrquica y la repeticin de sub-componentes. El VHDL soporta el diseo

jerrquico a travs de la sentencia de declaracin ("component") y la de instanciacin de

componentes ("instancia : nombre_componente port map"). La repeticin regular de componentes

est soportada por las sentencias for...generate.

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 2 de 10

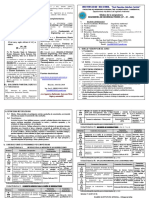

PROBLEMA 2 [90 puntos]

La unidad de ejecucin de enteros (integer execution unit, IEU) de un microprocesador de alta gama, como el

Itanium 2, est compuesta por seis unidades aritmtico-lgicas (arithmetic logic units, ALU), como se puede

ver en la figura P2.1.

Figura P2.1: La unidad de ejecucin de enteros del microprocesador Itanium 2

El camino para una de las ALU empieza por unos registros que contienen las seales de entrada a un sumador

(adder), como en la figura P2.2. El primer multiplexor (result MUX) selecciona entre el resultado de la suma

anterior, la salida de la unidad lgica y la salida de un desplazador. A continuacin, una serie de

multiplexores de puenteo (bypass MUX) selecciona las entradas al sumador para el siguiente ciclo. El early

bypass MUX selecciona entre resultados de las ALU de ciclos previos y no se encuentra en el camino crtico.

El multiplexor intermedio 8:1 de puenteo (middle bypass MUX) selecciona un resultado de una de las seis

ALUs, la salida del early bypass MUX o el fichero de registros (regfile). El multiplexor tardo 4:1 de puenteo

(late bypass MUX) selecciona uno de los dos resultados que se entregan de la memoria cach, la salida del

middle bypass MUX o un operando intermedio imm especificado por la siguiente instruccin. La salida del

late bypass MUX de la ALU se conecta a su propia entrada creando un bucle de un nico ciclo que define el

camino crtico. Como las seis ALU y los multiplexores de puenteo ocupan mucha rea en el chip, el camino

crtico incluye unas conexiones de 2mm entre los result y middle MUX y entre los middle y late MUX.

Figura P2.2: Diagrama de bloques de una ALU del microprocesador Itanium 2

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 3 de 10

La tabla de retardos de los componentes es la siguiente:

adder result MUX early MUX middle MUX late MUX pistas 2mm registros

t

max

640 ps 60 ps 110 ps 80 ps 70 ps 100 ps 90 ps

t

min

40 ps 35 ps 95 ps 55 ps 45 ps 65 ps 75 ps

Adems, los tiempos de setup y hold de los registros son respectivamente 62 ps y 10 ps. Conteste a las

siguientes preguntas:

(a) Calcule la frecuencia mxima de funcionamiento de la unidad aritmtico-lgica. [2 pts]

Retardo del camino crtico de la lgica (sumamos los retardos mximos de la tabla de retardos):

2

2 1000

logic adder resultMUX middleMUX lateMUX pistas mm

t t t t t t ps = + + + + = . s

Perodo mnimo de reloj: 90 1000 62 1152

registro logic setup min

T t t t ps ps ps ps = + + = + + = .

Por tanto:

1

868

max

min

f MHz

T

= = .

(b) La entrada que llega primero al late MUX es el valor de imm desde algn registro. Experimentara este

camino (registro - late MUX) violacin de los tiempos de hold? [3 pts]

10

hold

t ps = y

, ,

75 45 120

registro min lateMUX min

t t ps ps ps + = + = . Entonces, la condicin del tiempo de hold (el

tiempo de mantenimiento del registro de destino debe ser inferior al retardo mnimo de propagacin a

travs de la lgica, libro, apartado 10.3) se cumple y no existe violacin de hold.

(c) Una vez realizada la distribucin fsica del reloj en la IEU, se determina que hay skew ||=50 ps de un

ciclo a otro entre los biestables en las varias ALUs. Determine la frecuencia mxima de reloj a la que

podra funcionar el procesador en el caso peor del signo del skew. [3 pts]

El caso peor ocurre cuando el skew es negativo (el sesgo negativo reduce el tiempo disponible para el

procesamiento, de modo que es preciso incrementar el perodo de reloj en una cantidad igual a ||).

Calculamos otra vez el perodo mnimo sumando los retardos mximos de las etapas combinacionales

implicadas:

90 1000 62 ( 50 ) 1202 '

registro logic setup min

T t t t ps ps ps ps ps = + + = + + = .

Por tanto:

1

832

'

'

max

min

f MHz

T

= = .

(d) Determine la cota de skew de reloj permisible en la arquitectura que hemos presentado, teniendo en

cuenta lo descrito en el apartado (b). [2

pts]

Un skew negativo no afecta la condicin de hold. Slo un skew positivo grande puede violar esta condicin.

Este escenario puede realizarse como en el apartado (b), cuando la seal imm llega ms temprano:

, , , ,

75 45 10 110

hold registro min lateMUX min registro min lateMUX min hold

t t t t t t ps ps ps ps + + < < = + =

Para este problema: libro Rabaey et al., apartado 10.3.1

1050 ps

1202 ps

832 MHz

1252 ps

799 MHz

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 4 de 10

(e) Para completar el diseo del datapath de la figura P2.2, hace falta disear el sumador. Las entradas Src1

y Src2 al sumador son nmeros positivos de 16 bits.

Se conocen los siguientes datos:

- t

carry

: retardo de propagacin de cada bit del acarreo desde el acarreo de entrada al acarreo de salida

de un sumador binario completo. t

carry

= 40 ps

- t

sum

: retardo de la generacin de la suma desde los dos bits de entrada y el acarreo de entrada en un

sumador binario completo. t

sum

= 40 ps

- t

mux2-1

:

retardo de un multiplexor 2-1 de un bit. t

mux2-1

= 40 ps

- t

gate

: retardo de cualquier puerta lgica de hasta 5 entradas. t

gate

= 20 ps

e.1) Verifique que los retardos del sumador indicados en la tabla de retardos de los componentes de la

ALU corresponden a una implementacin del circuito como sumador de propagacin de acarreo

(RCA, ripple-carry adder). [5

pts]

t

RCA

= 15 t

carry

+ t

sum

= 15 40 + 40 ps = 640 ps.

Todos los dems tipos de sumadores que hemos estudiado son ms rpidos que este.

e.2) Disee la topologa del sumador carry select (CSA, sumador con seleccin del acarreo) para esta

aplicacin, suponiendo que se utilizan bloques de 4 bits. Identifique el camino crtico de

temporizacin y calcule el retardo mximo de propagacin de este tipo de sumador. [10 pts]

CSA de 16 bits: libro de Rabaey et al., fig. 11.17.

El tiempo necesario para crear las seales de generacin y propagacin (t

setup

) es de 20 ps, dado

que para realizar estas operaciones (implementacin de las expresiones 11.2 del libro)

necesitamos un circuito con un nivel de puertas lgicas.

Retardo del propagacin para el camino crtico:

t

CsA

= t

setup

+ 4t

carry

+ 4t

mux

+ t

sum

= 20 + 440 + 440 + 40 ps = 380 ps

Observamos que este sumador mejora las prestaciones de un RCA de 16 bits, aunque un

sumador CSA ocupa ms rea que un RCA.

e.3) Usando la estrategia del square root CSA (CSA no lineal), y recordando en este caso que t

mux2-1

=

t

carry

, disee el sumador segn el modelo de la arquitectura carry bypass (CBA) optimizando el

tamao de cada una de las etapas de este circuito, y proponga por tanto una variante de la

arquitectura CBA compuesta por bloques de tamao variable para la suma de dos nmeros de 16

bits.

Nota: Aunque hay varias opciones para este diseo alternativo, se sugiere empezar con el primer

bloque de tamao de solo 1 bit. Tengan en cuenta tambin que es necesario optimizar tanto el

tamao de los primeros bloques como de los ltimos en el camino crtico de temporizacin de ese

tipo de circuito sumador. [15 pts]

En un sumador CBA con todos los bloques de igual tamao, aunque todas las etapas del circuito

producen un acarreo de salida C

out

al mismo tiempo, a continuacin tienen que esperar a que el

acarreo de la primera etapa pase por todos los multiplexores, sin hacer nada ms. Como en el caso

del CSA no lineal con dependencia a la raz cuadrada del nmero de bits, podemos por tanto

reducir el tamao de la primera etapa e incrementar progresivamente el tamao de las etapas

siguientes. Del anlisis del camino crtico del CBA, sin embargo (ecuacin 11.9 del libro de Rabaey

et al), el camino crtico incluye tambin la ltima etapa de sumadores. Como consecuencia,

tenemos que empezar a reducir el tamao de los bloques cuando nos aproximamos a la parte final

del circuito.

Si t

mux2-1

= k t

carry

entonces el segundo bloque debera tener k+1 sumadores, el tercero 2k+1, etc.

Aqu el problema se simplifica por tener k=1. Por esto, en este caso podemos simplemente escoger

tambin una solucin con etapas de 1, 2, 3, 4, 5 y 1 bit respectivamente (total 16 bits).

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 5 de 10

Dos posibles realizaciones de este diseo pueden ser por tanto las siguientes:

Retardo CBA lineal de 4 etapas de 4 bits:

t

setup

+ 4t

carry

+ 3t

mux

+ 3t

carry

+ t

sum

= t

setup

+ 7t

carry

+ 4t

mux

+ t

sum

= 20 + 640 + 440 + 40 ps = 460 ps

Retardo CBA modificado (a):

t

setup

+ t

carry

+ 6t

mux

+ t

sum

= 20 + 40 + 640 + 40 ps = 340 ps

(ganamos 6t

carry

- 3t

mux

en comparacin con el CBA lineal para este caso).

Retardo CBA modificado (b), para el caso especfico de este problema:

t

setup

+ t

carry

+ 5t

mux

+ t

sum

= 20 + 40 + 540 + 40 ps = 300 ps

(ganamos 6t

carry

- 2t

mux

en comparacin con el CBA lineal para este caso).

Observamos que este sumador mejora las prestaciones de un RCA de 16 bits.

e.4) Para obtener un retardo ms pequeo, se puede disear el sumador con una arquitectura segn el principio de

acarreo anticipado (CLA, carry lookahead). Un sumador CLA de 16 bits se puede construir a partir de 4

bloques de sumadores CLA de 4 bits. En este tipo de sumadores se trata de separar los caminos de los

sumadores completos que no implican la propagacin de acarreo de los que contienen este camino.

En la figura siguiente se muestra un bloque de cuatro sumadores parciales (partial full adders, PFA) en los

cuales se incluye la parte del circuito que realiza la suma en la posicin de cada bit (estructura 1), conectado

con el circuito de propagacin de acarreo que corresponde a una estructura RCA de 4 bits (estructura 2) y,

como alternativa, con el circuito de propagacin de acarreo para la arquitectura CLA de 4 bits (estructura 3).

Las entradas a cada PFA son los dos bits A y B de los sumandos y el acarreo de entrada C. Las salidas

corresponden a las seales de propagacin (P) y generacin (G) de acarreo, y el resultado de la suma (S).

Complete el diseo con la estructura interior a nivel de puertas lgicas para cada uno de las estructuras 1. 2, y 3.

Compare cualitativamente el retardo de propagacin de acarreo entre las arquitecturas 2 y 3.

Para este diseo se dispone de las puertas lgicas que haga falta, de hasta 5 entradas (fan in de 5). [15 pts]

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 6 de 10

Retardo de propagacin de acarreo de C

0

a C

4

para el caso de RCA: 24+1 puertas = 9 puertas. Se

implemente segn el esquema:

Retardo de propagacin de acarreo de C

0

a C

4

para el caso de CLA: 2+1 puertas = 3 puertas

C

4

1

2

3

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 7 de 10

(f) Otra de las seis unidades ALU del microprocesador Itanium 2 de la figura P2.1 est encargada de las

operaciones de multiplicacin. Su diagrama de bloques es idntico al diagrama de la figura P2.2, donde

ahora el sumador (+) se sustituye por un multiplicador (). Las entradas Src1 y Src2 ahora son nmeros

positivos de 5 bits.

Para el diseo del multiplicador se disponen de celdas estndar full adder (FA, sumadores completos),

half adder (HA, semi-sumadores) y de celdas de las puertas lgicas que haga falta. Para las celdas de

sumadores (FA y HA), se utilizarn circuitos con retardos t

sum

y t

carry

idnticas a las empleadas en el

apartado anterior (t

sum

t

carry

= 40 ps). El retardo de cualquier puerta lgica de hasta 5 entradas que se

emplea en este diseo es: t

gate

= 20 ps.

f.1) Disee la implementacin del multiplicador utilizando una estructura de sumadores a base del

principio de almacenamiento de acarreo (carry save) con el mayor detalle posible (no hace falta

mostrar las puertas lgicas que generan los productos parciales). [10 pts]

Implementamos la siguiente secuencia de suma de productos parciales para una multiplicacin

binaria de dos nmeros de 4 bits con el algoritmo carry save:

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 8 de 10

Esta solucin propuesta es una versin de carry save "mejorada", dado que en su versin

convencional tiene que contener cinco lneas de sumadores (replicando el layout de un multiplicador

matricial y cambiando la direccin de los acarreos en cada etapa) en vez de cuatro. Ambas

soluciones son correctas en este caso.

f.2) Para cumplir con unas estrictas especificaciones de temporizacin y de coste, se necesita optimizar el

diseo del multiplicador. Reorganice la matriz de productos parciales en forma de rbol y disee una

estructura del multiplicador de dos nmeros de 5 bits en forma de rbol de Wallace. [15 pts]

Re-organizamos la matriz de los productos parciales en forma de rbol:

Seguimos la misma estrategia que se presenta en la figura 11.34 del libro para ir disminuyendo la

profundidad de sumadores en la columna ms poblada (5 productos parciales a sumar en la columna

4) empleando sumadores carry save de tres entradas y dos salidas:

Primera etapa:

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

a

3

b

3

a

2

b

3

a

1

b

3

a

1

b

2

a

1

b

1

a

1

b

0

a

4

b

2

a

3

b

2

a

2

b

2

a

2

b

1

a

2

b

0

a

4

b

1

a

3

b

1

a

3

b

0

a

4

b

0

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

a

3

b

3

a

2

b

3

a

1

b

3

a

1

b

2

a

1

b

1

a

1

b

0

a

4

b

2

s

5

,

0

a

2

b

2

a

2

b

1

a

2

b

0

c

5

,

0

c

4

,

0

s

4

,

0

a

3

b

0

Segunda etapa:

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

a

3

b

3

a

2

b

3

a

1

b

3

a

1

b

2

a

1

b

1

a

1

b

0

a

4

b

2

s

5

,

0

a

2

b

2

a

2

b

1

a

2

b

0

c

5

,

0

c

4

,

0

s

4

,

0

a

3

b

0

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

s

6,0

s

5,1

s

4,1

s

3,0

s

2,0

a

1

b

0

c

6

,

0

c

5

,

1

c

4

,

1

c

3

,

0

c

2

,

0

Tercera etapa:

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

s

6,0

s

5,1

s

4,1

s

3,0

s

2,0

a

1

b

0

c

6

,

0

c

5

,

1

c

4

,

1

c

3

,

0

c

2

,

0

a

4

b

4

s

7,0

s

6,2

s

5,2

s

4,2

s

3,1

a

0

b

2

a

0

b

1

a

0

b

0

c

7

,

0

c

6

,

1

c

5

,

2

c

4

,

2

c

3

,

1

c

2

,

1

s

2,0

a

1

b

0

Cuarta etapa (sumador final):

b

4

b

3

b

2

b

1

b

0

a

4

a

3

a

2

a

1

a

0

a

4

b

4

a

3

b

4

a

2

b

4

a

1

b

4

a

0

b

4

a

0

b

3

a

0

b

2

a

0

b

1

a

0

b

0

a

4

b

3

a

3

b

3

a

2

b

3

a

1

b

3

a

1

b

2

a

1

b

1

a

1

b

0

a

4

b

2

a

3

b

2

a

2

b

2

a

2

b

1

a

2

b

0

+

a

4

b

1

a

3

b

1

a

3

b

0

a

4

b

0

P

9

P

8

P

7

P

6

P

5

P

4

P

3

P

2

P

1

P

0

a

4

b

4

s

7,0

s

6,2

s

5,2

s

4,2

s

3,1

a

0

b

2

a

0

b

1

a

0

b

0

c

7

,

0

c

6

,

1

c

5

,

2

c

4

,

2

c

3

,

1

c

2

,

1

s

2,0

a

1

b

0

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 9 de 10

El circuito con los sumadores completos ser de esta forma:

f.3) Calcule y compare los tiempos de retardo del camino crtico de las dos estructuras de multiplicadores

diseados y compare estos tiempos con el retardo de una estructura de multiplicador matricial para dos

nmeros de 5 bits.

Cmo influye el tamao de palabra de los nmeros de entrada en los tiempos de retardo mximo?

Comente sobre la eficiencia del layout y el coste asociado con cada estructura de multiplicador diseada,

en trminos de rea y de esfuerzo de optimizacin de los caminos crticos. [10 pts]

- Multiplicador en array, de la ecuacin (11.24) del libro de Rabay et al:

t

mult

7t

carry

+ 4t

sum

+ t

and

= 740 + 440 ns + 20 ps = 460 ps

- Multiplicador carry-save, de las ecuaciones (11.4) y (11.25), considerando el sumador final como RCA:

t

mult

4t

carry

+ t

sumafinal

+ t

and

4t

carry

+ (4t

carry

+ t

sum

) + t

and

= 8t

carry

+ t

sum

+ t

and

= 840+40+20 ps= 380 ps

- Implementacin alternativa del multiplicador carry-save propuesta aqu:

t

mult

7t

carry

+ t

sum

+ t

and

= 740 ns + 40 ns + 20 ps = 340 ps.

- Multiplicador en rbol de Wallace, considerando el sumador final como RCA de 5 bits (los tres

primeros bits se pueden sumar a la vez que las sumas de la 1, 2 y 3 etapa respectivamente):

t

mult

3t

sum

+t

sumafinal

+t

and

= 3t

sum

+ (4t

carry

+ t

sum

) + t

and

= 4t

carry

+ 4t

sum

+ t

and

= 440+440+20 ps = 340 ps.

El tiempo mnimo para todas las arquitecturas es el tiempo de propagacin de una puerta AND.

Con la condicin que t

sum

= t

carry

(en este caso t

sum

= t

carry

= 40 ps) observamos que el multiplicador carry-save

puede tener un retardo muy parecido al retardo del multiplicador en rbol para nmeros de pocos bits.

Estas dos arquitecturas mejoran el retardo del multiplicador matricial.

Para multiplicadores de gran tamao, es posible emplear sumadores ms rpidos que los RCA, como

pueden ser los CLA, con un ahorro en tiempo de clculo significativo, al cual se aade el ahorro en

hardware para la estructura en rbol que emplea menos sumadores que las arquitecturas anteriores. En

general, para los multiplicadores matriciales y los carry save, el retardo depende linealmente del

nmero N de bits de las entradas. Para el multiplicador Wallace la dependencia del retardo de

propagacin al nmero de bits es logartmica.

La desventaja del multiplicador Wallace es que su irregular estructura complica la tarea de obtener un

layout eficiente. Por otra parte, el multiplicador carry save tiene una estructura muy regular y facilita

su generacin automtica. Al mismo tiempo, el camino crtico de este multiplicador es ms corto que el

DCSE 2010/11. Grupo 43 5 ejercicio en clase (evaluacin continua)

Pgina 10 de 10

camino crtico del equivalente multiplicador matricial y definido de manera nica, aunque con un coste

ligeramente mayor en trminos de rea ya que necesitamos un sumador adicional. Por otra parte, y en el

caso general que t

sum

t

carry

, para el multiplicador matricial existen mltiples caminos crticos idnticos y

como consecuencia, para acelerar las prestaciones del diseo es necesario optimizar tanto el retardo

t

carry

como el t

sum

.

También podría gustarte

- Formato Ficha RAE-1Documento2 páginasFormato Ficha RAE-1RubenHernando0% (1)

- Credito InformalDocumento13 páginasCredito InformalDemetrio Choqueapaza JimenezAún no hay calificaciones

- Tarea 2 - Doctrinas EconomicasDocumento8 páginasTarea 2 - Doctrinas EconomicasDaniel José MoralesAún no hay calificaciones

- LinealizacionDocumento5 páginasLinealizacionSergio AtahuichiAún no hay calificaciones

- Tarea 1 PresupuestoDocumento14 páginasTarea 1 PresupuestoKevin Andrés VillavicencioAún no hay calificaciones

- Cronograma Sarlaft 1Documento3 páginasCronograma Sarlaft 1Carolain SantanaAún no hay calificaciones

- Mapa Conceptual Redes 1Documento3 páginasMapa Conceptual Redes 1ErikaPlusAún no hay calificaciones

- Planificación Estratégica y Trabajo en Equipo Del Personal Directivo de Las Escuelas Bolivarianas Del Municipio ValeraDocumento99 páginasPlanificación Estratégica y Trabajo en Equipo Del Personal Directivo de Las Escuelas Bolivarianas Del Municipio ValeraHenrry MoralesAún no hay calificaciones

- El Arte Del EstrategaDocumento81 páginasEl Arte Del EstrategaRonald Maluenda100% (1)

- Ejercicio de Vicios de LenguajeDocumento3 páginasEjercicio de Vicios de LenguajeJOAN MAYAún no hay calificaciones

- Eda Vi - Actividad 01Documento2 páginasEda Vi - Actividad 01Deliz UmasiAún no hay calificaciones

- Examen - Ruiz Ramirez AliciaDocumento2 páginasExamen - Ruiz Ramirez AliciapocarutaAún no hay calificaciones

- Silabo Ingeniería de Biorreactores 2018-IDocumento2 páginasSilabo Ingeniería de Biorreactores 2018-IJose Orbegoso LopezAún no hay calificaciones

- LA Cosa Rara 1235Documento2 páginasLA Cosa Rara 1235Catherine RamosAún no hay calificaciones

- La Mercancia Hacker FinalDocumento128 páginasLa Mercancia Hacker FinalguarendickAún no hay calificaciones

- Vojta ConceptoDocumento35 páginasVojta ConceptoBiborka GyepesiAún no hay calificaciones

- Revista Latinoamericana de Politica ComparadaDocumento176 páginasRevista Latinoamericana de Politica ComparadaSeba Gonzalez LopezAún no hay calificaciones

- Tarea Academica 2 Presentacion Da AnDocumento12 páginasTarea Academica 2 Presentacion Da AnAngello YarascaAún no hay calificaciones

- Matriz RiesgosDocumento9 páginasMatriz RiesgosBRANDON QUINTERO TOROAún no hay calificaciones

- Practica Cristalizacion 1Documento12 páginasPractica Cristalizacion 1Fernando GarciaAún no hay calificaciones

- Reglamento General de Triatlon de RoboticaDocumento22 páginasReglamento General de Triatlon de RoboticaMarcelo StéfanoAún no hay calificaciones

- 001 Tarea 1 Principios Del Derecho CivilDocumento17 páginas001 Tarea 1 Principios Del Derecho CivilelsaAún no hay calificaciones

- Como Controlar La Ira PDFDocumento2 páginasComo Controlar La Ira PDFJohnAún no hay calificaciones

- Apunte de Estrategias Intervención Versión Revisada 2014Documento14 páginasApunte de Estrategias Intervención Versión Revisada 2014alvarodiazjoAún no hay calificaciones

- Sistema Numérico Según Los Incas (Semana13-14)Documento9 páginasSistema Numérico Según Los Incas (Semana13-14)AnthonyZamoraAún no hay calificaciones

- Book PreguntasDocumento96 páginasBook Preguntasmaria elizabeth rojas diaz50% (2)

- Tinciones DiferencialesDocumento6 páginasTinciones Diferencialesalvaro acAún no hay calificaciones

- Informe de Rendicion Cuentas CCLDocumento4 páginasInforme de Rendicion Cuentas CCLangelica romeroAún no hay calificaciones

- Actividades para Barbara 8Documento5 páginasActividades para Barbara 8Yeny SojoAún no hay calificaciones

- 1.sociología AmbientalDocumento5 páginas1.sociología AmbientalAlexhander Zuñiga TrilloAún no hay calificaciones