Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Sadgrado 2

Cargado por

Pinto Wallace Adrenaline Bike Wallace PintoTítulo original

Derechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Sadgrado 2

Cargado por

Pinto Wallace Adrenaline Bike Wallace PintoCopyright:

Formatos disponibles

Sistemas de Adquisicin de datos (2)

Clasificacin de los Convertidores DAC

Segn las caractersticas de la seal de entrada digital Codificacin: Cdigo: Signo Binario Natural BCD Positivo Positivo y negativo Valor absoluto y signo Complemento a 1 Complemento a 2 Desplazamiento del cero

Formato:

Serie Paralelo

Almacenamiento Sin latch (cerrojo) Con latch Segn las caractersticas de la seal analgica de referencia Referencia fija Referencia Variable (unipolar o bipolar).

1

Sistemas de Adquisicin de datos (2)

Segn la funcin de transferencia Lineal Logartmica Exponencial Segn el mtodo de conversin Directo Red Lineal Red ponderada Red R-2R Simple Compuesta Suma de corrientes Suma de Tensiones

Indirecto

Multiplicador de relacin de impulsos Convertidor con PCM Mediante muestreo y retencin (S&H) Mediante filtro paso-bajo

Segn la seal obtenida en la salida Tensin Corriente Parmetros importantes de un DAC: Rango de salida, Resolucin (1 LSB), Tiempo de conversin.

2

Sistemas de Adquisicin de datos (2)

Errores que se producen en el funcionamiento de un DAC Error de asimetra, o desplazamiento del cero. Se debe principalmente a la utilizacin de operacionales con error de offset. Se puede corregir ajustando al mnimo el offset del operacional Error de ganancia, o pendiente incorrecta. En los DACs que emplean un operacional y una resistencia de realimentacin para obtener la seal de salida, el problema se suele deber a un valor errneo de dicha resistencia. El valor errneo puede ser debido a utilizar una resistencia con excesiva tolerancia, o a la variacin de su valor por cambios de temperatura y/o envejecimiento de la resistencia. Error de linealidad. En general, se produce por errores en los valores de las resistencias empleadas en el circuito, especialmente en las redes de resistencia. Se deben emplear resistencias con baja tolerancia y poca dependencia con la temperatura. Es el ms difcil de corregir.

3

Sistemas de Adquisicin de datos (2)

Convertidor DAC con multiplexor analgico y red lineal.

Inconvenientes: Gran nmero de resistencias, y multiplexor complejo Ejemplo para 8 bits: 256 resistencias y un MDX con 256 entradas !

n Vref Vo = 2N

N indica el nmero de bits (3 en este ejemplo). n es el valor numrico de entrada (D2 D1 D0).

4

Sistemas de Adquisicin de datos (2)

Potencimetros digitales.

1) Reemplazan a los potencimetros mecnicos en las aplicaciones de ajuste y calibracin. 2) Se basan en el DAC con multiplexor analgico y red lineal. 3) Aaden una interfaz serie (I2C, SPI) y una memoria voltil o no voltil. 4) El valor numrico enviado al potencimetro digital, define la posicin del contacto mvil (wiper). Ver: www.maxim-ic.com www.analog.com

5

www.xicor.com

Sistemas de Adquisicin de datos (2)

Convertidor DAC realizado con conmutadores analgicos y resistencias ponderadas: Este ejemplo tiene 8 bits. En general:

n Vref Vo = N 1 2

N es el nmero de bits n es el valor digital Ejemplo: N=8 Vref= -1 V Con n=0 , Vo= 0 Con n=64 , Vo= 0,5 V Con n=128 , Vo= 1 V Con n=255 , Vo= 1,9921875 V (casi 2 V)

6

Inconvenientes: Resistencias de valores muy dispares.

Sistemas de Adquisicin de datos (2)

Variante del anterior DAC, que no precisa grandes diferencias en los valores de las resistencias: Las tensiones V7 , V6 , V5, V4 , V3 , V2 , V1 , V0 , slo pueden adoptar los valores 0 V.

V7 V6 V5 V4 Itotal = + + + +I R 2 R 4 R 8R

Sistemas de Adquisicin de datos (2)

El circuito se puede dividir en dos bloques: El primer bloque incluye las 4 resistencias R, 2R, 4R y 8R de la parte superior, Rf, y el operacional. El segundo bloque incluye las 4 resistencias R, 2R, 4R y 8R de la parte inferior, y la resistencia 8R desplazada a la derecha. El primer bloque es similar al del DAC estndar con resistencias ponderadas. Por lo tanto, se centra el estudio sobre el segundo bloque. El siguiente esquema facilita el clculo de I.

Sistemas de Adquisicin de datos (2)

La corriente I se puede expresar en funcin de Vx y R (ley de Ohm en la resistencia 8R):

Vx I= 8R

o bien

Vx = 8I R

(expresin 1)

La corriente I tambin se puede expresar como suma de las corrientes parciales:

V3 V x V2 V x V1 V x V0 V x + + + I= R 2R 4R 8R

La expresin anterior se puede mostrar agrupando la dependencia de Vx al final: (bloque A) (bloque B)

I=

V3 V2 V1 V0 Vx Vx Vx Vx + + + R 2 R 4 R 8R R 2 R 4 R 8R

Utilizando la expresin 1, el bloque B queda como:

8I 4 I 2 I I

o simplemente

9

-15I

Sistemas de Adquisicin de datos (2)

Con lo que queda:

(bloque A)

(bloque B)

V3 V2 V1 V0 I= + + + 15I R 2 R 4 R 8R

Agrupando los trminos en I:

V3 V2 V1 V0 16 I = + + + R 2 R 4 R 8R

y despejando I:

V3 V0 V2 V1 I= + + + 16 R 32 R 64 R 128R

que es el resultado del segundo bloque. Completando con el primer bloque:

Itotal =

V7 V6 V5 V4 V V V V + + + + 3 + 2 + 1 + 0 R 2 R 4 R 8R 16 R 32 R 64 R 128R

10

Sistemas de Adquisicin de datos (2)

DAC con red R-2R utilizando el mtodo de suma de tensiones:

El DAC se puede representar de la siguiente forma, donde los generadores Vo, V1, etc. sustituyen a los conmutadores.

11

Sistemas de Adquisicin de datos (2)

El bloque de la izquierda se puede simplificar utilizando Thevenin, quedando como el central. A continuacin se aade la siguiente R en serie:

El proceso sigue as, siguiendo la flecha:

12

Sistemas de Adquisicin de datos (2)

Y sigue...

Se obtiene la expresin de la tensin de salida en funcin de los valores de V0, V1, V2 y V3. Los pesos son los correctos.

13

Sistemas de Adquisicin de datos (2)

DAC con red R-2R en el modo de suma de corrientes:

Vo = n

Vref 2N

14

Sistemas de Adquisicin de datos (2)

Modificacin del DAC anterior, para poderlo utilizar en modo bipolar:

Ejemplo, N=3 y Vref=4V, n va de 0 a 7 n=0, Vo=-4 n=4, Vo= 0 n=7, Vo= +3

Vo1 = n

Vref 2N

tomado de Vo de la pgina anterior

n Vo = Vref 2 Vo1 = Vref N 1 1 2

n = valor digital N= nmero de bits

15

Sistemas de Adquisicin de datos (2)

Modificacin del DAC unipolar anterior para obtener una conversin divisiva:

2 N Vref Vo = n

16

Sistemas de Adquisicin de datos (2)

Convertidor DAC mediante conversin indirecta de frecuencia variable Vref Entrada digital Mux Filtro paso bajo Vo

Generador de impulsos

Divisor programable

El generador de impulsos genera una onda cuadrada de reloj. El divisor programable digitalmente elimina ciertos pulsos del reloj. El filtro paso bajo recibe una cadena de impulsos (incompletos) que se repiten cclicamente. Los impulsos tienen un nivel alto Vref y un nivel bajo de valor cero. La salida del filtro (Vo) es prcticamente un nivel de continua, aunque existe un pequeo rizado. El valor de Vo es proporcional a la entrada digital.

17

Sistemas de Adquisicin de datos (2)

Convertidor DAC mediante conversin indirecta de ancho de impulso variable Vref Entrada digital Contador Mux Comparador Filtro paso bajo Vo

Generador de impulsos El comparador digital activa la entrada Vref mientras el contador no supera a la entrada digital. Cuando el contador supera a la entrada digital, el Mux conmuta al nivel cero. En Vo se obtiene un nivel de continua proporcional a la entrada digital, con un pequeo rizado.

18

Sistemas de Adquisicin de datos (2)

Tabla comparativa de convertidores DAC

Tipo de convertidor

Precisin (LSB)

Velocidad (orientativa) 10 ns 100 ns 1 ms

Resistencias ponderadas Baja R-2R , MUX analgico Mtodos indirectos Alta Media-alta

19

También podría gustarte

- ITIL 4 Examen PDFDocumento7 páginasITIL 4 Examen PDFCrhistian Romero83% (6)

- Modulo Introducción A La InformaticaDocumento31 páginasModulo Introducción A La InformaticaDennis HerediaAún no hay calificaciones

- Trabajo Original de MicrosoftDocumento82 páginasTrabajo Original de MicrosoftmrgianeeAún no hay calificaciones

- Tutorial JTAG para Receptores dm500 y ClonesDocumento5 páginasTutorial JTAG para Receptores dm500 y ClonesMartin Alvarado VieraAún no hay calificaciones

- Silabo SPSSDocumento3 páginasSilabo SPSSJeremy D. Justo NaupayAún no hay calificaciones

- SIMTRAFFIC IntroduccionDocumento5 páginasSIMTRAFFIC Introduccionjonas kunoAún no hay calificaciones

- H Foda FichaDocumento4 páginasH Foda FichaHector Gomez de la Torre Marquina100% (1)

- KarenDocumento14 páginasKarenKaren Mesa ArangoAún no hay calificaciones

- Guia de Aprendizaje Alfabetizacion InformaticaDocumento9 páginasGuia de Aprendizaje Alfabetizacion InformaticaInstructor TicAún no hay calificaciones

- Rúbrica para Evaluar La Ejecución Del Proyecto EducativoDocumento1 páginaRúbrica para Evaluar La Ejecución Del Proyecto EducativoGenser RamirezAún no hay calificaciones

- Practica2 EconometriaDocumento4 páginasPractica2 EconometriaMartin Yupanqui AndradeAún no hay calificaciones

- Calidad ProyectosDocumento4 páginasCalidad ProyectosBederAún no hay calificaciones

- Trabajo Práctico EstadisticaDocumento35 páginasTrabajo Práctico EstadisticaFelipeMlAún no hay calificaciones

- 3.2 Planeacion Estrategica Del Mantenimiento IndustrialDocumento16 páginas3.2 Planeacion Estrategica Del Mantenimiento IndustrialJaqueline Serrata80% (5)

- Taller 1 Comercializacion de Productos TextilesDocumento14 páginasTaller 1 Comercializacion de Productos Textilesedna ramirezAún no hay calificaciones

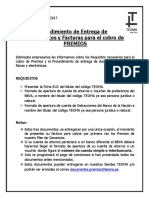

- Procedimiento de Entrega Documentos y FacturasDocumento3 páginasProcedimiento de Entrega Documentos y Facturasjonathan0% (1)

- Instituto Tecnológico de Aguascalientes Proyecto SimulacionDocumento12 páginasInstituto Tecnológico de Aguascalientes Proyecto SimulacionKaren Pérez OlveraAún no hay calificaciones

- 10 Razones Por Que Es Importante La InformáticaDocumento1 página10 Razones Por Que Es Importante La Informáticakiller_jj100% (1)

- Ley μ y Ley ADocumento5 páginasLey μ y Ley AJefferson Alonso Ramos RiveraAún no hay calificaciones

- Operaciones de VecindadDocumento4 páginasOperaciones de VecindadAlfonso AlejandroAún no hay calificaciones

- Estudiante DevOps Essentials Professional Certificate DEPC V092018A PDFDocumento92 páginasEstudiante DevOps Essentials Professional Certificate DEPC V092018A PDFchaconada78% (9)

- El Problema de AsignacionDocumento5 páginasEl Problema de AsignacionAlex Helder HuancaraAún no hay calificaciones

- Experto en Visual Foxpro 9 SP2Documento161 páginasExperto en Visual Foxpro 9 SP2Alex Mauricio Rodriguez LopezAún no hay calificaciones

- Procesamiento de Texto PHPDocumento11 páginasProcesamiento de Texto PHPCrbeXDAún no hay calificaciones

- Marco TeóricoDocumento2 páginasMarco TeóricoRoberto Perdomo100% (1)

- El Juego de La Vida PDFDocumento7 páginasEl Juego de La Vida PDFAlejandroRománAún no hay calificaciones

- Act 1 Mate para TDDocumento10 páginasAct 1 Mate para TDL Lugo0% (1)

- Ejemplos de Patrones de Arquitectura de SoftwareDocumento10 páginasEjemplos de Patrones de Arquitectura de SoftwareOmar Francisco GarcíaAún no hay calificaciones

- CAD Basico Ejercicio 6Documento18 páginasCAD Basico Ejercicio 6Carlos QuispeAún no hay calificaciones