Documentos de Académico

Documentos de Profesional

Documentos de Cultura

Unidad 1 Audio

Cargado por

Marcos Gomez OlivaDerechos de autor

Formatos disponibles

Compartir este documento

Compartir o incrustar documentos

¿Le pareció útil este documento?

¿Este contenido es inapropiado?

Denunciar este documentoCopyright:

Formatos disponibles

Unidad 1 Audio

Cargado por

Marcos Gomez OlivaCopyright:

Formatos disponibles

hardware y software: el sofware se define como el conjunto de instrucciones de programas de computado ra que dirige la operacin del hardware.

un conjunto de instrucciones para una tarea especifica se llama rutina. y el conjunto completo de instrucciones para ejecutar un conjunto de tareas rela cionadas se llama programa. el software se clasifica en: software de base: que controla las operaciones de la computadora en s ( como el s istema operativo y las bios). software de aplicacon o programa de usuario: resuelve problemas para los usuarios . arquitectura basica: unidad de control o uc: resibe las instrucciones del programa, que le indica lo que debe realizar, y reparte las tareas a las demas partes del conjunto. unidad aritmtica y logica: es donde se realizan los procesos de las intrucciones que resibo de la unidad de control. la union de la uc con la alu, forman la sepe, o unidad central de procesos. la memoria: es donde se almacenan y registran los datos y los programas. la memo ria contiene millones de circuitos que reconocen solo dos estados: si pasa o no energia. si pasa corriente, se memorisa un 1, y si no pasa, se memorisa un 0. buses de computadora: un bus es una ruta electrica comun entre multiples dispositivos. el mas comun es el bus de sistema, presente en toda computadora, que contiene entre 50 y 100 al ambres de cobre grabados en una matriz, que contiene conectores para las targeta s de entrada y salida. para que las targetas diceadas por terseras personas pueda n conectarse al bus de sistemas, deben existir especificaciones detalladas sobre el funcionamiento del mismo. que deben ser obedecidas por todos los dispositivo s conectados al bus. esas reglas se denominan protocolo del bus. tambin deben existir especificaciones mecanicas y para que cada targeta pueda a justarse al gabinete de targetas, y para que cada una tenga suficientes conector es para acoplarse a la targeta matriz. algunos dispositivos conectados al bus, se encuentran en estado activo, y pueden realizar transacciones. otros se encuentran en estado pasivo, esperando solicit udes. los activos se llaman maestros, y los pasivos esclavos. si la c p u le ordena a un controlador de disco leer o escribir un bloque, la c p u esta actuando como maestro, y el controlador como esclavo. sin embargo, el c ontrolador puede actuar como maestro, al ordenarle a la memoria que acepte lo qu e est lellendo o escribiendo. pero la memoria nunca puede actuar como maestro. la mayoria de los dispositivos maestros se conectan mediante una pastilla llamad a, manejador de disco, que actua como un amplificador digital. los dispositivos esclavos, lo hacen atraves de un reseptor del bus. los dispositivos que actuan c omo maestros y esclavos, utilizan una pastilla mixta, llamada transmisor-resept or del bus. los aspectos a tener en cuenta al momento de disear un bus son: la sincronizacin d el bus, el mecanismo de arbitraje, el manejo de interrupciones, y el manejo de e rrores. todos ellos afectan la velocidad y la amplitud de la banda del bus. buses sncronos y asncronos: un bus sncrono tiene una lnea manejada por un reloj maestro. la seal de esta linea consiste en una honda cuadrada cuya frecuencia varia entre 5 y 50 mega hertz. to das las actividades del bus se realizan en un numero entero de estos siclos, lla mados siclos del bus. arbitraje del bus: si dos o ms dispositivos conectados al bus quieren actuar como maestros al mismo tiempo, se utiliza un arbitraje del bus. puede ser centralizado o desentralizado

. el centralizado puede decidir cual de los dispositivos tendra acceso al bus. el bus tiene una linea de solicitud que puede ser activada por cualquiera de los di spositivos en cualquier momento. el arbitro no sabe cual de los dispositivos ha enviado la solicitud. solo sabe si hay o no solicitudes. cuando se utiliza el arbitraje desentralizado no existe un arbitro. por ejemplo, si un bus tiene 16 lineas de solicitud, el numero de dispositivos se limita a 1 6. cuando alguno de ellos necesita usar el bus, activa su linea de solicitud. lo s dispositivos monitorean todas las lineas de solicitud, para que al final de ca da ciclo de bus, cada dispositivo sepa si tiene la prioridad mas alta y asi, pod er usar el bus durante el siguiente siclo. este metodo requiere ms lineas de soli citud, pero evita el costo del arbitro encadenamiento margarita: tiene como prioridad que los dispositivos tengan prior idades asignadas dependiendo de que tan cerca se encuentren del arbitro. el disp ositivo mas cercano tiene la prioridad mas alta. cuando el arbitro recibe una solicitud para el bus, autoriza su uso activando la linea de respuesta del bus. dicha linea est conectada en serie atravs de los disp ositivos de entrada y salida. cuando el dispositivo que se encuentra mas cerca del arbitro resibe la seal, veri fica si fue l quien hizo la solicitud, en ese caso utiliza el bus y evita que la seal se siga propagando. si el dispositivo no envi la solicitud, la seal biaja al p roximo dispositivo, donde actua de igual forma y asi asta que algun dispositivo utilize el bus. dispositivos de entrada y salida: la c p u tambin puede competir por el bus, pero tiene la prioridad ms baja y solo puede ocupar el bus cuando nadie ms lo usa. la c p u puede esperar mientras que los dispositivos de entrada y salida deben t ener acceso al bus rapidamente o perderan los datos que estan recibiendo. manejo de interrupciones: cuando la c p u le asigna una tarea a algn dispositivo de entrada y salida, la sea l de interrupcin indica que necesita usar el bus. para evitar que los dispositivo s enven interrupcines al mismo tiempo, se les asignan prioridades, y se utiliza un abitraje centralizado para dar prioridad a aquellos que tengan los tiempos ms cr iticos. en las entradas de solicitud de interrupcin, pueden conectarse hasta 8 pastillas controladoras de entrada y salida de forma diecta. cuando un dispositivo desea r ealizar una interrupcin, activa su linea de interrupcin, la cual maneja la pata de interrupcin de la c p u. en este punto, la pastilla controladora especifica que dispositivo caus la interrupcin, colocando el numero de ste en el bus de datos. la c p u usa ese numero como ndice en una tabla de apuntadores llamados vectores de interrupcon. una ves que el programa ha manejado la interrupcin, escribe una cl ave especial en uno de los registros, lo que proboca que se desactive la seal de interrupcin r, a menos que alla otra solicitud pendiente.

También podría gustarte

- Unidad 1 SoDocumento2 páginasUnidad 1 SoMarcos Gomez OlivaAún no hay calificaciones

- Gestión de Memoria (Armado)Documento6 páginasGestión de Memoria (Armado)Marcos Gomez OlivaAún no hay calificaciones

- Ondas EstacionariasnDocumento2 páginasOndas EstacionariasnMarcos Gomez OlivaAún no hay calificaciones

- Unidad 1 SoDocumento2 páginasUnidad 1 SoMarcos Gomez OlivaAún no hay calificaciones

- Informatica 2 - Manual - de - Catedra Unidad 3 (Para El Final)Documento7 páginasInformatica 2 - Manual - de - Catedra Unidad 3 (Para El Final)Marcos Gomez OlivaAún no hay calificaciones

- Maquina Virtual y FuncionesDocumento1 páginaMaquina Virtual y FuncionesMarcos Gomez OlivaAún no hay calificaciones

- Campos de EnergiaDocumento4 páginasCampos de EnergiaMarcos Gomez OlivaAún no hay calificaciones

- Los DiscosDocumento3 páginasLos DiscosMarcos Gomez OlivaAún no hay calificaciones

- Campos de EnergiaDocumento4 páginasCampos de EnergiaMarcos Gomez OlivaAún no hay calificaciones

- Un Manual para La Ascension - Primera Parte - El TiempoDocumento3 páginasUn Manual para La Ascension - Primera Parte - El TiempoMarcos Gomez OlivaAún no hay calificaciones

- Yoga Autorrealizacion y Cambio SocialDocumento3 páginasYoga Autorrealizacion y Cambio SocialMarcos Gomez OlivaAún no hay calificaciones

- Unidad 6 ControlDocumento2 páginasUnidad 6 ControlMarcos Gomez Oliva100% (1)

- Capitulo2 IS11Documento19 páginasCapitulo2 IS11rammsterAún no hay calificaciones

- SO - ProcesosDocumento30 páginasSO - ProcesosAntonio AndradaAún no hay calificaciones

- Usuario YoutubeDocumento1 páginaUsuario YoutubeMarcos Gomez OlivaAún no hay calificaciones

- Hologram ADocumento3 páginasHologram AMarcos Gomez OlivaAún no hay calificaciones

- Capitulo2 IS11Documento19 páginasCapitulo2 IS11rammsterAún no hay calificaciones

- Los LenguajesDocumento3 páginasLos LenguajesMarcos Gomez OlivaAún no hay calificaciones

- Unidad 3Documento3 páginasUnidad 3Marcos Gomez OlivaAún no hay calificaciones

- El Mayor Misterio Del MundoDocumento1 páginaEl Mayor Misterio Del MundoMarcos Gomez OlivaAún no hay calificaciones

- Gayatri MantraDocumento1 páginaGayatri MantraMarcos Gomez OlivaAún no hay calificaciones

- Usuario YoutubeDocumento1 páginaUsuario YoutubeMarcos Gomez OlivaAún no hay calificaciones

- Unidad 4Documento5 páginasUnidad 4Marcos Gomez OlivaAún no hay calificaciones

- Trucos Gta Sa Ps2Documento5 páginasTrucos Gta Sa Ps2Marcos Gomez OlivaAún no hay calificaciones

- Todos Los Capitulos de SpownDocumento1 páginaTodos Los Capitulos de SpownMarcos Gomez OlivaAún no hay calificaciones

- Calendario Academico 2013Documento2 páginasCalendario Academico 2013Marcelo NievaAún no hay calificaciones

- Unidad 5Documento2 páginasUnidad 5Marcos Gomez OlivaAún no hay calificaciones

- Introducción A La TelefoníaDocumento14 páginasIntroducción A La TelefoníaAngel EstradaAún no hay calificaciones

- Tutorial de PremierDocumento53 páginasTutorial de PremierOmar ZamudioAún no hay calificaciones

- Portafolio Mesa de AyudaDocumento8 páginasPortafolio Mesa de AyudaJaunDelgasAún no hay calificaciones

- Ccna4 Cap3 ExamenDocumento13 páginasCcna4 Cap3 ExamenjoschicoAún no hay calificaciones

- FOTOCOPIADORADocumento2 páginasFOTOCOPIADORAGiselaAún no hay calificaciones

- Diario El ComercioDocumento38 páginasDiario El Comerciompacheco_570702Aún no hay calificaciones

- Comunicacion InalambricaDocumento17 páginasComunicacion InalambricaMario René Chagala OrtizAún no hay calificaciones

- La FlexografíaDocumento4 páginasLa FlexografíaClaudia BermudezAún no hay calificaciones

- Alineacion 2Documento1 páginaAlineacion 2Imagina TuWebAún no hay calificaciones

- Hoja de Vida DRGDocumento3 páginasHoja de Vida DRGdanielAún no hay calificaciones

- Catálogo de Servicios COMPUCENTRODocumento11 páginasCatálogo de Servicios COMPUCENTROJoseAún no hay calificaciones

- Sensor de ImagenDocumento2 páginasSensor de ImagenWalther EstevezAún no hay calificaciones

- Componentes Internos Del ComputadorDocumento9 páginasComponentes Internos Del Computadorcarla riveroAún no hay calificaciones

- Traktor Kontrol S4 MK2 Manual EspañolDocumento251 páginasTraktor Kontrol S4 MK2 Manual EspañolWaldir Urbina EscobarAún no hay calificaciones

- Radio Definido Por SoftwareDocumento2 páginasRadio Definido Por SoftwareYunior DagaAún no hay calificaciones

- Guia #2733Documento1 páginaGuia #2733Jorge Vesga Z0% (1)

- Usuario Basic PrintDocumento54 páginasUsuario Basic PrintLuis Lucas67% (3)

- Dispositivos de Entrada y Salida PDFDocumento8 páginasDispositivos de Entrada y Salida PDFEDISSON SOLARTEAún no hay calificaciones

- Lista de Precios 28-02 Con StockDocumento125 páginasLista de Precios 28-02 Con StockOliva, Diego MartínAún no hay calificaciones

- Semana 3 Estructura Del ComputadorDocumento13 páginasSemana 3 Estructura Del ComputadorRoni AguilarAún no hay calificaciones

- 5.0.1.2 Class Activity - Join My Social CircleDocumento3 páginas5.0.1.2 Class Activity - Join My Social CircleFelix PerezAún no hay calificaciones

- Arquitectura de La Red Internet de Banda AnchaDocumento5 páginasArquitectura de La Red Internet de Banda AnchaCerberus MaxAún no hay calificaciones

- Manual de Operación de Soporte TecnicoDocumento26 páginasManual de Operación de Soporte TecnicoJohn Kevin BarreraAún no hay calificaciones

- EndiannessDocumento3 páginasEndiannessFrancisco RamosAún no hay calificaciones

- Desarrollo Taller Nº2 SistemasDocumento9 páginasDesarrollo Taller Nº2 Sistemasplayero40 valencia morenoAún no hay calificaciones

- Resumen CCNA4Documento20 páginasResumen CCNA4Cristian GarcíaAún no hay calificaciones

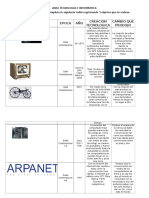

- Tabla Objetos TecnologiaDocumento2 páginasTabla Objetos TecnologiaCMD TutorialesAún no hay calificaciones

- Qué Es El Internet, Relación y Diferencias de HTTP y HTML 1Documento3 páginasQué Es El Internet, Relación y Diferencias de HTTP y HTML 1Edgar Fabian Traba CamaraAún no hay calificaciones

- Análisis de TráficoDocumento25 páginasAnálisis de TráficoJulian David Yepes CarreñoAún no hay calificaciones

- Tecnologia 3GDocumento23 páginasTecnologia 3GRonald GonzaloAún no hay calificaciones